前言

現(xiàn)場(chǎng)可編程門陣列(FPGA)是近幾年來(lái)出現(xiàn)并被廣泛應(yīng)用的大規(guī)模集成電路器件,它的特點(diǎn)是直接面向用戶,具有極大的靈活性和通用性使用方便,硬件測(cè)試和實(shí)現(xiàn)快捷,開發(fā)效率高,成本低,上市時(shí)間短,技術(shù)維護(hù)簡(jiǎn)單,工作可靠性好等。

硬件描述語(yǔ)言(VHDL)是用來(lái)描述硬件電路的功能,信號(hào)連接關(guān)系及時(shí)序關(guān)系的高級(jí)硬件編程語(yǔ)言,設(shè)計(jì)者可根據(jù)VHDL語(yǔ)言法則,對(duì)系統(tǒng)的邏輯進(jìn)行行為描述,然后通過綜合工具進(jìn)行電路結(jié)構(gòu)的綜合、編譯、優(yōu)化,用仿真工具進(jìn)行邏輯功能仿真和系統(tǒng)時(shí)序仿真,可在短時(shí)間內(nèi)設(shè)計(jì)出高效、穩(wěn)定、符合設(shè)計(jì)要求的大規(guī)模或超大規(guī)模的集成電路。

該處理器采用了TOP—DOWN的層次網(wǎng)絡(luò)模塊化設(shè)計(jì)方法,用VHDL描述了嵌入式PLC的CPU的主要邏輯功能,考慮到嵌入式CPU結(jié)構(gòu)的復(fù)雜性和設(shè)計(jì)的可擴(kuò)展性,在頂層設(shè)計(jì)中采用了原理圖的方法,通過VHDL對(duì)每個(gè)單元模塊進(jìn)行了仿真和綜合,然后將綜合生成的各個(gè)模塊連接起來(lái),組成了一個(gè)整體

1 系統(tǒng)設(shè)計(jì)

1.1 系統(tǒng)的功能

該P(yáng)LC主要是用來(lái)與DSP共同實(shí)現(xiàn)數(shù)控機(jī)床中的部分操作,它主要執(zhí)行一些輔助的邏輯控制。它的主要任務(wù)如下:

(1)接收從DSP發(fā)送過來(lái)的指令字,并將其進(jìn)行譯碼轉(zhuǎn)換成相應(yīng)的命令信號(hào),從而執(zhí)行相應(yīng)的操作;(2)接收操作面板上的按鍵信號(hào),并響應(yīng)相應(yīng)的操作;(3)給DSP發(fā)送應(yīng)答信號(hào)以及狀態(tài)信息;(4)將處理的結(jié)果輸出到面板上以驅(qū)動(dòng)相應(yīng)的繼電器。

1.2 系統(tǒng)的組成部分

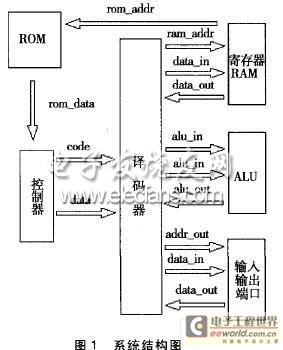

該系統(tǒng)的核心組成部分是由控制器、運(yùn)算器以及I/0端口構(gòu)成,如圖1所示。

控制器:控制器是由程序計(jì)數(shù)器、指令寄存器、指令譯碼器、時(shí)序產(chǎn)生器和操作控制器等組成,它是發(fā)布命令的“決策機(jī)構(gòu)”。運(yùn)算器:運(yùn)算器由算術(shù)邏輯單元、暫存器以及數(shù)據(jù)緩沖器等組成,它是數(shù)據(jù)的加工處理部件。

I/0端口該P(yáng)LC的I/O點(diǎn)數(shù)為l0點(diǎn)輸入和8點(diǎn)輸出。每個(gè)端口由輸入寄存器以及相應(yīng)的端口控制部分組成。

2 系統(tǒng)的FPGA實(shí)現(xiàn)

2.1 控制器

控制器的形式主要有組合邏輯控制器和微程序控制器兩種,與組合邏輯控制器相比較,微程序控制器具有規(guī)整性、靈活性、可維護(hù)性等一系列優(yōu)點(diǎn) ,在計(jì)算機(jī)的設(shè)計(jì)中使用比較普遍,本控制器的設(shè)計(jì)采用的也是微程序控制器。微程序控制的基本思想,就是仿照通常的解題程序的方法,把操作控制信號(hào)編成所謂的“微指令”,存放到一個(gè)只讀存儲(chǔ)器里。當(dāng)機(jī)器運(yùn)行時(shí),一條又一條地讀出這些微指令,從而產(chǎn)生全機(jī)所需要的各種操作控制信號(hào),使相應(yīng)部件執(zhí)行所規(guī)定的操作 。

微程序控制器主要由控制存儲(chǔ)器(CM),微地址產(chǎn)生邏輯,微地址寄存器(uAR),微指令寄存器(ulR)等組成。

(1)機(jī)器指令與微程序。該處理器選取了PLC指令系統(tǒng)中的十條基本指令如表1所示,指令采用十位二進(jìn)制編碼格式。

第9~6位是四位指令的操作碼字段;第5位是標(biāo)志位,用來(lái)判斷該指令有無(wú)操作數(shù)(1一有操作數(shù),0一無(wú)操作數(shù));第4~0位是操作數(shù)字段。

表中每條機(jī)器指令對(duì)應(yīng)一段微程序,一段微程序包含若干條微指令,微程序的設(shè)計(jì)就具體地可落實(shí)到微指令的設(shè)計(jì) ,微指令中的控制字段作為控制命令控制計(jì)算機(jī)的操作,控制字段給出的微命令應(yīng)包含計(jì)算機(jī)操作的所有微命令,對(duì)微命令給出和表示的方法與所采用的編碼方式有關(guān),常用的微命令表示方法有直接表示法、編碼表示法、和混合表示法,該設(shè)計(jì)采用的是將直接表示法和編碼表示法混合使用的混合表示法。

該系統(tǒng)中的每條微指令為32位,其中低5位為下地址字段,直接送給微地址寄存器,第5~7位為測(cè)試字段,送到微地址產(chǎn)生邏輯電路里面以控制微地址的產(chǎn)生,其余位為用來(lái)產(chǎn)生各種微命令的控制字段。

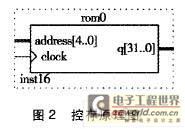

(2)控制存儲(chǔ)器。控制存儲(chǔ)器中存放的是各指令所對(duì)應(yīng)的微程序,它可以用FPGA中的LPM—ROM模塊來(lái)實(shí)現(xiàn),如圖2所示。Clock為同步時(shí)鐘信號(hào),address為5位的地址值,q為32位的微指令,當(dāng)clock上升沿到來(lái)時(shí),rom就把a(bǔ)ddress所對(duì)應(yīng)的地址中的值輸出給q。

(3)微地址產(chǎn)生邏輯。微地址產(chǎn)生邏輯主要是根據(jù)微指令中的測(cè)試位及其他相關(guān)的條件來(lái)控制微地址的產(chǎn)生,它是根據(jù)一定的邏輯功能用VHDL語(yǔ)言編寫的,并且經(jīng)過編譯和綜合后生成的模塊,如圖3所示。

其中,clk為同步時(shí)鐘信號(hào),rst為復(fù)位信號(hào),q為輸出的5位微地址值。其控制流程如下:

(1)系統(tǒng)啟動(dòng)時(shí),給出一個(gè)rst=1的復(fù)位信號(hào),q端便輸出“00010”,為輸入掃描微程序的入口地址;(2)對(duì)應(yīng)的微指令就從控存中輸出,然后該微指令中的5位下地址字段直接輸入到din端,3位測(cè)試位輸入到m端;(3)如果m=“000”,則q端輸出的地址值直接加1,且返回(2)繼續(xù)執(zhí)行;否則,執(zhí)行下一步;(4)如果m=“001”,則看i端輸入的用戶程序指令來(lái)判斷是否需要取數(shù)操作,如果需要,則q端輸出各個(gè)取數(shù)微程序的入口地址;如果不需要,則q端根據(jù)i的操作碼輸出相應(yīng)指令的微程序入口地址,且返回(2)繼續(xù)執(zhí)行;否則,執(zhí)行下一步;(5)如果m=“010”,q端直接輸出din的地址值,且返回(2)繼續(xù)執(zhí)行;否則,執(zhí)行下一步;(6)如果m=“011”,則q端根據(jù)i的操作碼輸出相應(yīng)指令的微程序人口地址,且返回(2)繼續(xù)執(zhí)行。

2.2 運(yùn)算器

運(yùn)算器是用來(lái)對(duì)輸入的數(shù)據(jù)進(jìn)行算術(shù)和邏輯運(yùn)算的部件 ,該ALU具有三輸入和兩輸出,d1和d2是參與邏輯運(yùn)算的兩個(gè)位數(shù)據(jù),其中dl來(lái)自外部的取數(shù),d2來(lái)自輸出暫存器s,sel是指令的操作碼。result是運(yùn)算后的結(jié)果,輸出后送給了暫存器S,q用來(lái)啟動(dòng)定時(shí)器,如圖4所示。

2 3 RAM 圖4 運(yùn)算器原理圖

RAM用來(lái)存儲(chǔ)用戶程序,它可以用FPGA中的LPM—RAM—DQ模塊來(lái)實(shí)現(xiàn)。其中,wren是讀寫控制端,當(dāng)wren=0時(shí)為讀允許,這時(shí)在同步時(shí)鐘clock的上升到來(lái)時(shí)沿將address所對(duì)應(yīng)的地址中的內(nèi)容給輸出端q;當(dāng)wren=1時(shí)為寫允許,這時(shí)在同步時(shí)鐘clock的上升沿到來(lái)時(shí)將data端的數(shù)據(jù)寫入到address所指明的地址中,如圖5所示。

3 仿真與分析

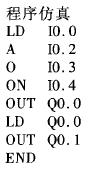

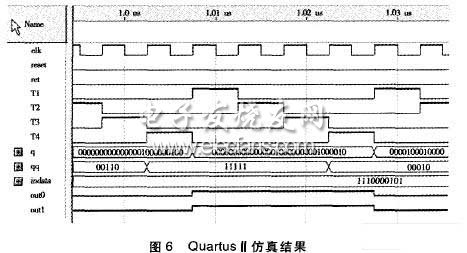

為了測(cè)試指令的運(yùn)行情況,本文在最后給出了一段基于Quartus II的程序仿真。

仿真時(shí)給出了10位輸入數(shù)據(jù)indata=”1 1 10000101”,10.0~10.4分別對(duì)應(yīng)著該數(shù)據(jù)的第0位~第4位,同樣QO.o和Qo.1分別對(duì)應(yīng)著輸出端子的第。位和第1位。

仿真結(jié)果的圖6中:T1,T2,T3,T4為4個(gè)時(shí)鐘節(jié)拍信號(hào),out0和out1分別對(duì)應(yīng)著輸出端子Qo.o和Qo.1,因?yàn)镮O.o和IO.2為1,IO.3和IO.4都為o,因此程序運(yùn)行的最后結(jié)果應(yīng)該是QO.o和Q0.1都為1,并且從圖6可以看出,仿真結(jié)果與此相同,程序運(yùn)行正確,說(shuō)明所設(shè)計(jì)的微處理器及其指令正確可靠。

4 結(jié)束語(yǔ)

本文所設(shè)計(jì)的PLC微處理器具有很強(qiáng)的可修改性和可移植性,并且優(yōu)化升級(jí)也很方便,可以根據(jù)特定的需要方便地增刪指令和I/O端口的數(shù)量,這比傳統(tǒng)的PLC具有更大的靈活性。另外,由于FPGA具有很高的密度,能夠集成很大的系統(tǒng) ,因而極大地提高了系統(tǒng)的可靠性。