開啟新的FPGA設(shè)計是一趟令人興奮而又充滿挑戰(zhàn)的旅程,對于初學(xué)者來說尤其如此。FPGA世界為創(chuàng)建復(fù)雜、高性能的數(shù)字系統(tǒng)提供了巨大的潛力,但同時也需要對各種設(shè)計原理和工具有扎實的了解。無論您是設(shè)計新手還是經(jīng)驗豐富的FPGA專家,有時你會發(fā)現(xiàn)可能會遇到一些不熟悉的情況,包括理解時序約束到管理多個時鐘域,或者需要去了解最新的器件和軟件功能。

在本文中,我們將分享一些有用的技巧,幫助您快速開始設(shè)計,避免常見的設(shè)計陷阱。通過掌握這些關(guān)鍵技巧,可以確保您在開發(fā)工業(yè)設(shè)備、醫(yī)療設(shè)備、智能家居設(shè)備、自動駕駛汽車和機器人應(yīng)用時,更順利、更高效的進(jìn)行設(shè)計流程,最終成功實現(xiàn)FPGA設(shè)計。現(xiàn)在讓我們來深入了解這些基本技巧,并探討如何利用它們來提高FPGA設(shè)計和相關(guān)技能。

1. 掌握時序約束

時序約束對于指導(dǎo)布局和布線過程至關(guān)重要。它們可用于優(yōu)先處理某些物理設(shè)計,如時序、功耗和面積使用。在實施以太網(wǎng)、PCIe或USB等通信協(xié)議以及電機控制和工業(yè)自動化應(yīng)用等控制系統(tǒng)時,時序約束至關(guān)重要。通過設(shè)置精確的時序約束,可以確保復(fù)雜的RTL設(shè)計滿足I/O輸入輸出的物理和接口要求。

時序約束不僅要滿足設(shè)計的即時要求,還要確保長期的可靠性和性能。通過設(shè)置精確的時序約束,您可以避免出現(xiàn)設(shè)置和保持時間違例等問題,這些問題可能會導(dǎo)致系統(tǒng)出現(xiàn)不可預(yù)測的行為。此外,了解時鐘偏移和抖動對設(shè)計的影響有助于創(chuàng)建更穩(wěn)健的時序約束。同樣重要的是,隨著設(shè)計的進(jìn)展,定期檢查和更新時序約束,確保其在整個設(shè)計過程中保持相關(guān)性和有效性。

萊迪思在Lattice Insights 上提供全面的培訓(xùn)課程,幫助設(shè)計人員有效地理解和實施時序約束,您可以點擊觀看萊迪思開發(fā)者大會上關(guān)于FPGA時序約束和時序收斂深度剖析的演講。

2. 監(jiān)測資源利用情況

隨著設(shè)計的推進(jìn),必須密切關(guān)注資源利用率,以避免線路擁塞并確保時序收斂。忽略資源數(shù)量會導(dǎo)致設(shè)計效率低下,消耗不必要的功率和面積。通過在整個設(shè)計過程中監(jiān)控資源利用率,您可以就優(yōu)化設(shè)計的性能、功耗和面積做出明智的決策。

此外,還要確保您選擇的FPGA產(chǎn)品系列可以輕松實現(xiàn)密度拓展。萊迪思為大多數(shù)產(chǎn)品系列的各種密度器件提供引腳到引腳的封裝遷移路徑。萊迪思Nexus? 和萊迪思Avant? 系列提供三種速度等級,可在萊迪思Radiant? 設(shè)計軟件中進(jìn)行模擬,幫助設(shè)計人員選擇最合適的器件來實現(xiàn)時序收斂和裕度。

這可以幫助您避免代價高昂的重新設(shè)計,并確保您的FPGA在系統(tǒng)和IP層面都能滿足所需的規(guī)格要求。此外,了解不同資源類型(如邏輯元件、存儲模塊和DSP slice)之間的權(quán)衡,可以幫助您做出更好的設(shè)計選擇,帶來更均衡、更高效的實現(xiàn)。

3. 高效的時鐘域管理

管理多個時鐘域很有挑戰(zhàn)性,但對于確保數(shù)據(jù)完整性和可靠運行至關(guān)重要。通過采用適當(dāng)?shù)耐郊夹g(shù),可以最大限度地降低不穩(wěn)定性和數(shù)據(jù)損壞的風(fēng)險。此外,了解時鐘域交叉對設(shè)計時序和性能的影響有助于創(chuàng)建更高效、更可靠的系統(tǒng)。

確保利用同步電路、雙時鐘或異步FIFO來處理跨域時鐘。萊迪思Radiant? 設(shè)計軟件提供深入的靜態(tài)和動態(tài)時序分析,使設(shè)計人員能夠有效地識別和管理多個時鐘域。

4. 全面的仿真和測試

正確的設(shè)計仿真需要為IP和/或被測器件(DUT)提供強大的功能仿真模型和測試平臺。萊迪思Radiant? 設(shè)計軟件包括Siemens QuestaSim和器件庫/模型,幫助FPGA設(shè)計人員為萊迪思器件的復(fù)雜設(shè)計和IP無縫開發(fā)仿真。我們的IP庫和參考設(shè)計包括示例測試平臺和仿真模式,可進(jìn)行定制并集成到更大的設(shè)計中。此外,使用Reveal Analyzer等工具可以幫助您深入了解設(shè)計的行為和性能。

仿真和測試是FPGA設(shè)計過程中的關(guān)鍵步驟。通過充分仿真您的設(shè)計,您可以在硬件出現(xiàn)問題之前發(fā)現(xiàn)并加以解決。

5. 管理功耗

功耗是FPGA設(shè)計中的一個重要考慮因素。隨著結(jié)溫的升高,漏電流和靜態(tài)功耗也會上升。萊迪思Radiant功率估算器可幫助設(shè)計人員建立熱性能模型,并估算各種器件開關(guān)狀態(tài)下的功耗,從而創(chuàng)建適當(dāng)?shù)纳峤鉀Q方案和合適的功率樹。該工具基于真實的芯片性能數(shù)據(jù),提供精確的、數(shù)據(jù)驅(qū)動的圖形化功耗計算和估算表。

功耗在FPGA設(shè)計中至關(guān)重要,尤其是對功耗和熱要求嚴(yán)格的應(yīng)用。通過準(zhǔn)確估算和管理功耗,您可以確保FPGA在安全的熱限制范圍內(nèi)運行,并滿足最終產(chǎn)品所需的性能規(guī)格。

利用正確的工具和資源可以使您的設(shè)計目標(biāo)得以快速實現(xiàn),萊迪思提供了一套全面的產(chǎn)品、軟件、工具和支持,以加速和增強您的FPGA開發(fā)。

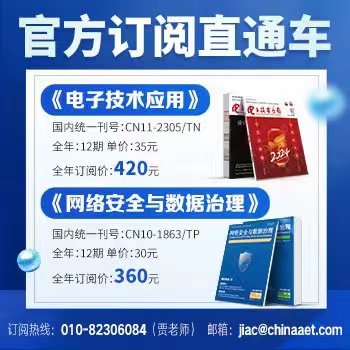

更多精彩內(nèi)容歡迎點擊==>>電子技術(shù)應(yīng)用-AET<<