摘要:由于FPGA具有速度快,效率高,靈活穩(wěn)定,集成度高等優(yōu)點(diǎn),所以為了提高串口通信的速度和效率,在串行通信中采用FPGA來實(shí)現(xiàn)串口通信是十分必要的。由于通信傳輸?shù)牟淮_定性以及干擾等原因,串行通信經(jīng)常會(huì)出現(xiàn)異常情況。然而,在串行通信中添加CRC校驗(yàn),可以提高通信的可靠性。采用Verilog HDL設(shè)計(jì)的一個(gè)帶CRC校驗(yàn)的串口通信程序,對(duì)其下栽到FPGA芯片中進(jìn)行實(shí)驗(yàn)驗(yàn)證,得到的結(jié)論是用FPGA進(jìn)行串口通信,可大大提高通信的速度和效率,且CRC校驗(yàn)確保了通信的準(zhǔn)確性及卡可靠性。

關(guān)鍵詞:Verilog HDL;串口通信;FPGA;CRC檢驗(yàn)

現(xiàn)場可編程門陣列(field programmable gate array,F(xiàn)PGA)在數(shù)字電路設(shè)計(jì)中已經(jīng)被廣泛使用。這種設(shè)計(jì)方式可以將以前需要多塊集成芯片的電路設(shè)計(jì)到一塊大模塊可編程邏輯器件中,大大減少了電路板的尺寸,增強(qiáng)了系統(tǒng)的可靠性和設(shè)計(jì)的靈活性。本文詳細(xì)介紹了已在實(shí)際項(xiàng)目中應(yīng)用的基于FPGA的串口通信設(shè)計(jì)。硬件描述語言(hardware description language,HDL)是一種用形式化方法來描述數(shù)字電路和設(shè)計(jì)數(shù)字邏輯系統(tǒng)的語言。數(shù)字邏輯電路設(shè)計(jì)者可以利用這種語言來描述自己的設(shè)計(jì)思想,然后利用電子設(shè)計(jì)自化(EDA)工具進(jìn)行仿真,再自動(dòng)綜合到門級(jí)電路,然后用ASIC或Soft-Core實(shí)現(xiàn)其功能。Verilog HDL是硬件描述語言的一種,用于數(shù)字電子系統(tǒng)設(shè)計(jì)。串口通信是指在一個(gè)時(shí)間內(nèi)傳輸1位數(shù)字?jǐn)?shù)據(jù)。從19世紀(jì)的二進(jìn)位電報(bào)編碼,發(fā)展到現(xiàn)在的RS 232(EIA 232),主要用于連接終端和大型主機(jī)。串口通信在過去的40年里,大大推動(dòng)了通信技術(shù)的發(fā)展。通信協(xié)議是指通信雙方的一種約定。約定包括對(duì)數(shù)據(jù)格式、同步方式、傳送速度、傳送步驟、檢糾錯(cuò)方式以及控制字符定義等問題做出統(tǒng)一規(guī)定,通信雙方必須共同遵守。因此,也叫通信控制規(guī)程,或稱傳輸控制規(guī)程,它屬于 ISO’sOSI七層

參考模型中的數(shù)據(jù)鏈路層,其主要完成的作用如下:

(1)實(shí)現(xiàn)數(shù)據(jù)格式化;

(2)進(jìn)行串/并轉(zhuǎn)換;

(3)控制數(shù)據(jù)傳輸速率;

(4)進(jìn)行錯(cuò)誤檢測;

(5)進(jìn)行TTL與EIA電平轉(zhuǎn)換;

(6)提供EIA-RS 232C接口標(biāo)準(zhǔn)所要求的信號(hào)線;

(7)為了完成上述串行接口的任務(wù),串行通信接口電路一般由可編程的串行接口芯片、波特率發(fā)生器、EIA與TTL電平轉(zhuǎn)換器以及地址譯碼電路組成。

1 方案設(shè)計(jì)與分析

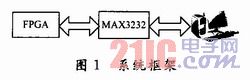

1.1 硬件電路

該方案的硬件電路設(shè)計(jì)包括:FPGA芯片、MAX3232,DB9。其硬件電路與微機(jī)通信的結(jié)構(gòu)框圖如圖1所示。

1.2 軟件設(shè)計(jì)思想

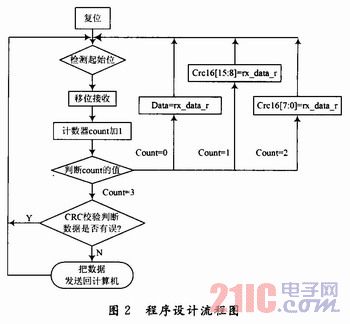

軟件部分的設(shè)計(jì)流程如圖2所示。

1.2.1 波特率設(shè)置

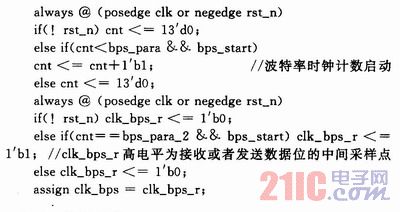

系統(tǒng)時(shí)鐘是由PFGA的16引腳輸入的24 MHz時(shí)鐘,而異步串口通信的波特率設(shè)置為9 600 b/s,所以需要對(duì)主頻進(jìn)行分頻。分頻過程定義了2個(gè)常量,分別用來存儲(chǔ)波特率96 000 b/s的分頻計(jì)數(shù)最大值bpspara和分頻計(jì)數(shù)的一半bps_para_2。每個(gè)系統(tǒng)時(shí)鐘的上升沿來臨時(shí)計(jì)數(shù)器cnt加1,每bps_para_2個(gè)系統(tǒng)時(shí)鐘周期clk_bps改變1次狀態(tài),這樣就產(chǎn)生了96 000 b/s的波特率。部分分頻代碼如下:

1.2.2 數(shù)據(jù)接收

數(shù)據(jù)接收模塊所要完成的任務(wù)包括:

(1)連續(xù)接收3個(gè)字節(jié):1個(gè)字節(jié)的數(shù)據(jù)信息和2個(gè)字節(jié)的數(shù)據(jù)信息的CRC校驗(yàn)碼;

(2)取出這3個(gè)字節(jié)的第一個(gè)字節(jié),重新生成CRC碼;

(3)講新生成的CRC碼與接收到得CRC比較,若相同則傳輸過程中沒有出現(xiàn)錯(cuò)誤;若不相同則傳輸過程有錯(cuò)誤,等待接收下一組數(shù)據(jù)。

①單字節(jié)串/并轉(zhuǎn)換

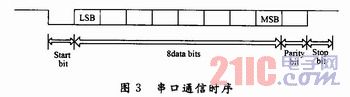

串口通信發(fā)送數(shù)據(jù)的格式:1位起始位(低),8位數(shù)據(jù)位,1位停止位(高),共10位(這里沒有校驗(yàn)位ParityBit)傳輸時(shí)的順序是:起始位+數(shù)據(jù)位低位---數(shù)據(jù)位高位+停止位,其時(shí)序圖如圖3所示;

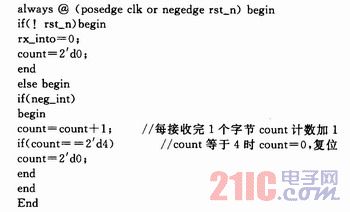

②3字節(jié)連續(xù)接收并儲(chǔ)存

為了連續(xù)接收3個(gè)字節(jié)數(shù)據(jù),定義中斷寄存器neg_int和計(jì)數(shù)器count,復(fù)位時(shí)都清零,開始接收數(shù)據(jù)時(shí)rx_int置高,每接受完1個(gè)字節(jié),rx_int清零,此時(shí)檢測rx_int的下降沿,下降沿到來時(shí)計(jì)數(shù)器count加1,直到接收完第3個(gè)字節(jié)時(shí)count的值是3。部分程序如下:

因?yàn)镠DL是硬件描述語言,所以必須時(shí)刻檢測是否有起始位到來,需用幾個(gè)并行的always語句塊來處理。在接受完第1個(gè)字節(jié)后繼續(xù)檢測下降沿,并把接收到的數(shù)據(jù)暫存到寄存器data中,接收完第2個(gè)字節(jié)后仍繼續(xù)檢測下降沿,并暫存數(shù)據(jù)到crc16[15:8],接收完第3個(gè)字節(jié)繼續(xù)檢測下降沿,暫存數(shù)據(jù)到crc16[7:O]。等待下面的校驗(yàn)處理。下面用case語句塊來暫存數(shù)據(jù)。

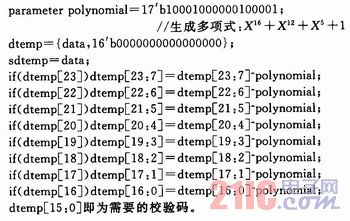

③CRC碼生成

循環(huán)冗余校驗(yàn)(cyclic redundancy check,CRC)是一種在數(shù)據(jù)傳輸中廣泛應(yīng)用的差錯(cuò)檢測方法。CRC的設(shè)計(jì)思想是將數(shù)據(jù)包當(dāng)作一個(gè)多位的二進(jìn)制數(shù),用這個(gè)二進(jìn)制數(shù)除以一個(gè)選定的多項(xiàng)式,所得的余數(shù)作為校驗(yàn)數(shù)據(jù)直接附加在數(shù)據(jù)后面發(fā)送出去,在接收端對(duì)數(shù)據(jù)除以相同的多項(xiàng)式如余數(shù)為零則表示沒有錯(cuò)誤被檢測到。CRC的工作過程如下:假設(shè)需要發(fā)送的數(shù)據(jù)為8位,校驗(yàn)多項(xiàng)式一般為X16+X12+X5+1。首先將發(fā)

送數(shù)據(jù)左移16位生成一個(gè)新的數(shù)列,然后采用模2運(yùn)算(異或)將新數(shù)列除以校驗(yàn)多項(xiàng)式,所得余數(shù)序列即為冗余循環(huán)碼,將其直接加到數(shù)據(jù)后面即可。

部分程序如下:

將生成CRC碼與接收到得CRC碼進(jìn)行比較,判斷傳輸過程是否有誤,若無誤就將數(shù)據(jù)信息發(fā)送出去。

1.2.3 數(shù)據(jù)發(fā)送

數(shù)據(jù)發(fā)送部分的功能是將檢驗(yàn)完畢后的正確數(shù)據(jù)發(fā)送出去,實(shí)際上是一個(gè)并/串轉(zhuǎn)換。當(dāng)數(shù)據(jù)校驗(yàn)正確后err置位,通過pos_err濾波檢測err的上升沿,上升沿到來時(shí)pos_err置高1個(gè)時(shí)鐘周期,此時(shí)開始進(jìn)行數(shù)據(jù)發(fā)送。串口通信的傳輸格式是:1位起始位,8位數(shù)據(jù)為,1位停止位。所以需要將數(shù)據(jù)裝載成發(fā)送格式,然后再發(fā)送出去。發(fā)送時(shí)先發(fā)送起始位O,再發(fā)送數(shù)據(jù)低位,然后發(fā)送高位,最后在發(fā)送停止位1。這部分用計(jì)數(shù)器num進(jìn)行計(jì)數(shù),在case(num)語句塊里,分別發(fā)送這10位。

2 實(shí)驗(yàn)驗(yàn)證

按照以上設(shè)計(jì)方案編寫Verilog HDL程序,下載到FPGA芯片中,通過微機(jī)與設(shè)計(jì)系統(tǒng)的通信來驗(yàn)證該設(shè)計(jì)方案的可行性與可靠性。下載程序前,事先連接電路,連接好電源、串口線、 Byteblaster下載電纜。程序代碼用開發(fā)軟件QuartusⅡ5.O下載到FPGA芯片里,具體操作步驟如下:

新建Verilog HDL文件→輸入并保存代碼→新建工程→設(shè)置選項(xiàng)(選擇目標(biāo)芯片,本實(shí)驗(yàn)用的是cyclone公司的EPlC6T144C8N,配置方式,下載方式等)→編譯→配置引腳→編譯→選擇下載電纜→下載運(yùn)行。

按照以上步驟下載好程序即可以進(jìn)行實(shí)驗(yàn)驗(yàn)證。微機(jī)串口調(diào)試助手的選項(xiàng)如下:波特率:96 000 b/s;校驗(yàn)位:NONE;數(shù)據(jù)位:8位;停止位:1位;接收區(qū)設(shè)置:16進(jìn)制顯示;發(fā)送端設(shè)置:16進(jìn)制發(fā)送。

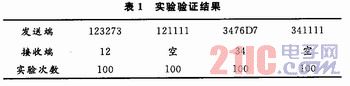

表1所示為實(shí)驗(yàn)驗(yàn)證結(jié)果,其中的12的CRC碼為3273,34的CRC碼是76D7。

實(shí)驗(yàn)驗(yàn)證結(jié)果可以看出,數(shù)據(jù)傳送的正確率很高。

3 結(jié)語

簡單介紹了FPGA芯片、Verilog HDL、串口通信協(xié)議以及硬件電路設(shè)計(jì),詳細(xì)分析了軟件部分各個(gè)模塊的設(shè)計(jì)方法,并下載程序到FPGA芯片,通過微機(jī)與系統(tǒng)之間的串口通信,驗(yàn)證了該設(shè)計(jì)的可行性與可靠性。在實(shí)現(xiàn)過程中,著重分析了移位串/并,并/串轉(zhuǎn)換過程,并加入CRC檢驗(yàn)碼生成過程和具體校驗(yàn)過程,用Verilog HDL語言編程,實(shí)現(xiàn)了串口通信的采集、數(shù)據(jù)處理、數(shù)據(jù)發(fā)送的全過程。該方案的特點(diǎn)是實(shí)現(xiàn)容易,速度快,效率高,實(shí)用性強(qiáng),可以廣泛應(yīng)用于終端、打印機(jī)、邏輯分析儀、磁盤等與計(jì)算機(jī)相距不遠(yuǎn)的人-機(jī)交互設(shè)備和串行存儲(chǔ)的外部設(shè)備。