引言:數(shù)字濾波器是語音與圖像處理、模式識(shí)別、雷達(dá)信號(hào)處理、頻譜分析等應(yīng)用中的一種基本的處理部件,它能滿足波器對幅度和相位特性的嚴(yán)格要求,避免模擬濾波器所無法克服的電壓漂移、溫度漂移和噪聲等問題。有限沖激響應(yīng)(FIR)濾波器能在設(shè)計(jì)任意幅頻特性的同時(shí)保證嚴(yán)格的線性相位特性。

一、FIR數(shù)字濾波器

FIR濾波器用當(dāng)前和過去輸入樣值的加權(quán)和來形成它的輸出,如下所示的前饋差分方程所描述的。

FIR濾波器又稱為移動(dòng)均值濾波器,因?yàn)槿魏螘r(shí)間點(diǎn)的輸出均依賴于包含有最新的M個(gè)輸入樣值的一個(gè)窗。由于它的響應(yīng)只依賴于有限個(gè)輸入,F(xiàn)IR濾波器對一個(gè)離散事件沖激有一個(gè)有限長非零響應(yīng),即一個(gè)M階FIR濾波器對一個(gè)沖激的響應(yīng)在M個(gè)時(shí)鐘周期之后為零。

FIR濾波器可用圖1所示的z域塊圖來描述。

其中每個(gè)標(biāo)有z-1的方框都代表了有一個(gè)時(shí)鐘周期延時(shí)的寄存器單元。這個(gè)圖中標(biāo)出了數(shù)據(jù)通道和必須由濾波器完成的操作。濾波器的每一級(jí)都保存了一個(gè)已延時(shí)的輸入樣值,各級(jí)的輸入連接和輸出連接被稱為抽頭,并且系數(shù)集合{hk}稱為濾波器的抽頭系數(shù)。一個(gè)M階的濾波器有M+1個(gè)抽頭。通過移位寄存器

用每個(gè)時(shí)鐘邊沿n(時(shí)間下標(biāo))處的數(shù)據(jù)流采樣值乘以抽頭,并且求和得到輸出yFIR[n]。濾波器的加法和乘法必須足夠快,在下一個(gè)時(shí)鐘來到之前形成y[n]。并且在每一級(jí)中都必須測量它們的大小以適應(yīng)他們數(shù)據(jù)通道的寬度。在要求精度的實(shí)際應(yīng)用中,Lattice結(jié)構(gòu)可以減少有限字長的影響,但增加了計(jì)算成本。一般的目標(biāo)是盡可能快地濾波,以達(dá)到高采樣率。通過組合邏輯的最長信號(hào)通路包括M級(jí)加法和一級(jí)乘法運(yùn)算。FIR結(jié)構(gòu)指定機(jī)器的每一個(gè)算術(shù)單元有限字長,并且管理運(yùn)算過程中數(shù)據(jù)流。

二、FIR數(shù)字濾波器設(shè)計(jì)的實(shí)現(xiàn)

目前FIR濾波器的實(shí)現(xiàn)方法有三種:利用單片通用數(shù)字濾波器集成電路、DSP器件和可編程邏輯器件實(shí)現(xiàn)。單片通用數(shù)字濾波器使用方便,但由于字長和階數(shù)的規(guī)格較少,不能完全滿足實(shí)際需要。使用DSP器件實(shí)現(xiàn)雖然簡單,但由于程序順序執(zhí)行,執(zhí)行速度必然不快。FPGA/CPLD有著規(guī)整的內(nèi)部邏輯陣列和豐富的連線資源,特別適合于數(shù)字信號(hào)處理任務(wù),相對于串行運(yùn)算為主導(dǎo)的通用DSP芯片來說,其并行性和可擴(kuò)展性更好。但長期以來,F(xiàn)PGA/CPLD一直被用于系統(tǒng)邏輯或時(shí)序控制上,很少有信號(hào)處理方面的應(yīng)用,其原因主要是因?yàn)樵贔PGA/CPLD中缺乏實(shí)現(xiàn)乘法運(yùn)算的有效結(jié)構(gòu)。

現(xiàn)在的FPGA產(chǎn)品已經(jīng)能夠完全勝任這種任務(wù)了。其中Altera公司的Stratix系列產(chǎn)品采用1.5V內(nèi)核,0.13um全銅工藝制造,它除了具有以前Altera FPGA芯片的所有特性外,還有如下特點(diǎn):芯片內(nèi)有三種RAM塊,即512bit容量的小RAM(M512)、4KB容量的標(biāo)準(zhǔn)RAM(M4K) 、512KB的大容量RAM(MegaRAM)。內(nèi)嵌硬件乘法器和乘加結(jié)構(gòu)的DSP塊,適于實(shí)現(xiàn)高速信號(hào)處理;采用全新的布線結(jié)構(gòu),分為三種長度的行列布線,在保證延時(shí)可預(yù)測的同時(shí)增加布線的靈活性;增加片內(nèi)終端匹配電阻,提高信號(hào)完整性,簡化PCB布線;同時(shí)具有時(shí)鐘管理和鎖相環(huán)能力。

FIR濾波器的Verilog HDL設(shè)計(jì)實(shí)例

1、設(shè)計(jì)意圖

本例主要是在Stratix器件內(nèi)實(shí)現(xiàn)基本有限脈沖響應(yīng)濾波器。

FIR的基本結(jié)構(gòu)包括一系列的乘法和加法。FIR的運(yùn)算可用式(1)的方程描述,現(xiàn)重寫如下:

一個(gè)L=8的FIR設(shè)計(jì)如圖2,利用了輸入的8個(gè)樣本。因此稱之為8抽頭濾波器。該結(jié)構(gòu)是有一個(gè)移位寄存器,乘法器和加法器組成的,可實(shí)現(xiàn)L=8階的FIR。其數(shù)據(jù)通道必須足夠?qū)挘赃m應(yīng)乘法器和加法器的輸出。這些采樣值被編碼為有限字長的形式,然后通過M個(gè)寄存器并行移動(dòng)。可見用一個(gè)MAC級(jí)連鏈就可以構(gòu)成這種機(jī)器。每個(gè)寄存器提供一個(gè)單位樣本內(nèi)延遲。這些延遲輸入與各自的系數(shù)相乘,然后疊加得到輸出。圖2所示為基于MAC的8階FIR數(shù)字濾波器結(jié)構(gòu)

在該設(shè)計(jì)中有八個(gè)抽頭,各抽頭有18位輸入和濾波器系數(shù)。由于一個(gè)DSP塊可以支持4個(gè)18位輸入的分支,所以設(shè)計(jì)需要2個(gè)DSP塊。輸入數(shù)據(jù)串行加載到DSP塊中,DSP內(nèi)部的移入/移出寄存器鏈用于產(chǎn)生延遲。濾波器系數(shù)從TriMatrix™ 的ROM存儲(chǔ)器中加載。

2、Verilog HDL代碼編寫風(fēng)格

HDL代碼編寫應(yīng)該具有很好的易讀性和可重用性,而自頂向下的分割方法可以幫助我們達(dá)到最佳的結(jié)果。HDL代碼在達(dá)到功能的情況下要盡可能的簡潔,盡量避免使用帶有特殊庫單元的實(shí)例,因?yàn)檫@樣會(huì)使得整個(gè)進(jìn)程變得不可靠。

在本設(shè)計(jì)中,我們將設(shè)計(jì)劃分成一個(gè)頂級(jí)文件和三個(gè)次級(jí)文件,并且調(diào)用了QuartusII中的MegaFunction功能輔助完成整個(gè)設(shè)計(jì)。

圖3顯示FIR濾波器的頂級(jí)方塊圖

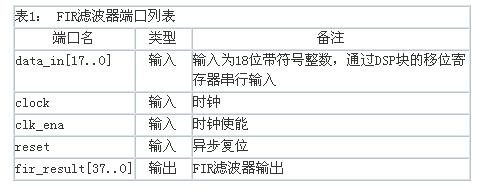

表1:FIR濾波器的設(shè)計(jì)范例的端口列表

3、驗(yàn)證仿真

完全可綜合設(shè)計(jì)的一個(gè)優(yōu)點(diǎn)就是同樣的HDL代碼能夠用于驗(yàn)證和綜合。在使用HDL代碼之前必須要驗(yàn)證設(shè)計(jì)的功能,最好且最簡單的方法就是利用驗(yàn)證工具,其次是利用仿真工具作有目的的仿真。

QuartusII內(nèi)部帶有仿真器,只要通過建立正確的Vector Waveform File(向量波形文件)就可以開始仿真了。圖4所示為QuartusII內(nèi)部仿真器得到的8階FIR的脈沖響應(yīng)波形。

五、結(jié)論

利用Verilog HDL設(shè)計(jì)數(shù)字濾波

器的最大優(yōu)點(diǎn)就是可使設(shè)計(jì)更加靈活。比較硬件電路圖設(shè)計(jì),Verilog HDL語言設(shè)計(jì)的參數(shù)可以很容易在Verilog程序中更改,通過綜合工具的簡化和綜合即可以得到電路圖,其效率要高出利用卡諾圖進(jìn)行人工設(shè)計(jì)許多。而且編譯過程也非常簡單高效。優(yōu)秀編碼風(fēng)格能夠在綜合過程中節(jié)省芯片使用的單元,從而降低設(shè)計(jì)成本。

參考文獻(xiàn):

[1]. 夏宇聞。VerilogHDL數(shù)字系統(tǒng)設(shè)計(jì)教程,北京航空航天大學(xué)出版社,北京. 2003.

[2]. Altera Corporation. Introduction to QuartusII. 2003

[3]. Michael D. Ciletti. Advanced Digital Design with Verilog HDL. Prentice Hall, NJ.2005.

[4].彭保等.基于VerilogHDL的FPGA設(shè)計(jì). 微計(jì)算機(jī)信息, 2004年第20卷第10期