摘 要: 為了使JPEG2000" title="JPEG2000">JPEG2000能應用到便攜產品中,采用了高效存儲結構的硬件實現(xiàn)方案,并設計了相應的寄存器組和控制邏輯。仿真結果表明所設計的塊編碼器能夠在0.256s內完成對一幅512×512的灰度圖像的編碼。

關鍵詞: 基于最優(yōu)截斷的嵌入式塊編碼 JPEG2000 交錯存儲

隨著多媒體市場的迅猛發(fā)展,百萬像素的數(shù)碼相機、各種功能強大的彩屏手機等數(shù)字消費產品逐漸普及。這些多媒體應用均需要處理高質量、高分辨率的大圖像,這對存儲介質的容量和傳輸信道的帶寬都提出了新要求。圖像壓縮的國際標準JPEG已不能滿足這些新的要求,而且它在低碼率時還存在著方塊效應。因此,從1997年開始,JPEG委員會就致力于開發(fā)新的靜態(tài)圖像壓縮標準JPEG2000[1],并在2000年8月形成了最終草案,在2000年12月使其成為了國際標準。

JPEG2000相比JPEG有著更大的靈活性,不僅能對原始圖像高效地壓縮,而且可以對壓縮后的數(shù)據進行處理。這意味著可以從壓縮碼流中提取一部分數(shù)據來重建低分辨率或低碼率的圖像,或者是提取圖像的感興趣區(qū)域。這樣就允許將原始圖像壓縮為單一的碼流以適應不同的傳輸信道、存儲或顯示設備,而不必考慮該圖像的大小、分量多少以及樣本的精度。

JPEG2000的一個主要特性就是基于圖像質量和分辨率的累進傳輸,為了支持這種可分級的壓縮編碼,JPEG2000采用了離散小波變換(DWT)替代JPEG中的離散余弦變換(DCT),并采用了Taubman提出的具有優(yōu)化截斷點的嵌入式塊編碼[2](EBCOT)算法。

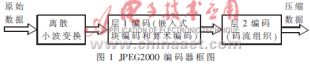

JPEG2000編碼器的框圖如圖1所示。

首先將原始圖像劃分為圖像片,通過DWT將圖像片分解為不同的分辨率級別,獲得多個子帶的頻域系數(shù),將各個子帶劃分為碼塊(典型大小是32×32或64×64),對每個碼塊進行嵌入式的塊編碼,生成上下文和待編碼的數(shù)據位;然后由算術編碼" title="算術編碼">算術編碼部分根據每個數(shù)據位的上下文自適應編碼,產生每個碼塊的子碼流;最后將各個碼塊的子碼流組織成代表碼流質量層的分組,并添加相應的頭結構信息,幫助解碼器識別如何解碼。

EBCOT[2]作為JPEG2000的核心部分,包含了層1和層2兩部分,其中嵌入式塊編碼的邏輯比較復雜,是影響編碼速度的瓶頸之一,使用通用處理器很難提高其效率。傳統(tǒng)的編碼方式采用軟件實現(xiàn),但速度和效率不高,且占用較大的存儲資源;而采用硬件實現(xiàn)方式則會有更大的靈活性。事實上采用硬件芯片實現(xiàn),不但可以提高編碼的速度和效率,而且也能根據算法本身的特點,采用特定的、高效的硬件結構來實現(xiàn)算法的關鍵部分,可以較大幅度地提高編碼效率。另外,隨著多媒體的應用和網絡應用逐步便攜化,以前多數(shù)可以在PC機上處理的工作必須轉移到便攜產品上,這對便攜產品有限的資源提出了挑戰(zhàn)。因此有必要研究硬件編碼芯片完成編碼過程,本文旨在研究JPEG2000編碼中的關鍵技術——嵌入式塊編碼。

1 算法分析及設計

嵌入式塊編碼其實是基于位平面的編碼[2],而每個位平面又被劃分為三個編碼通道,即顯著通道、細化通道和清除通道。編碼采用固定的掃描方式,每個比特位僅在其中的一個編碼通道中完成編碼。編碼過程可以分為兩個步驟,即判別編碼通道的歸屬和編碼原操作。在顯著通道中,當比特位本身不顯著,且周圍8個近鄰至少有一個是顯著時被編碼;在細化通道中,當比特位在上一個位平面就變顯著時被編碼;在清除通道,所有在上面兩個通道中略過的比特位被編碼。編碼原操作共4個,即零值編碼、符號編碼、細化編碼和游程編碼。

根據算法要求,編碼時必須用到一些編碼信息。假設碼塊的大小是32×32的,則編碼信息位包括1024個顯著信息位(表示當前系數(shù)位是否顯著)、1024個細化信息位(表示當前系數(shù)位是否第一次細化)、1024個訪問信息位(表示當前系數(shù)位是否在前面的編碼通道中編過)。當然,除此之外,還需要有1024個符號位和幅度位,因此編碼過程中需要存儲的信息為5Kbit。由于FPGA片內RAM資源十分有限,因此將碼塊量化后的小波系數(shù)存在外部RAM中(對于32×32的碼塊,16bit的系數(shù),需要存儲16Kbit),而在片內只存儲5Kbit的信息。

塊編碼過程是以一列的4個比特位為單位進行編碼,且在判別編碼通道的歸屬和編碼操作時,都需要用到當前比特位的8個近鄰的顯著信息和符號信息。因此,事實上在編碼每一列數(shù)據時,必須訪問18bit的顯著信息和符號信息,以及當前列的幅度位、訪問信息和細化信息各4bit。對于幅度位、訪問信息和細化信息,可以將每列的數(shù)據作為一個字存儲,但這種存儲方式對顯著信息和符號信息卻效率較低。如圖2所示,如果采用右邊的方案,則對于編碼帶中的每一列,必須讀取12bit的顯著和符號信息,其中有6bit是冗余的;如果采用左邊的交錯存儲" title="交錯存儲">交錯存儲[3]的方案,即對于32×32的碼塊,在其首行之前和末行之后各添加一行,形成34×32的塊,然后將每兩行作為一組,并采取交錯方式存儲(a, b,c,b,a,b,c,…,b,c,b,a),則讀取信息時不會有冗余。

顯然,交錯存儲方案更有效,只是它需要在硬件電路上付出一些代價。首先,在預處理小波數(shù)據時,必須將符號位按照上述交錯方式寫入內部RAM,這比處理幅度位復雜一些。其次,在編碼過程中,需要讀取數(shù)據至內部6×4顯著或符號寄存器,而對于奇、偶數(shù)編碼帶,其讀入順序也是交錯的,對于前者是a、b、c,對于后者則是c、b、a;而且讀取三塊內存區(qū)域的地址信號也是不同步的,如表1所示,讀取存儲器b的地址信號始終增長,而讀取存儲器a和b的地址信號則符合以下規(guī)律:前者在從奇編碼帶過渡到偶編碼帶時地址增加,而在從偶編碼帶過渡到奇編碼帶時地址保持不變;后者正好相反。

因此,必須設計相應的控制電路滿足上述要求,盡管這樣做付出了額外的代價,但卻大大提高了存儲器的讀寫效率(提高了50%),這對于需要頻繁訪問存儲器的位平面編碼來說是很寶貴的;另外,采用了交錯存儲方式,可以對三塊存儲區(qū)域獨立地產生地址信號,一次性讀取6bit,而在常規(guī)的存儲方式下,為了讀取12bit信息,必須對同一塊存儲區(qū)域訪問3次,可見采用交錯存儲的方案同時也提高了讀寫速度。

在JPEG2000的標準中,塊編碼器采用兩種編碼模式,即NORMAL和VCAUSAL。在VCAUSAL模式下,考慮當前編碼位的周圍顯著信息時,將下一編碼帶的顯著信息看作是不顯著的,而在NORMAL模式下則看作是顯著的。在文獻[4]中,采用VCAUSAL模式,盡管這樣簡化了對存儲器訪問的邏輯控制,節(jié)省了一些存儲空間,但卻降低了塊編碼器的編碼效率。因此,本文結合文獻[3]和[4],設計了圖3所示的寄存器組來配合上面介紹的交錯存儲的方案,這些內部寄存器包括6×4bit的顯著和符號信息寄存器,8bit的細化和訪問信息寄存器,4bit的幅度寄存器,如圖3所示。

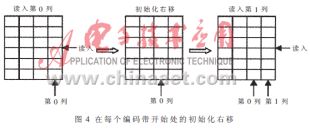

圖3中表示出了各個寄存器讀入數(shù)據和寫回更新數(shù)據的位置、當前的編碼位置和當前編碼位。這些寄存器都能完成右移一位的功能。特別值得注意的是:由于編碼過程中必須用到18bit的顯著和符號信息,因此在每個編碼帶開始處,必須對顯著和符號信息寄存器做初始化右移一次,確保在編碼第0列數(shù)據時已經有18bit的信息,見圖4的示例。

2 硬件設計

根據本文設計的編碼算法,可用如圖5所示的硬件結構實現(xiàn)嵌入式塊編碼器。

上述結構中,狀態(tài)機用于控制總體的編碼流程,外部信號START使狀態(tài)機進入初始的預處理狀態(tài),表示此時外部RAM的數(shù)據已經準備好,然后在編碼過程中根據計數(shù)器的數(shù)值進行狀態(tài)切換。

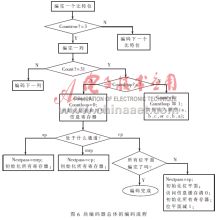

設計中用到的計數(shù)器共3個,即Countrow(位計數(shù)器)、Count(列計數(shù)器)、Countloop(編碼帶計數(shù)器)。圖6中示出了塊編碼器的總體流程,從中可以看出編碼器的狀態(tài)隨計數(shù)器的數(shù)值變化的情況。

預處理單元分為兩個部分:碼塊預處理和位平面預處理。其中碼塊預處理包括計算需要編碼的位平面數(shù),提取各個系數(shù)的符號位填充相應的符號緩存,初始化顯著信息緩存和細化緩存(全部清0);位平面預處理則提取當前位平面的幅度位填充相應的幅度緩存,初始化訪問信息緩存(全部清0)。

讀寫控制邏輯單元負責產生合適的控制信號與外部RAM和內部緩存接口;在預處理時負責外部RAM和內部緩存的讀寫控制,在編碼過程中則負責內部緩存和寄存器組的讀寫控制。

編碼單元分為兩部分(見圖7),判斷邏輯和編碼操作單元。判斷邏輯負責決策當前系數(shù)位是否屬于當前的編碼通道,編碼操作單元包括零值編碼、細化編碼和符號編碼,而游程編碼則采用硬連線編碼,不使用獨立的單元。這幾個編碼操作單元直接采用組合邏輯實現(xiàn),而不是采用查表方式。多路選擇器則根據當前執(zhí)行的編碼操作選擇輸出合適的CX和D。

FIFO單元用于解決塊編碼和算術編碼邏輯之間的異步問題(因為前者產生數(shù)據具有間歇性,且算術編碼處理數(shù)據也會有一定的延遲)。

3 結論與展望

本文通過對嵌入式塊編碼的算法分析,結合文獻[3]和[4]的方案,采用了比較合理的存儲結構來存儲編碼信息,并設計了相應的寄存器組和地址產生控制邏輯,本設計能夠做到讀寫操作無冗余信息。

本編碼器算法采用MODELSIM進行功能仿真,圖8是在MODELSIM中截取的部分仿真波形。仿真所采用的時鐘頻率是50MHz,從圖8中可以看出編碼過程在1074090ns完成,大約1ms左右完成32×32碼塊的編碼。因此,對于一幅512×512的灰度圖像,估計能夠在0.256s內完成編碼。本設計選用的FPGA芯片最高時鐘頻率可達到275MHz,估計通過一定的優(yōu)化,可使工作頻率進一步提高;另外,塊編碼的算法本身就蘊含著并行的特性,可以在FPGA中實現(xiàn)多個塊編碼器單元同時處理多個碼塊的數(shù)據,這樣編碼一幅圖像的速度可以進一步提高。

參考文獻

1 M.Boliek,C.Christopoulos,E.Majani (Editors). JPEG 2000 Part 1 Final Publication Draft.ISO/IEC JTC1/SC29/WG1 N2678, July 2002

2 D.Taubman.High Performance Scalable Image Compression with EBCOT. IEEE Transactions on Image Processing,2000;9(7):1158~1170

3 K.-F. Chen, C.-J. Lian, H.-H. Chen, L.-G. Chen. Analysis and Architecture Design of EBCOT for JPEG2000. IEEE ISCAS 2001,2001;2(3):765~768

4 K.Andra, T. Acharya,C. Chakrabarti. Efficient VLSI Imple- mentation of Bit Plane Coder of JPEG2000. Proc. of SPIE Applications of Digital Image Processing, 2001