0 引 言

傳統(tǒng)的數(shù)據(jù)采集系統(tǒng)一般采用單片機(jī),系統(tǒng)大多通過PCI總線完成數(shù)據(jù)的傳輸。其缺點(diǎn)是數(shù)學(xué)運(yùn)算能力差;受限于計(jì)算機(jī)插槽數(shù)量和中斷資源;不便于連接與安裝;易受機(jī)箱內(nèi)電磁環(huán)境的影響。這些問題遏制了基于PCI總線的數(shù)據(jù)采集系統(tǒng)的進(jìn)一步開發(fā)和應(yīng)用。因此,需要一種更為簡便通用的方式完成采集系統(tǒng)和計(jì)算機(jī)數(shù)據(jù)的交互。

數(shù)據(jù)采集系統(tǒng)性能的好壞,主要取決于它的精度和速度。在保證精度的條件下應(yīng)盡可能地提高采樣速度,以滿足實(shí)時(shí)采集、實(shí)時(shí)處理和實(shí)時(shí)控制的要求。實(shí)踐表明,采用ARM 32位嵌入式微處理器作為控制器,用USB(通用串行總線)和上位機(jī)連接構(gòu)成的數(shù)據(jù)采集系統(tǒng)能大大提高系統(tǒng)數(shù)據(jù)處理的能力,降低對PC機(jī)和接口速度的依賴。

1 系統(tǒng)硬件設(shè)計(jì)

實(shí)現(xiàn)系統(tǒng)功能的基本思路是:以CPLD/FPGA實(shí)現(xiàn)儀器的數(shù)字平臺,和ARM嵌入式處理器及單片機(jī)一起實(shí)現(xiàn)對整機(jī)的智能控制和高速的數(shù)據(jù)處理。

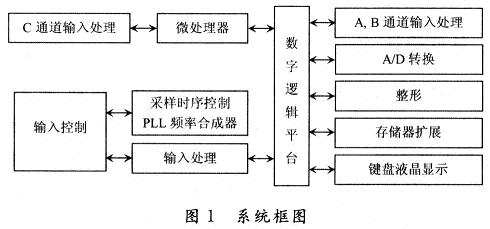

1.1 系統(tǒng)框圖

系統(tǒng)原理方框圖如圖1所示,該系統(tǒng)主要由微處理器、數(shù)字邏輯平臺、輸入控制、A,B通道輸入處理、C通道輸入處理、整形、A/D轉(zhuǎn)換、采樣時(shí)序控制、鍵盤液晶顯示、存儲器擴(kuò)展等模塊構(gòu)成。

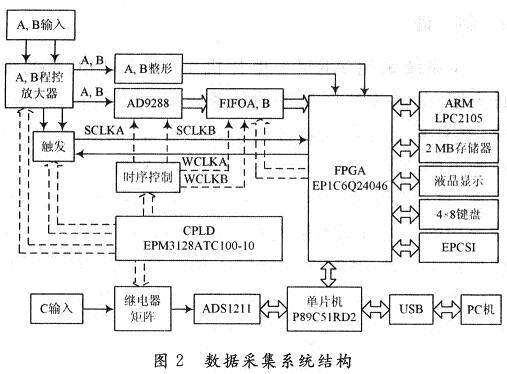

1.2 系統(tǒng)結(jié)構(gòu)圖

系統(tǒng)硬件如圖2所示,利用一片規(guī)模較小的CPLD和一片規(guī)模較大的FPGA組合構(gòu)成系統(tǒng)的數(shù)字邏輯平臺。CPLD主要用作輸入控制,F(xiàn)PGA則連接了系統(tǒng)的其他各個(gè)部分。CPLD/FPGA可實(shí)現(xiàn)現(xiàn)場編程,使用CPLD/FPGA可使設(shè)計(jì)方便,利用它靈活、校驗(yàn)快以及設(shè)計(jì)可隨意改變的特點(diǎn),可大大縮短研制時(shí)間。

1.3 主要部分功能

1.3.1 微處理器

系統(tǒng)采用由Philips公司生產(chǎn)的ARM 32位微處理器LPC2105作為主CPU,進(jìn)行高速的數(shù)據(jù)處理,用8位單片機(jī)P89C51RD2作為輔CPU,進(jìn)行速度較慢的數(shù)據(jù)處理,控制其他外圍芯片和模塊實(shí)現(xiàn)A,B通道模擬帶寬100 MHz、峰值電壓±100 V和C通道二極管通斷、電壓、電流、電阻值的數(shù)據(jù)采集功能。

1.3.2 A,B通道部分

通過自動增益電路(AGC)即程序控制放大器,將被測模擬信號調(diào)理到適合ADC芯片(AD9288)采樣的范圍。根據(jù)頻率的大小和觸發(fā)方式,運(yùn)用實(shí)時(shí)采樣或等效采樣對調(diào)理后的模擬信號進(jìn)行采樣(A/D轉(zhuǎn)換)。利用高速FIFO存貯器(IDT72V261LAl0A)存儲采樣后得到的數(shù)據(jù)。

結(jié)合鍵盤操作和系統(tǒng)設(shè)置,對采樣后的數(shù)據(jù)進(jìn)行數(shù)學(xué)運(yùn)算,將還原后的波形數(shù)據(jù)和參數(shù)送液晶顯示器顯示或存入閃存里面或通過USB接口傳送給PC機(jī),從而實(shí)現(xiàn)了A,B通道高速數(shù)據(jù)采集的功能。

1.3.3 C通道部分

C輸入通道為多功能輸入通道,系統(tǒng)通過控制繼電器矩陣來選擇不同的模塊測量電壓、電流或二極管的通斷和電阻。被測元件參數(shù)或電壓、電流經(jīng)過多功能轉(zhuǎn)換電路處理后,其信號送24 b的A/D轉(zhuǎn)換器ADS1211采樣后送單片機(jī)P89C51RD2,分析被測元件或電壓、電流的參數(shù)值,從而實(shí)現(xiàn)了C通道高精度數(shù)據(jù)采集的功能。

1.3.4 鍵盤、液晶顯示接口電路

本系統(tǒng)采用4×8的鍵盤和320×240不帶驅(qū)動器的液晶顯示模塊,驅(qū)動器和顯存設(shè)計(jì)在FPGA內(nèi)。以上系統(tǒng)通過USB接口與PC機(jī)通信,在上位機(jī)的控制下,實(shí)現(xiàn)可視化人機(jī)交互界面。同時(shí)系統(tǒng)也保留了傳統(tǒng)的RS 232接口,但只是用于ARM和單片機(jī)的編程下載。

2 軟件設(shè)計(jì)流程

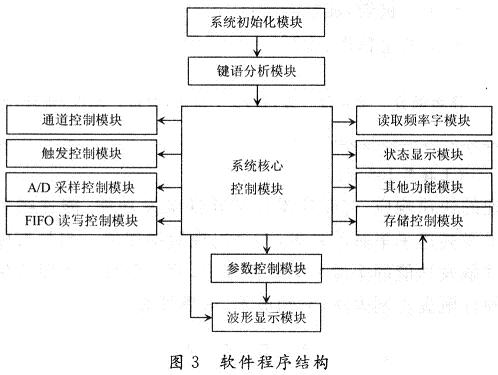

LPC2105芯片作為系統(tǒng)主控制中心及數(shù)據(jù)處理中心,整個(gè)系統(tǒng)的運(yùn)轉(zhuǎn)受到它的控制,例如響應(yīng)用戶的按鍵操作,發(fā)出通道控制,A/D采樣時(shí)鐘控制,F(xiàn)IFO寫時(shí)鐘的選擇,菜單及系統(tǒng)狀態(tài)顯示,F(xiàn)IFO數(shù)據(jù)的處理,信號或參數(shù)的自動測試等。

數(shù)據(jù)采集卡的軟件程序結(jié)構(gòu)如圖3所示,可分為系統(tǒng)初始化模塊、鍵語分析模塊、系統(tǒng)核心控制模塊、通道控制模塊、觸發(fā)控制模塊、A/D采樣控制模塊、FIFO讀寫控制模塊、讀取頻率字模塊、參數(shù)測試模塊、狀態(tài)顯示模塊、波形顯示模塊、存儲控制模塊、其他功能模塊。

系統(tǒng)的初始化模塊包括開機(jī)自檢、硬件參數(shù)初始化、系統(tǒng)狀態(tài)初始化(如通道的波形顯示狀態(tài)初始化)等。鍵語分析模塊對面板上的用戶輸入進(jìn)行分析處理,通過核心控制模塊調(diào)用相應(yīng)的功能處理模塊,通過對通道控制模塊、觸發(fā)控制模塊、A/D采樣控制模塊、FIFO讀寫控制模塊、讀取頻率字模塊、參數(shù)測試模塊、狀態(tài)顯示模塊、波形顯示模塊、存儲控制模塊、其他功能模塊的函數(shù)調(diào)用來實(shí)現(xiàn)對來自鍵語分析的處理功能。狀態(tài)顯示模塊顯示程序運(yùn)行時(shí)的各種狀態(tài),如當(dāng)前數(shù)據(jù)采集的掃描速率、通道的垂直靈敏度等。波形顯示模塊顯示采集的波形。

整個(gè)系統(tǒng)的程序又可分成底層驅(qū)動和上層軟件。底層驅(qū)動指對本系統(tǒng)其他外設(shè)或器件直接控制或訪問的程序部分,包括LPC2105和單片機(jī)的初始化(即對片內(nèi)各核心寄存器的操作賦值、對片上外設(shè)的初始化賦值、對片內(nèi)各外設(shè)中斷及外部中斷的控制操作)。上層軟件主要指:菜單的設(shè)計(jì)及顯示、數(shù)據(jù)的處理、波形的恢復(fù)及平滑等。