1、引言

隨著電子技術(shù)和計(jì)算機(jī)技術(shù)的迅猛發(fā)展,國(guó)內(nèi)開(kāi)展先進(jìn)飛機(jī)配電系統(tǒng)研究的技術(shù)手段已比國(guó)外八十年代好得多, 對(duì)固態(tài)功控系統(tǒng)研究,就是基于目前飛機(jī)配電系統(tǒng)的發(fā)展應(yīng)運(yùn)而生的,目前市場(chǎng)上的均為單開(kāi)關(guān)結(jié)構(gòu),最近多開(kāi)關(guān)的 SSPC 組已經(jīng)處于研發(fā)之中,SSPC 組共享大規(guī)模控制芯片,可進(jìn)一步提高功率密度和擴(kuò)展功能。現(xiàn)在國(guó)外對(duì)進(jìn)行研究的公司有美國(guó)的印和立奇等,國(guó)內(nèi)對(duì)的研究處于工程樣機(jī)階段。

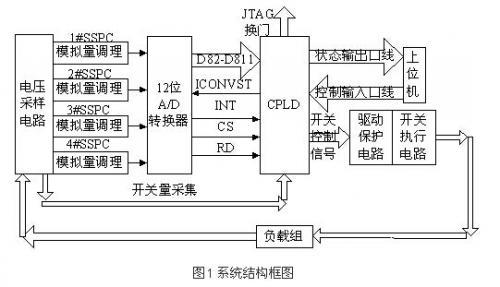

2、系統(tǒng)總體結(jié)構(gòu)框圖

如圖 1 所示,每路 SSPC 取樣電阻上的電壓經(jīng)過(guò)調(diào)理電路和低通濾波器以后,送到 4 通道 A/D 轉(zhuǎn)換器的一個(gè)模擬輸入端,A/D 轉(zhuǎn)換器的數(shù)據(jù)輸出端、狀態(tài)信號(hào)和控制信號(hào)分別接到 CPLD 的 I/O 引腳,便于程序控制 A/D 轉(zhuǎn)換器的動(dòng)作。CPLD 另外的 I/O 口可以配置為 MOSFET 的開(kāi)關(guān)命令輸出口線、SSPC 的狀態(tài)輸出口線和與上位機(jī)相連的控制命令輸入口線;CPLD 自身提供的 JTAG BST 電路,可以方便的測(cè)試系統(tǒng)內(nèi)部器件之間的連接和檢驗(yàn)器件的操作。

3、硬件設(shè)計(jì)

3.1 邏輯控制器件

根據(jù)設(shè)計(jì)要求,需要集成多個(gè) SSPC 在一塊電路板上,如果完全用分離元件來(lái)實(shí)現(xiàn),數(shù)字電路的體積相當(dāng)龐大,因此我們采用復(fù)雜可編程邏輯器件 -CPLD。ALTERA 公司的可編程邏輯器件在工業(yè)界是最快和最大的,該公司的 PLD 器件不僅具有 PLD 的一般優(yōu)點(diǎn),而且還有如下一些優(yōu)勢(shì):高性能、高集成度、價(jià)格合理、開(kāi)發(fā)周期較短和利于編程。

根據(jù)軟件所需要的資源,邏輯主控芯片采用 ALTERA 公司的 MAX3000A 系列芯片中的 EPM3256ATC144-10,相對(duì)于 MAX7000 系列,MAX3000A 系列的 I/O 電壓為+3.3V,而 MAX7000 系列的 I/O 電壓為+5V,一般來(lái)說(shuō),對(duì)于控制信號(hào)的輸出,+5V 電壓可靠性高些,但是低電壓、低功耗是以后的發(fā)展趨勢(shì),并且也利于以后的換代產(chǎn)品的設(shè)計(jì),而對(duì)于可靠性的考慮可以通過(guò)加強(qiáng)外圍電路的設(shè)計(jì)來(lái)達(dá)到系統(tǒng)設(shè)計(jì)的要求。

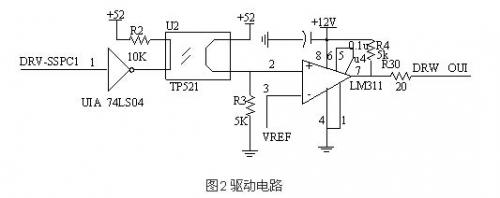

3.2 電力 MOSFET 的驅(qū)動(dòng)電路

控制命令經(jīng)過(guò)光耦隔離輸出后,接到比較器 LM311 的正相輸入端,比較器的反相輸入端輸入的是參考電平 Vref,取 Vref=3V。當(dāng) DRV_SSPC1=1 時(shí),光耦輸出高電平,比較器正相輸入端電壓大于反相輸入端電壓,比較器輸出 DRC_OUT 為高電平:當(dāng) DRV_SSPC1=0 時(shí),光耦輸出低電平,比較器正相輸入端電壓小于反相輸入端電壓,比較器輸出 DRC_OUT 為低電平;比較器的輸出端接低值電阻 R30,目的是與電力 MOSFET 的 G 極和 D 極間寄生電容構(gòu)成一定時(shí)間的阻容延時(shí),保證 MOS 管的導(dǎo)通時(shí)間不至于太快或太慢,減小寄生振蕩,該電阻值應(yīng)隨被驅(qū)動(dòng)器件額定電流值的增大而減小。

3.3 信號(hào)采集電路

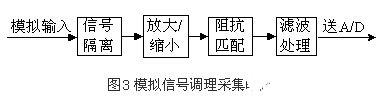

1、模擬量采集電路。信號(hào)采樣!調(diào)理的方塊圖如圖 3 所示。模擬信號(hào)經(jīng)過(guò)隔離電路,得到取樣電壓,經(jīng)過(guò)一定比例的放大,通過(guò)跟隨器進(jìn)行阻抗匹配,最后經(jīng)過(guò)濾波處理,濾去信號(hào)中的交流分量,得到的信號(hào)就可以送到 A/D 轉(zhuǎn)換器的模擬輸入端。

需要模數(shù)轉(zhuǎn)換的模擬電壓信號(hào)為直流電壓信號(hào),范圍大概在 0V-7V 之間,由于 SSPC 在電路中是用來(lái)作為負(fù)載的一個(gè)開(kāi)關(guān)保護(hù)措施, 因此,要求其動(dòng)作時(shí)間盡可能的快,細(xì)化到電路的每一個(gè)環(huán)節(jié),就要求 A/D 轉(zhuǎn)換器的轉(zhuǎn)換時(shí)間盡量小,在 A/D 的轉(zhuǎn)換精度和轉(zhuǎn)換時(shí)間之間權(quán)衡,得出一個(gè)折中的方案。經(jīng)過(guò)對(duì)比,采用 AD 公司的 12 位的 A/D 轉(zhuǎn)換器 AD7874,這是一款 4 通道同時(shí)采樣,12 位快速低功耗的 A/D 轉(zhuǎn)換器,內(nèi)部包括一個(gè) 12 位高速模數(shù)轉(zhuǎn)換器、片上時(shí)鐘和四個(gè)采樣 / 保持器。這樣,避免了四個(gè)輸入通道共享一個(gè)采樣 / 保持器所帶來(lái)的問(wèn)題一通道間采樣出現(xiàn)相位差。

2、開(kāi)關(guān)量采集電路。開(kāi)關(guān)量主要有兩個(gè):表示負(fù)載狀態(tài)的 STA_LOAD 和表示電力 MOSFET 狀態(tài)的 STA_SSPC。規(guī)定:當(dāng)負(fù)載的電流大于 SSPC 額定電流的 15%時(shí),表示負(fù)載狀態(tài)的開(kāi)關(guān)量 STA_LOAD 為低(0);當(dāng) MOSFET 處于導(dǎo)通狀態(tài)時(shí),表示 MOSFET 開(kāi)通關(guān)斷狀態(tài)的開(kāi)關(guān)量 STA_SSPC=1。通過(guò)對(duì) CPLD 采集到的 A/D 通道的數(shù)據(jù)進(jìn)行判斷:當(dāng) i_load 大于負(fù)載電流的 15%時(shí),表明負(fù)載導(dǎo)通,置 STA_LOAD0;當(dāng) i_load 小于負(fù)載電流的 15%時(shí),表明負(fù)載不工作,置 STA_LOAD 為 1。STA_LOAD 通過(guò) CPLD 的 I/O 口輸出。

3、I/O 驅(qū)動(dòng)與隔離電路設(shè)計(jì)。CPLD 與外圍器件接口時(shí),應(yīng)考慮驅(qū)動(dòng)能力,在中間添加驅(qū)動(dòng)器和隔離器件,以保護(hù) CPLD 不受損害。因?yàn)楸容^器是 12V 供電,所以出來(lái)的狀態(tài)量信號(hào)為 12V 信號(hào),而邏輯判斷模塊的 CPLD 是 3.3V I/O 供電和 2.5 V 內(nèi)核供電,因此對(duì) SSPC 狀態(tài)信號(hào)的采集和控制信號(hào)的輸出都需要經(jīng)過(guò)電平轉(zhuǎn)換和電氣隔離,具體采用光耦隔離的方式,既實(shí)現(xiàn)了電氣隔離,又實(shí)現(xiàn)了電平轉(zhuǎn)換。當(dāng)控制信號(hào)從 CPLD 輸出時(shí),因光耦的驅(qū)動(dòng)電流相對(duì)較大(20mA 左右),如果直接從 CPLD 輸出來(lái)驅(qū)動(dòng),就會(huì)使 CPLD 因電流太小而無(wú)法驅(qū)動(dòng),因此實(shí)際中采用六通道反相器 74HC04 來(lái)做光耦前一級(jí)的驅(qū)動(dòng)。而對(duì)輸入 CPLD 的信號(hào),因?yàn)槭菑墓怦钶敵鰜?lái)的,電流一般不大(Ic《5mA ),所以可以不用反相器來(lái)驅(qū)動(dòng)。

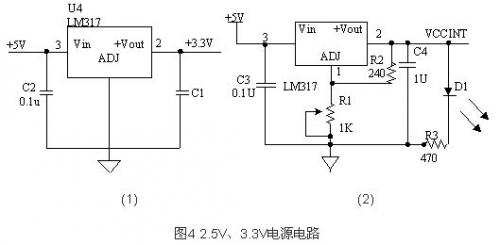

3.4 電源電路

在目前的實(shí)驗(yàn)系統(tǒng)中,SSPC 的供電由市電經(jīng)變換得來(lái)。它所使用得電源種類(lèi)較多,包括 2.5V, 3.3V, +5V,-5V, 12V 等。其中,2.5 V 為 CPLD 核心所使用的電源,CPLD 的 I/O 引腳需要使用 3.3V 的電源,+5 V 電源用于一些外設(shè)器件和參考標(biāo)準(zhǔn),12V 電源主要用于運(yùn)算放大器和比較器。3.3V 和 2.5V 電源都是由 5V 電源變換得到的。5V 和 12V 則采用了 ANSJ 公司生產(chǎn)的 AC/DC 電源模快得到,這類(lèi)電源使用簡(jiǎn)單,具備高功率、高效率、寬輸入范圍、低噪聲、可靠及應(yīng)用簡(jiǎn)易等優(yōu)點(diǎn),且結(jié)構(gòu)緊密,具有優(yōu)良的輸出編程和低待機(jī)損耗等特性,具備輸出過(guò)壓保護(hù)及過(guò)溫關(guān)機(jī)功能。圖 4 是 5V 轉(zhuǎn) 2.5V 和 3.3V 的電源電路,采用了輸出電壓連續(xù)可調(diào)的器件 LM317。它可以提供高達(dá) 1.5A 電流,而且電壓調(diào)整方便,非常適合 CPLD 的供電要求。如圖 4 中的 2 圖所示,輸出電壓 VCCINT=1.25(1+R1/R2)+IADJR2。

4、可編程邏輯區(qū)設(shè)計(jì)

1、A/D 數(shù)據(jù)采集模塊。利用狀態(tài)機(jī)的概念,一個(gè)步驟對(duì)應(yīng)一個(gè)狀態(tài),每個(gè)狀態(tài)賦予 CPLD 特定的功能。將 AD7874 的工作大致分為 10 個(gè)步驟區(qū)間。AD7874 轉(zhuǎn)換的量化噪聲與輸出位數(shù)和量化步長(zhǎng)有關(guān),輸出位數(shù)越多,量化步長(zhǎng)越小,則量化噪聲越小。實(shí)際 A/D 轉(zhuǎn)換器多為定點(diǎn)制,動(dòng)態(tài)范圍為±1,輸出最大值為 1。如果只考慮量化噪聲,則輸入信號(hào)信噪比為

如果 AD7874 為 12 位,則 SNR=70dB 左右,在應(yīng)用中一般已經(jīng)足夠,字長(zhǎng)過(guò)長(zhǎng)并不是非常必要,因?yàn)檩斎肽M信號(hào)本身有一定的信噪比,A/D 轉(zhuǎn)換器的量化噪聲比模擬信號(hào)的噪聲電平更低是沒(méi)有意義的。

2、開(kāi)關(guān)量采集模塊。上位機(jī)下傳的控制信號(hào),由于存在各種干擾,使得開(kāi)關(guān)量在實(shí)驗(yàn)中經(jīng)常出現(xiàn)抖動(dòng),另一方面,電路中經(jīng)過(guò)比較器得到的開(kāi)關(guān)量(如 STA _SSPC),由于主電路中的電流不穩(wěn)定,偶爾出現(xiàn)電流過(guò)沖,使得送到 CPLD 的開(kāi)關(guān)量信號(hào)也會(huì)出現(xiàn)抖動(dòng);這些都會(huì)導(dǎo)致 SSPC 經(jīng)常誤動(dòng)作,為此,需要設(shè)計(jì)一個(gè)專(zhuān)門(mén)的開(kāi)關(guān)量去抖動(dòng)電路,降低 SSPC 誤動(dòng)作的概率。實(shí)際中采用的是延遲電路后級(jí)加上 R-S 觸發(fā)器,具體的工作原理如下所述:先將輸入信號(hào)先引至輸入端,經(jīng)過(guò)兩級(jí)的 D 觸發(fā)器延遲后,然后再通過(guò) RS 觸發(fā)器作處理。

3、整個(gè)數(shù)據(jù)分析過(guò)程包括以下幾部分:

(1) 當(dāng)電流在額定范圍內(nèi),SSPC 正常工作;

(2) 電流大于額定電壓,小于額定電壓的 800%時(shí),SSPC 進(jìn)入反時(shí)限保護(hù);

(3) 當(dāng)電流大于額定電流的 800%時(shí),SSPC 立刻跳閘。

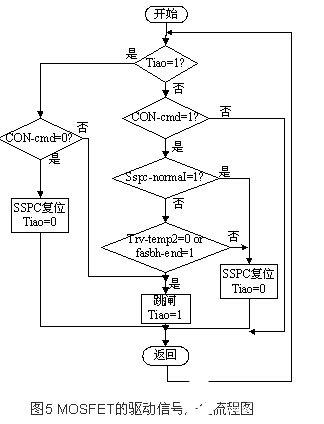

4、邏輯判斷模塊。邏輯判斷模塊將采集到的電流信號(hào)、接收到的控制命令和內(nèi)部狀態(tài),經(jīng)過(guò)邏輯判斷后,綜合得出電力 MOSFET 的導(dǎo)通 / 關(guān)斷指令,作為驅(qū)動(dòng)電路的輸入信號(hào)。程序流程如圖 5 所示。在對(duì) SSPC 的控制中,最容易出現(xiàn)的問(wèn)題就是誤動(dòng)作,為此,采用了較為復(fù)雜的控制邏輯,以此降低 SSPC 誤動(dòng)作的概率。SSPC 的控制是通過(guò)“相鄰兩位、多條指令”兩個(gè)步驟來(lái)完成的,只有幾個(gè)條件同時(shí)滿足才能使 SSPC 動(dòng)作,缺一不可,這就大大降低了 SSPC 誤動(dòng)作的概率。