1 引言

隨著現(xiàn)代武器與航天技術(shù)的發(fā)展,要求雷達(dá)應(yīng)具有高精度、遠(yuǎn)距離、高分辨力等性能。簡(jiǎn)單矩形脈沖雷達(dá)存在雷達(dá)探測(cè)能力與距離分辨力之間的矛盾。為解決這一矛盾,大多數(shù)現(xiàn)代雷達(dá)采用脈沖壓縮技術(shù),調(diào)制信號(hào)頻率或相位,從而產(chǎn)生大時(shí)寬帶寬信號(hào),接收端通過具有匹配濾波器的接收機(jī)接收,產(chǎn)生窄時(shí)間脈沖,提高距離分辨率。以數(shù)字方式實(shí)現(xiàn)的脈沖壓縮具有可靠性高、靈活性好、可編程、便于應(yīng)用。因此,這里介紹一種分布式算法實(shí)現(xiàn)時(shí)域脈沖壓縮,它是一種基于查找表的計(jì)算方法,通過將各輸入數(shù)據(jù)每一對(duì)應(yīng)位產(chǎn)生的部分積預(yù)先相加形成相應(yīng)部分積,然后再對(duì)各部分積累加形成最終結(jié)果,從而實(shí)現(xiàn)乘加功能。與傳統(tǒng)算法(所有乘積產(chǎn)生后,再相加完成乘加運(yùn)算)相比,分布式算法可極大減少硬件電路規(guī)模,易于實(shí)現(xiàn)流水線處理,提高電路執(zhí)行速度。

2 脈沖壓縮

2.1 脈沖壓縮處理過程

脈沖壓縮處理有時(shí)域和頻域兩種方式。其中.時(shí)域處理是由數(shù)字有限沖擊響應(yīng)(FIR)實(shí)現(xiàn)的過程,即信號(hào)與系數(shù)的卷積;而頻域處理則是先用FFT計(jì)算出數(shù)字回波信號(hào)的頻譜S(ω),再將其與匹配濾波器的頻響H(ω)相乘,最后進(jìn)行快速傅里葉反變換(IFFT),得到脈壓結(jié)果。一般而言,對(duì)于大時(shí)寬帶寬信號(hào),采用頻域處理較好;對(duì)于小時(shí)寬帶寬信號(hào),采用時(shí)域處理較好。脈沖壓縮信號(hào)實(shí)現(xiàn)方法有:線性調(diào)頻信號(hào)、非線性調(diào)頻信號(hào)和相位編碼信號(hào)。線性調(diào)頻信號(hào)是通過非線性相位調(diào)制或線性頻率調(diào)制(LFM)來獲得大時(shí)寬帶寬積。與其他脈沖壓縮信號(hào)相比,它具有匹配濾波器對(duì)回波信號(hào)的多普勒頻移不敏感的優(yōu)點(diǎn)。這里采用的LFM信號(hào)是由一個(gè)匹配濾波器來處理,并具有不同多普勒頻移的信號(hào)。

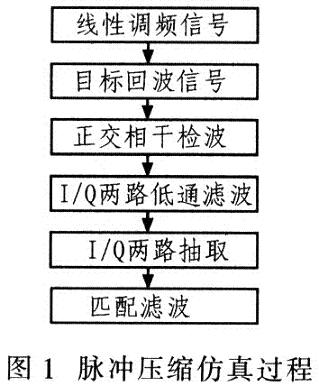

IFM數(shù)字脈沖壓縮仿真流程包括線性調(diào)頻(LFM)信號(hào)產(chǎn)生、回波信號(hào)的模擬、正交相干檢波、I/O兩路信號(hào)低通濾波及抽取、視頻信號(hào)(零中頻)匹配濾波,如圖1所示。作為關(guān)鍵部分的匹配濾波器,它是一種線性相位的FIR濾波器,其濾波器系數(shù)為發(fā)射信號(hào)的復(fù)共軛,h(n)=x*(N-n),而為了降低旁瓣,一般給系數(shù)加上相應(yīng)權(quán)值。

2.2 脈沖壓縮處理仿真

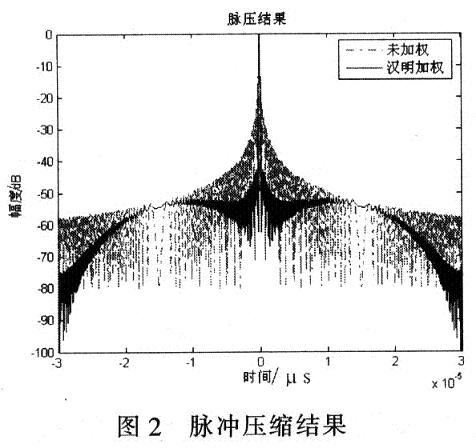

設(shè)線性調(diào)頻信號(hào)的載頻fo=25 MHz,調(diào)制頻率帶寬B=5MHz,采樣頻率fs=20 MHz,滿足中頻采樣定理要求,脈沖寬度τ=60μs,目標(biāo)距離12 km,時(shí)間延遲脈沖重復(fù)周期為320μs,信號(hào)幅度A=l。一個(gè)脈沖采樣點(diǎn)數(shù)為L(zhǎng)=Tfs=1 200,線性調(diào)頻信號(hào)的時(shí)寬帶寬積即脈寬壓縮比D=300,則輸出脈沖寬度r'=60μs/300=200 ns。

由以上參數(shù)產(chǎn)生的線性調(diào)頻信號(hào)的目標(biāo)回波信號(hào),經(jīng)正交相干檢波產(chǎn)生的I/Q兩路信號(hào)抽取。最后進(jìn)行匹配濾波的各個(gè)過程的MATLAB仿真,脈沖壓縮結(jié)果如圖2所示。從圖2看出,脈沖壓縮后產(chǎn)生窄脈沖,輸出波形具有辛格函數(shù)性質(zhì).除主瓣外。在時(shí)間軸上還有延伸的一串副瓣。另外還可看出.經(jīng)過海明加權(quán)后的第一副瓣比主瓣下降約40 dB,而主瓣寬度也相應(yīng)拓展,比沒有加權(quán)的脈沖壓縮結(jié)果理想許多。

3 邏輯設(shè)計(jì)和仿真

3.1 分布式算法的硬件結(jié)構(gòu)

根據(jù)分布式算法原理得出采用FPGA實(shí)現(xiàn)的分布式算法的硬件結(jié)構(gòu),如圖3所示。

圖3中N為該模塊的濾波器階數(shù),那么DALUT有2N個(gè)存儲(chǔ)單元,如果濾波器抽頭數(shù)過多,查找表規(guī)模隨抽頭數(shù)的增加成指數(shù)遞增。因此實(shí)現(xiàn)高階濾波器時(shí),要分割查找表。因?yàn)榫矸e運(yùn)算是線性的,所以在將每個(gè)子表的輸出相加可得到總輸出。邏輯設(shè)計(jì)是基于Altera公司的Stratix系列FPGA為平臺(tái),在OuartusII軟件中利用VHDL語言和原理圖進(jìn)行邏輯設(shè)計(jì)。

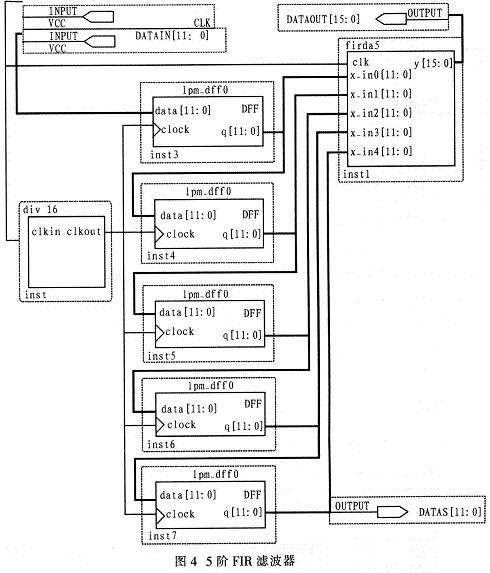

3.2 5階FIR濾波器設(shè)計(jì)

Stratix器件的LPM_ROM模塊最少有32(25)個(gè)存儲(chǔ)單元,所以設(shè)定濾波器模塊階數(shù)N=5。5階濾波器模塊設(shè)計(jì)如圖4所示,其中l(wèi)pm_dff0為12位鎖存器,5個(gè)鎖存器對(duì)輸入數(shù)據(jù)進(jìn)行移位寄存,firda5為分布式算法模塊,DATAS[11:0]輸出引腳是濾波器模塊最后一個(gè)鎖存器輸出,作為濾波器模塊級(jí)聯(lián)時(shí)不同濾波器模塊之間的數(shù)據(jù)移位。

分布式算法模塊firda5實(shí)現(xiàn)數(shù)據(jù)的并串轉(zhuǎn)換、DALUT查表、加權(quán)累加。設(shè)計(jì)中采用狀態(tài)機(jī)實(shí)現(xiàn)分布式算法的狀態(tài)轉(zhuǎn)移,這樣簡(jiǎn)化計(jì)算過程,在實(shí)現(xiàn)算法時(shí)發(fā)揮關(guān)鍵作用。根據(jù)分布式算法的狀態(tài)轉(zhuǎn)移關(guān)系,每輸入一個(gè)數(shù)據(jù),在下一個(gè)數(shù)據(jù)輸入之前,需要在狀態(tài)s1停留12位數(shù)據(jù)寬度的時(shí)鐘時(shí)間和2個(gè)寄存的時(shí)鐘時(shí)間(在QuartusII軟件中,器件選用Stratix系列,利用LPM_ROM模塊,地址輸入是寄存輸入,數(shù)據(jù)輸出也包含寄存器)以及一個(gè)數(shù)據(jù)輸出時(shí)鐘時(shí)間:所以系統(tǒng)時(shí)鐘必須為數(shù)據(jù)時(shí)鐘的16倍,圖中div 16實(shí)現(xiàn)16分頻。

3.3 50階匹配濾波器設(shè)計(jì)

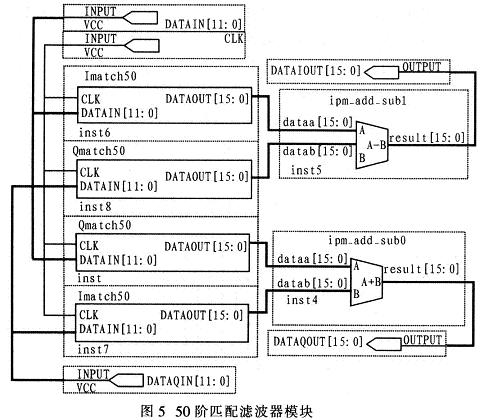

由于匹配濾波器就是有限脈沖響應(yīng)(FIR)濾波器,具有線性特性,所以通過低階濾波器的直接級(jí)聯(lián)相加就可以實(shí)現(xiàn)高階濾波器,前一個(gè)濾波器的移位數(shù)據(jù)DATAS[11:0]作為下一個(gè)濾波器模塊的信號(hào)輸入,每個(gè)濾波器模塊都根據(jù)圖4設(shè)計(jì),只需要根據(jù)不同的系數(shù)更改DALUT表中的數(shù)據(jù)。50階匹配濾波器的邏輯設(shè)計(jì)如圖5所示。其中,Imatch50模塊為匹配濾波器復(fù)系數(shù)實(shí)部對(duì)應(yīng)的50階濾波器,而Qmatch50模塊為匹配濾波器復(fù)系數(shù)虛部對(duì)應(yīng)的50階濾波器。輸出信號(hào)包括16位I信號(hào)和16位O信號(hào)。

對(duì)該匹配濾波器波形仿真,輸入數(shù)據(jù)為MATLAB仿真的12位數(shù)據(jù),由于該濾波器做的是50x50點(diǎn)的卷積.所以輸出數(shù)據(jù)為50+50-1=99個(gè),仿真波形如圖6所示。

4 結(jié)論

通過仿真分析脈沖壓縮過程和調(diào)試驗(yàn)驗(yàn)證整個(gè)設(shè)計(jì).可看出利用基于分布式算法能夠大大減少數(shù)字脈沖壓縮的運(yùn)算量,提高脈沖壓縮效率。由于匹配濾波器的系數(shù)是以中心,點(diǎn)對(duì)稱的,所以可采用線性相位FIR濾波器在FPGA中的實(shí)現(xiàn)算法,這樣同等性能的濾波器設(shè)計(jì)可減小一半的硬件規(guī)l模。同時(shí),還可通過分時(shí)復(fù)用嵌入式乘法器來實(shí)現(xiàn)卷積,這樣就會(huì)節(jié)省更多的邏輯單元,并且有能力實(shí)現(xiàn)更多功能。