0 引言

光電碼盤是一種基本的位置、速度檢測(cè)反饋單元,非常廣泛地應(yīng)用于變頻器、直流伺服、交流伺服等系統(tǒng)的閉環(huán)控制中。為了減小體積,絕對(duì)式編碼器一般采用串行通信方式輸出絕對(duì)編碼,針對(duì)伺服電機(jī)控制等高端場(chǎng)合,為了滿足快速的電流環(huán)、速度環(huán)、位置環(huán)的控制需要,編碼輸出的速度又應(yīng)該非常快,這些不利因素都對(duì)絕對(duì)式編碼的接收增加了難度。

絕對(duì)式編碼器廠家大多為其編碼器配套了接收芯片,實(shí)現(xiàn)串行編碼到并行編碼的轉(zhuǎn)換,便于控制器的讀取操作。但是此類芯片通常價(jià)格比較昂貴,大約占絕對(duì)式編碼器價(jià)格的四分之一。目前國(guó)內(nèi)外高端交流伺服系統(tǒng)中普遍采用FPGA+DSP結(jié)構(gòu)。DSP用來實(shí)現(xiàn)矢量變換和其它算法流程;FPGA用以實(shí)現(xiàn)譯碼、A、B、 Z信號(hào)輸出、I/O擴(kuò)展等功能,F(xiàn)PGA中尚有很多資源沒有得到充分利用。本文研制了一種用于交流伺服系統(tǒng)中的基于FPGA的絕對(duì)式編碼器智能接口,實(shí)現(xiàn)與絕對(duì)式編碼器的雙工通信,接收高速數(shù)據(jù)流,同時(shí)在FPGA內(nèi)部開辟RAM空間,將收到的編碼器數(shù)據(jù)存入RAM中,DSP可以以訪問內(nèi)存的方式讀取數(shù)據(jù),提高了工作速度。同時(shí),該接口還具有奇偶校驗(yàn)等糾錯(cuò)功能,完全可以替代廠家提供的接收芯片,大幅度降低了產(chǎn)品成本。

1 RCN226型絕對(duì)式編碼器

國(guó)內(nèi)外絕對(duì)式編碼器生產(chǎn)廠商很多,如日本的多摩川精機(jī)、德國(guó)的海德漢、國(guó)產(chǎn)的長(zhǎng)春三峰等。其中海德漢的RCN226型絕對(duì)式編碼器采用的是海德漢公司專用的EnDat2.2一位置編碼器雙向數(shù)字接口,它傳輸?shù)臄?shù)據(jù)類型分為位置值、位置值及附加信息或參數(shù)。發(fā)送的信息類型由模式指令選擇。模式指令決定被發(fā)送信息的內(nèi)容。每個(gè)模式指令包括三個(gè)位。為確保可靠發(fā)送信息,每個(gè)位均采用冗余發(fā)送(反相或兩次)。其發(fā)送位置值的模式指令為"000111"。信號(hào)傳輸格式如圖1所示。

數(shù)據(jù)包發(fā)送與數(shù)據(jù)傳輸同步。傳輸周期從第一個(gè)時(shí)鐘下降沿開始。編碼器保存測(cè)量值并計(jì)算位置值。兩個(gè)時(shí)鐘周期后,后續(xù)電子設(shè)備發(fā)送模式指令。編碼器發(fā)送位置值后,從起始位開始由編碼器向后續(xù)電子設(shè)備傳輸數(shù)據(jù)。后續(xù)"錯(cuò)誤位"-"錯(cuò)誤1"和"錯(cuò)誤2"是檢測(cè)類信號(hào),用于監(jiān)測(cè)故障。這兩個(gè)信號(hào)相互獨(dú)立地生成,它表示編碼器發(fā)生可導(dǎo)致不正確位置值的故障。發(fā)生故障的確切原因保存在"工作狀態(tài)"存儲(chǔ)器中,并可被詳細(xì)地查詢。然后編碼器從最低有效位(LSB)開始發(fā)送絕對(duì)位置值。其長(zhǎng)度取決于所用的編碼器,RCN226的絕對(duì)位置值為26位。位置值的數(shù)據(jù)發(fā)送以循環(huán)冗余校驗(yàn)(CRC)結(jié)束。在數(shù)據(jù)字結(jié)尾處,必須將時(shí)鐘信號(hào)置為高電平。10至30 μ s后或1.25至3.75 μ s后(系統(tǒng)時(shí)鐘大于1MHz時(shí))數(shù)據(jù)線返回低電平。然后,時(shí)鐘信號(hào)啟動(dòng)另一次數(shù)據(jù)發(fā)送。

2 絕對(duì)式編碼器接口的實(shí)現(xiàn)

全數(shù)字化交流伺服系統(tǒng)中采用TMS320X2812作為控制器,用以實(shí)現(xiàn)位置環(huán)、速度環(huán)和電流環(huán)以及SVPWM、電壓和電流采樣等功能。此外,采用Altera公司的型號(hào)為FP1C6的~Cyclone系列FPGA,用以實(shí)現(xiàn)與絕對(duì)式碼盤接口、譯碼邏輯等功能。同時(shí),在FPGA內(nèi)部實(shí)現(xiàn)了256字節(jié)的雙口RAM,用來與DSP之間通過總線實(shí)現(xiàn)數(shù)據(jù)傳輸。FPGA部分的功能框圖如圖2P所示。

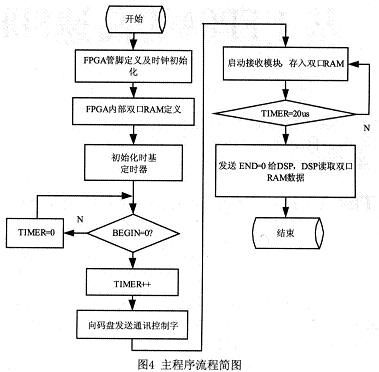

碼盤接口部分分為發(fā)送模塊、接收模塊、雙口RAM模塊、主程序模塊四部分。由于每次通信時(shí)間是嚴(yán)格固定的,設(shè)系統(tǒng)時(shí)鐘為2MHz。FPGA為主叫,向編碼器發(fā)送"請(qǐng)求數(shù)據(jù)"控制字共6位,需時(shí)3 μs,編碼器向FPGA共發(fā)送1個(gè)起始位、兩個(gè)"錯(cuò)誤位"、26位位置值和5位CRC校驗(yàn)位,共34位的數(shù)據(jù)共需時(shí)17 μs,所以每次通信需要20 μs的時(shí)間,并且每個(gè)時(shí)刻具體需要傳遞哪一位數(shù)據(jù)也是嚴(yán)格確定的。因此采用基于時(shí)基的設(shè)計(jì)方法。

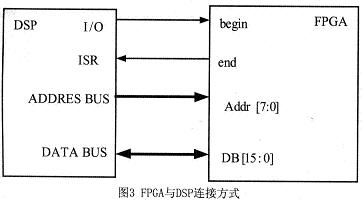

FPGA內(nèi)部設(shè)計(jì)了一個(gè)時(shí)基為20ns的計(jì)數(shù)器,每20ns加1,作為整個(gè)電路的時(shí)基,根據(jù)這個(gè)時(shí)基來確定每一時(shí)刻收到的數(shù)據(jù)具體屬于哪個(gè)位。在FPGA 內(nèi)部實(shí)現(xiàn)了256bytes的雙口RAM空問,A口具有8位數(shù)據(jù)線,8位地址線,用于與編碼器通信,B口具有16位數(shù)據(jù)線,8位地址線,用于與DSP通信,因?yàn)門MS320X2812為16位DSP,所以與FPGA中RAM的數(shù)據(jù)傳遞極為方便。

DSP在每個(gè)電流環(huán)周期發(fā)送一個(gè)有效的"begin"信號(hào),20μs之后,碼盤信號(hào)接收模塊將接收到的數(shù)據(jù)存入FPGA內(nèi)部雙口RAM的A口中,并按順序排列成16位數(shù)據(jù)的形式,然后向DSP發(fā)送end信號(hào),表示一次通信結(jié)束,DSP接收到中斷之后從FPGA的雙口RAM的B口中讀取數(shù)據(jù),完成一次通信, DSP的連接如圖3所示。

在本接口的研發(fā)過程中,對(duì)FPGA的開發(fā)采用Altera公司的Quartus II 5.1集成環(huán)境,硬件描述語言為VHDL語言。圖4為主程序流程圖。

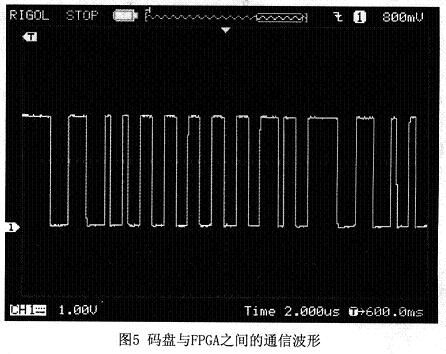

圖5為碼盤與FPGA之間的通信波形,從位置信號(hào)可以看出該接口工作正常。

3 結(jié)束語

本文設(shè)計(jì)了一種基于FPGA的絕對(duì)式碼盤智能接口,用以進(jìn)行絕對(duì)式編碼器和伺服驅(qū)動(dòng)器DSP處理器之間的通信。并且具CRC校驗(yàn)等糾錯(cuò)功能。該接口基本可以替代價(jià)格昂貴的專用接口芯片,降低產(chǎn)品的成本,促進(jìn)伺服電機(jī)驅(qū)動(dòng)器的國(guó)產(chǎn)化進(jìn)程。