1 引言

在信號(hào)處理領(lǐng)域,DSP技術(shù)的應(yīng)用越來越廣泛,基于DSP的信號(hào)采集處理平臺(tái)不斷出現(xiàn)。常見的DSP信號(hào)采集處理平臺(tái)利用總線進(jìn)行數(shù)據(jù)采集,總線上多個(gè)設(shè)備的數(shù)據(jù)傳輸經(jīng)常相互沖突。ADI公司的Tiger SHARCl01型DSP(簡稱TSl01)只有總線和鏈路口可以與外設(shè)通信,基于緩解總線沖突的目的,筆者設(shè)計(jì)了一種以現(xiàn)場可編程門陣列(FPGA)作為數(shù)據(jù)接口緩沖器,避開總線,經(jīng)TSl01的鏈路口將多個(gè)A/D轉(zhuǎn)換器采集到的數(shù)據(jù)傳送到TSl01。由FPGA完成多個(gè)多路A/D轉(zhuǎn)換器采集數(shù)據(jù)的緩沖排序,并形成符合TSl01鏈路口傳輸協(xié)議的數(shù)據(jù)流,送到TSl01的鏈路口。該設(shè)計(jì)實(shí)現(xiàn)了鏈路口與其他非鏈路口外部設(shè)備的通信。減少了TSlOl總線上的數(shù)據(jù)傳輸量,緩解了總線競爭的問題。

2 ADS8361型A/D轉(zhuǎn)換器

ADS8361是TI公司生產(chǎn)的雙通道、四路、模擬差分輸入、16 bit同步采樣串行A/D轉(zhuǎn)換器。4路模擬差分輸入分成2組,每組各有1個(gè)A/D轉(zhuǎn)換模塊,可同時(shí)采樣;對(duì)每個(gè)輸入最快可以實(shí)現(xiàn)500 ks/s的采樣率,即2 μs就完成1次A/D采樣。采樣后的數(shù)據(jù)由串行接口輸出,這對(duì)于具備同步串行接口的大多數(shù)DSP是非常有用的,DSP的總線可以掛接多種其他設(shè)備,在高速連續(xù)采樣的過程中,DSP的串口和總線可以互不影響地獨(dú)立工作。

ADS8361在采樣頻率率為50 kHz時(shí),有80 dB的共模抑制,這在強(qiáng)噪聲環(huán)境中非常重要。ADS8361需要模擬電壓和數(shù)字電壓分別供電,考慮到與外部電路的匹配,所以模擬部分選擇5 V供電,數(shù)字部分與DSP的I/O電壓一致,選擇3.3 V供電。工作時(shí)既可以使用內(nèi)部2.5 V參考電壓,也可以由外部提供參考電壓。差分模擬輸入信號(hào)的電壓范圍為±2.5V。ADS8361采用SSOP-24封裝。CS引腳是ADS8361的片選;Ml、M0、AO引腳用于選擇采樣通道和數(shù)據(jù)通道;RD引腳為讀取數(shù)據(jù)引腳,CONVST引腳是A/D轉(zhuǎn)換脈沖,在使用中應(yīng)將RD與CON-VST引腳相連;CLOCK引腳用于輸入采樣時(shí)鐘(與下文中FPGA輸出的ADCLK相連);2個(gè)通道的數(shù)據(jù)輸出引腳分別為SERIAL DATA A和SERIALDATA B,每次轉(zhuǎn)換輸出16 bit數(shù)據(jù)。ADS8361的工作時(shí)鐘最大值為10MHz,高電平和低電平至少各40 ns。

3 TSl01的鏈路口及傳輸方式

TSl01是高性能128 bit浮點(diǎn)數(shù)字信號(hào)處理器,其運(yùn)算能力很強(qiáng)(18億次/秒),而外部總線吞吐能力相對(duì)不足(若外部頻率為100 MHz,則外部總線傳輸速度為800 MB/s),當(dāng)外設(shè)較多時(shí)很容易形成I/O瓶頸。不過它有四個(gè)高速鏈路口,每個(gè)鏈路口的傳輸速度極限為250 MB/s,適合TSl01之間的點(diǎn)對(duì)點(diǎn)高速傳輸,也可與其相同協(xié)議的外設(shè)通信,從而大大緩解了總線壓力。

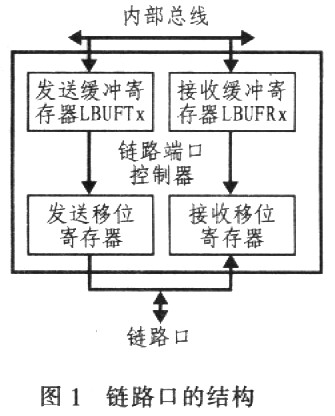

TSl01的每個(gè)鏈路口由發(fā)送器和接收器兩部分組成,每部分都有128 bit的移位寄存器和128 bit的緩沖寄存器,其結(jié)構(gòu)如圖l所示。每個(gè)鏈路口均有8 bit數(shù)據(jù)線和LxCLKIN、LxCLKOUT和LxDIR(x為鏈路口序號(hào)0-3)3個(gè)控制引腳,可支持多片TSl01處理器間點(diǎn)對(duì)點(diǎn)的雙向數(shù)據(jù)傳送,也可以用于與外部設(shè)備進(jìn)行數(shù)據(jù)傳輸。其中LxDIR用來指示鏈路口的數(shù)據(jù)流向。LxCLKIN和LxCLKOUT為鏈路口的時(shí)鐘/確認(rèn)握手信號(hào)。發(fā)送數(shù)據(jù)時(shí),LxCLKOUT為時(shí)鐘信號(hào),LxCLKIN為確認(rèn)信號(hào);接收數(shù)據(jù)時(shí),LxCLKIN為時(shí)鐘信號(hào),LxCLKOUT為確認(rèn)信號(hào)。發(fā)送數(shù)據(jù)時(shí),首先傳輸4字?jǐn)?shù)據(jù)到鏈路發(fā)送緩沖寄存器LBUFTx,再將其復(fù)制到移位寄存器(若移位寄存器為空,此時(shí)LBUFTx可被寫入新的數(shù)據(jù)),然后以字節(jié)的形式發(fā)送(先發(fā)送低字節(jié)),每個(gè)字節(jié)在鏈路時(shí)鐘的上升沿和下降沿被驅(qū)動(dòng)和鎖存。接收器的移位寄存器為空時(shí),系統(tǒng)將開始接收發(fā)送方傳輸?shù)臄?shù)據(jù)并將其送入移位寄存器,同時(shí)驅(qū)動(dòng)LxCLKOUT為低電平。當(dāng)整個(gè)4字接收完畢后,如果接收緩沖寄存器LBUFRx為空,系統(tǒng)會(huì)將4字?jǐn)?shù)據(jù)從移位寄存器復(fù)制到LBUFRx,并在數(shù)據(jù)被復(fù)制后驅(qū)動(dòng)其Lx-CLKOUT為高電平,以告訴發(fā)送方接收緩沖寄存器為空,可以準(zhǔn)備接收新數(shù)據(jù)。發(fā)送方檢測到Lx-CLKIN為高電平后立即進(jìn)行下次傳輸。

常見的啟動(dòng)鏈路傳輸數(shù)據(jù)的方法有二種:利用TSl01的IRQ中斷啟動(dòng)和利用鏈路中斷啟動(dòng)。鏈路傳輸以DMA方式進(jìn)行,DMA方式是在TSl01內(nèi)核不干預(yù)的情況下,后臺(tái)通過鏈路口高速傳送數(shù)據(jù)的機(jī)制。從外部設(shè)備向鏈路口傳送數(shù)據(jù),實(shí)際上是鏈路口把外部設(shè)備送來的數(shù)據(jù)自動(dòng)保存到TSlOl的內(nèi)、外存儲(chǔ)器中,也可以經(jīng)其他鏈路口轉(zhuǎn)發(fā)出去。對(duì)鏈路口及其DMA寄存器進(jìn)行正確的設(shè)置后就可以設(shè)置TCB塊。DMA啟動(dòng)后,一旦鏈路緩沖器未滿,它將向外部設(shè)備請(qǐng)求數(shù)據(jù)。這時(shí),如果DMA可以占用內(nèi)部或外部數(shù)據(jù)總線,那么,系統(tǒng)便可將數(shù)據(jù)從鏈路口傳送到存儲(chǔ)器中。

4 數(shù)據(jù)采集的硬件設(shè)計(jì)

TSIOI是運(yùn)算能力強(qiáng)但與外部連接資源相對(duì)少的一類DSP,在多個(gè)TSl01級(jí)連的系統(tǒng)中,如果利用總線進(jìn)行數(shù)據(jù)采集,A/D轉(zhuǎn)換器通常需要長時(shí)間占用總線,會(huì)經(jīng)常出現(xiàn)爭占總線的問題,從而導(dǎo)致信號(hào)采集處理出現(xiàn)總線瓶頸,利用鏈路口進(jìn)行數(shù)據(jù)采集可以很大程度地釋放總線資源。本應(yīng)用中需要對(duì)10路模擬信號(hào)同時(shí)進(jìn)行500 kHz的采樣,傳輸?shù)臄?shù)據(jù)率為lOx0.5 MBx2=10 MB/s<250 MB/s。

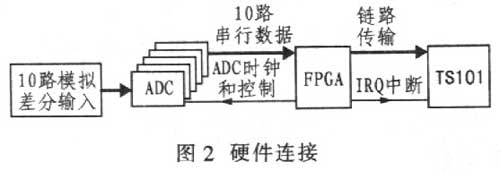

TSl01通過FPGA進(jìn)行數(shù)據(jù)采集,它的鏈路口作為數(shù)據(jù)輸入口。它們的連接結(jié)構(gòu)如圖2所示,將鏈路口的LxCLKIN直接和FPGA連接,由FPGA驅(qū)動(dòng),在FPGA向鏈路口傳送數(shù)據(jù)時(shí)作為鏈路口的時(shí)鐘輸入。LxDIR和LxCLKOUT可以懸空,鏈路口的8條數(shù)據(jù)線接到FPGA上。

設(shè)計(jì)中將每個(gè)A/D轉(zhuǎn)換器的M1、NO、A0引腳接地,僅取用每個(gè)A/D轉(zhuǎn)換器的2個(gè)模擬差分輸入——AO和B0通道,2個(gè)通道可以在2μs之內(nèi)同時(shí)完成1次采樣。本

設(shè)計(jì)共用5個(gè)ADS8361級(jí)連以擴(kuò)充模擬輸入通道,實(shí)現(xiàn)10個(gè)模擬通道輸入,每個(gè)ADS8361的RD與CONVST連接,由FPGA進(jìn)行控制,5個(gè)ADS8361同時(shí)進(jìn)行A/D轉(zhuǎn)換,轉(zhuǎn)換后在FPGA內(nèi)同時(shí)完成串并轉(zhuǎn)換,把轉(zhuǎn)換后的并行數(shù)據(jù)先鎖存在FPGA內(nèi)部,再將各通道按先低字節(jié)后高字節(jié)依次傳送到TSl01的鏈路口。

5 數(shù)據(jù)采集的軟件設(shè)計(jì)

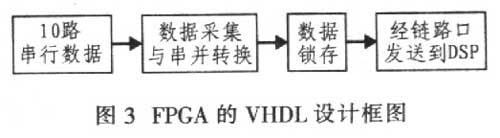

軟件部分包括TSl01軟件設(shè)計(jì)和FPGA軟件設(shè)計(jì),F(xiàn)PGA軟件設(shè)計(jì)采用VHDL實(shí)現(xiàn)。其結(jié)構(gòu)如圖3所示。

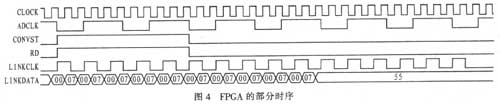

FPGA的主要操作是將5個(gè)ADS8361的10路串行采集數(shù)據(jù)轉(zhuǎn)換成20個(gè)8 bit數(shù)據(jù),再將數(shù)據(jù)鎖存,同時(shí)產(chǎn)生鏈路時(shí)鐘,將鎖存后的數(shù)據(jù)發(fā)送到TSl01鏈路口。需要實(shí)現(xiàn)的時(shí)序如圖4所示,其中CLOCK是TSlOl外部時(shí)鐘,ADCLK是ADS8361的工作時(shí)鐘,是CLDCK的5分頻,占空比為60%,CONVST與RD相連接,LINKCLK是鏈路時(shí)鐘,LINKDATA是鏈路數(shù)據(jù)。

使用鏈路傳輸時(shí),TSl01在鏈路時(shí)鐘的上升沿和下降沿都鎖存數(shù)據(jù),20個(gè)8 bit數(shù)據(jù)需要lO個(gè)鏈路脈沖,而鏈路口每次至少需要傳輸128 bit的數(shù)據(jù),即至少需要8個(gè)脈沖,且發(fā)送數(shù)據(jù)需要的脈沖數(shù)必須為8的倍數(shù)。所以設(shè)計(jì)中每次通過鏈路發(fā)送數(shù)據(jù)的脈沖數(shù)為16個(gè),前10個(gè)傳輸A/D轉(zhuǎn)換器采集到的數(shù)據(jù),其后的6個(gè)脈沖發(fā)送0x55。發(fā)送到鏈路的數(shù)據(jù)是A/D轉(zhuǎn)換器上次轉(zhuǎn)換的結(jié)果。TSl01可以設(shè)置鏈路口工作時(shí)鐘為內(nèi)核時(shí)鐘的2、3、4、8分頻,設(shè)計(jì)中TSl01外部時(shí)鐘CLOCK是50MHz,內(nèi)核時(shí)鐘是CLOCK的5倍頻即250 MHz,鏈路口接收數(shù)據(jù)時(shí)FPGA給TSIOI的鏈路時(shí)鐘LINKCLK是25 MHz TSl01鏈路口工作時(shí)鐘應(yīng)盡量接近鏈路時(shí)鐘LINKCLK,所以設(shè)置TSl01鏈路口工作時(shí)鐘為內(nèi)核時(shí)鐘的8分頻即31.25 MHz。

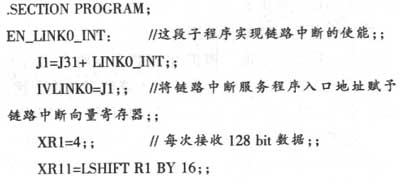

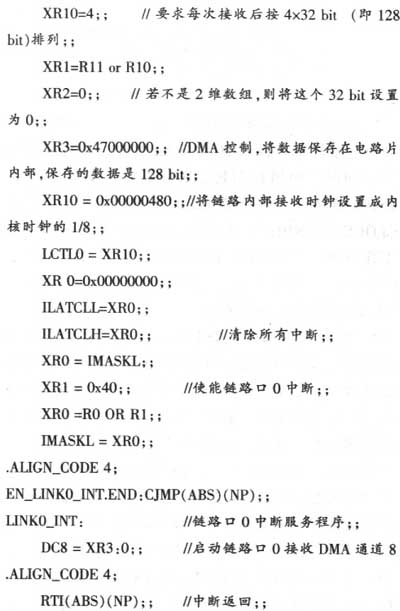

系統(tǒng)采用鏈路中斷方式接收FPGA送來的數(shù)據(jù),鏈路中斷方式數(shù)據(jù)接收的程序如下:

6 A/D轉(zhuǎn)換器電路的設(shè)計(jì)和使用

設(shè)計(jì)高精度A/D轉(zhuǎn)換器的關(guān)鍵是保證有效位數(shù),ADS8361的輸入動(dòng)態(tài)范圍為:±2.5 V,每個(gè)量化單位對(duì)應(yīng)0.076 mV,因此應(yīng)設(shè)法降低噪聲和干擾。噪聲和干擾的來源主要有二種:一種是A/D轉(zhuǎn)換器自身的噪聲如量化噪聲等,另一種是周圍電路產(chǎn)生的噪聲干擾。前者是A/D轉(zhuǎn)換器固有的,后者的大小遠(yuǎn)遠(yuǎn)超過前者,特別是電源、模擬/電路數(shù)字電路之間的干擾。ADS8361的差分輸入方式大大降低了共模干擾。設(shè)計(jì)中主要考慮如何在電路中減少其他噪聲和干擾。

電源設(shè)計(jì)是抑制噪聲的關(guān)鍵,本文介紹的設(shè)計(jì)具有多種電壓(模擬5 V、-5 V和數(shù)字3.3 V、1.2V等)并且是混合模擬和數(shù)字信號(hào)的板級(jí)設(shè)計(jì),選擇合適的電源電路,合理地進(jìn)行電源層和地層的切割是很重要的。開關(guān)電源具有體積小、效率高、輸出穩(wěn)定等優(yōu)點(diǎn),同時(shí)能夠很好地解決TSlOl的上電次序問題,但紋波明顯。開關(guān)頻率越高輸出電壓紋波越小,電路中選用的電感器在10μH~200 μH為宜,電路中可以使用ESR小、容值大的電容器構(gòu)成去耦電路,同時(shí)在板上放置多種電容器進(jìn)行濾波。

減少數(shù)字信號(hào)干擾也可以有效提高A/D轉(zhuǎn)換器的精度,布板和布線時(shí)要使ADS8361模擬差分信號(hào)輸入?yún)^(qū)域盡量遠(yuǎn)離數(shù)字信號(hào),F(xiàn)PGA設(shè)計(jì)中盡量避免多個(gè)信號(hào)電平同時(shí)翻轉(zhuǎn),同時(shí)給A/D轉(zhuǎn)換器提供良好的工作時(shí)鐘,應(yīng)使用串聯(lián)終端法,串聯(lián)1只小電阻器可以很好減少時(shí)基抖動(dòng),時(shí)鐘信號(hào)進(jìn)入A/D轉(zhuǎn)換器的布線越短越好,同時(shí)不要離數(shù)字信號(hào)太近,也不要靠近模擬區(qū),否則會(huì)增加模擬區(qū)的噪聲。同時(shí)要注意單點(diǎn)共地,在共地的點(diǎn)上串接1個(gè)磁珠。設(shè)計(jì)中使用了多層板布局,在輕載情況下可以將輸出電壓紋波減到4mV。

7 結(jié)束語

筆者設(shè)計(jì)一種通過TSl01鏈路口進(jìn)行多A/D轉(zhuǎn)換器多通道高精度數(shù)據(jù)采集的實(shí)現(xiàn)方法,在DSP信號(hào)采集處理系統(tǒng)中可以不占用總線,實(shí)現(xiàn)并行數(shù)據(jù)傳輸和處理,有更高的實(shí)時(shí)性,同時(shí)探討了如何提高A/D轉(zhuǎn)換器精度的問題。該設(shè)計(jì)方法已經(jīng)應(yīng)用于多種并行和串行A/D轉(zhuǎn)換電路中,具有通用性。