-蔣修國/文-

過孔的應(yīng)用場景非常多,過孔的結(jié)構(gòu)也是相當(dāng)復(fù)雜,在寫《ADS信號完整性仿真與實戰(zhàn)》一書時,用了一整章介紹了過孔。如下是過孔的一張簡化結(jié)構(gòu)圖:

其中就包括了過孔的殘樁Stub。

通常,在普通設(shè)計高多層板的時候,工程師都是想著把高速信號線或者射頻線設(shè)計在內(nèi)層(帶狀線)或者外層(微帶線)好就行,而不考慮到底是布線在內(nèi)層的第幾層,認(rèn)為帶狀線性能都是一樣的。

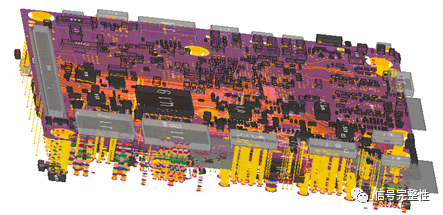

其實并不是如此的,就近期我們處理的一個案例來講,原本其設(shè)計如下圖所示:

經(jīng)過仿真之后,得到的插入損耗和回波損耗的結(jié)果如下圖所示:

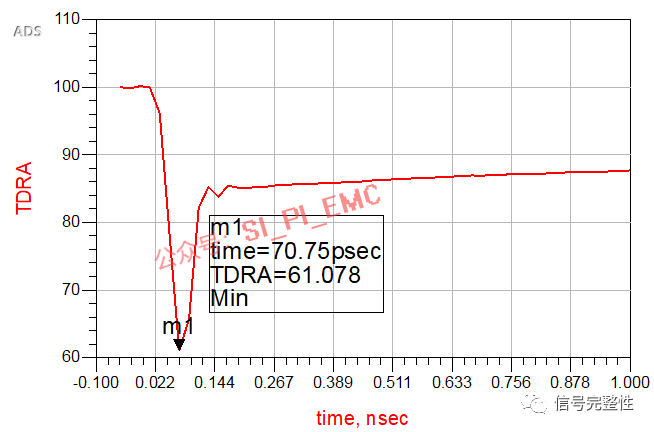

從上面的結(jié)果可以看到,不管是插入損耗還是回波損耗都非常差。再查看其阻抗,如下圖所示:

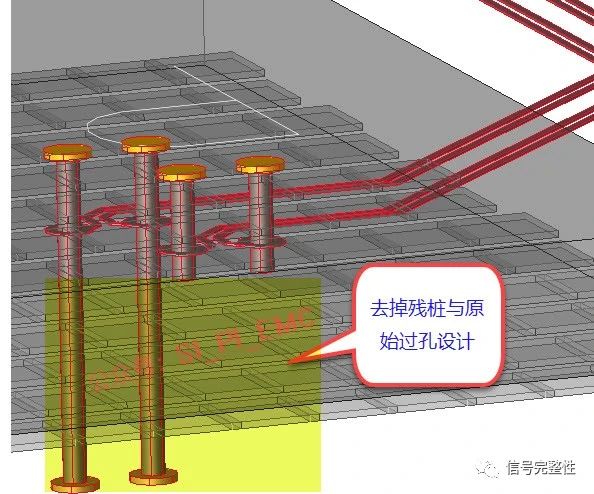

從上圖可以看到,其阻抗只有61ohm。以上的設(shè)計中,殘樁最大值達(dá)到了72mil。按照生產(chǎn)工藝,在仿真軟件ADS中把過孔的殘樁去掉之后,如下圖所示:

獲得的仿真結(jié)果與原始的對比如下圖所示:

顯然,去掉殘樁之后,插入損耗和回波損耗都得到了很好的改善。在14GHz左右,插入損耗相差約40dB,回波損耗也相差了約13dB。這對于高速信號的設(shè)計影響非常的大。再對比下其阻抗,如下圖所示:

兩個設(shè)計的過孔阻抗相差了約20ohm。

下面從大家比較熟知的眼圖,也可以看到一些結(jié)果上的差異:

上圖是按照16Gbps的信號速率獲得的眼圖結(jié)果,顯然,存在很大殘樁時,其眼圖完全閉合,而去掉殘樁之后,其眼圖張開了。

所以,過孔殘樁會直接影響到信號傳輸?shù)男阅埽こ處熢谠O(shè)計時要重視過孔殘樁的存在。在信號速率比較高,且殘樁比較長時,在PCB生產(chǎn)時,要考慮在過孔處使用Backdrill工藝,或者使用盲埋孔。當(dāng)然,并不是每一類設(shè)計都要使用Backdrill工藝或者盲埋孔,因為它們都會帶來成本上的增加。