隨著數(shù)據(jù)帶寬需求的持續(xù)增長(zhǎng),數(shù)據(jù)傳輸從并行變成串行,收發(fā)器的速率越來(lái)越高,無(wú)論在單板內(nèi)或者通過(guò)光纖和背板傳輸,都會(huì)帶來(lái)一系列信號(hào)完整性問(wèn)題。信號(hào)完整性,是指系統(tǒng)電路在信號(hào)傳輸過(guò)程中保持信號(hào)時(shí)域和頻域特性的能力。如果信號(hào)經(jīng)過(guò)信號(hào)線傳輸后依舊能保持其正確的功能特性,即信號(hào)在電路中能以正確的時(shí)序、幅度、相位等做出相應(yīng)的動(dòng)作,就表明該電路有較好的信號(hào)完整性。反之,就是信號(hào)完整性是有一定的問(wèn)題的。信號(hào)完整性問(wèn)題如何解決,如何保證誤碼率滿足協(xié)議要求,從芯片選型、電路設(shè)計(jì),再到PCB Layout的全過(guò)程都需要考慮。

一、高速Serdes信號(hào)完整性的問(wèn)題和影響

1、高速Serdes信號(hào)完整性的問(wèn)題

通常電信號(hào)在PCB上傳輸?shù)臅r(shí)候主要涉及兩個(gè)方面反射和插入損耗設(shè)計(jì)要求考量。

a、反射

反射是指在電信號(hào)傳輸時(shí),每一時(shí)刻都會(huì)遇到一個(gè)傳輸線的瞬時(shí)阻抗,當(dāng)該瞬時(shí)阻抗發(fā)生變化時(shí),一部分信號(hào)將會(huì)反射,另一部分將會(huì)繼續(xù)向前傳輸;或者說(shuō)反射就是回波,信號(hào)功率的一部分傳輸?shù)骄€上并達(dá)到負(fù)載端,但是有一部分反射會(huì)回到源端。

反射主要是由阻抗不匹配和stub引起的。例如線寬不一樣,就會(huì)引起阻抗不匹配,信號(hào)傳輸中經(jīng)過(guò)的耦合電容、過(guò)孔等位置都是會(huì)引起阻抗不匹配。

b、插入損耗

插入損耗是由介質(zhì)損耗、導(dǎo)體損耗、導(dǎo)體表面粗糙度等原因引起來(lái)的損耗。不同的介質(zhì)具備不同的插入損耗。背板設(shè)計(jì)的時(shí)候通常采用M4/M6板材取代FR4板材,雖然M4/M6板材成本也比較高也會(huì)比較貴,但是對(duì)應(yīng)插入損耗遠(yuǎn)遠(yuǎn)優(yōu)于FR4板材。

2、高速Serdes信號(hào)完整性的問(wèn)題影響

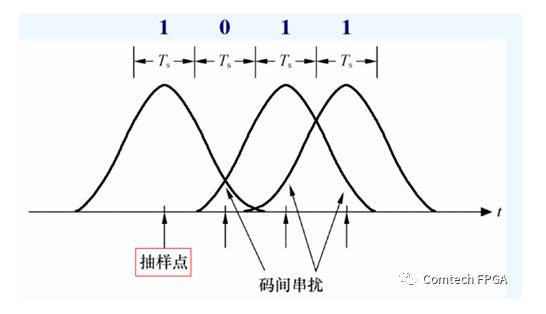

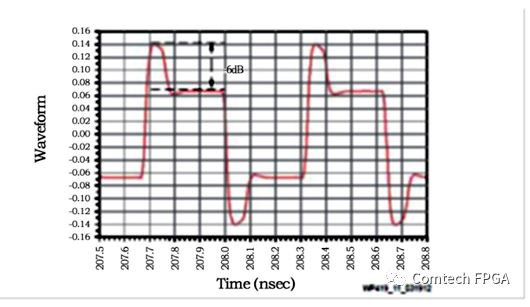

我們發(fā)送的數(shù)據(jù)有高中低等多種頻率,其中信號(hào)頻率越高,插入損耗就越大。信號(hào)經(jīng)過(guò)線路的傳輸,高頻成分被衰減得更多,會(huì)導(dǎo)致碼間干擾的產(chǎn)生。 碼間干擾,又稱ISI(Intersymbol interference),顧名思義是不同信號(hào)(碼元)之間的干擾。碼間干擾造成的后果是前一個(gè)bit的波形延伸到了后一個(gè)bit位置。在發(fā)送側(cè)我們發(fā)送的bit是0-1-1-0,經(jīng)過(guò)傳輸后最后一個(gè)1的波形延伸到后面一個(gè)0的位置,會(huì)造成0的電壓變高,判決時(shí)候可能判決成1,這樣本來(lái)發(fā)送的0-1-1-0,在接收端判決成0-1-1-1。這就是碼間干擾。碼間干擾的主要原因就是高頻成分損耗大,低頻成分損耗小。

圖一 碼間干擾

二、AMD-XilinxFPGA解決傳輸中的信號(hào)完整性方案

AMD-Xilinx FPGA在發(fā)送端使用了輸出擺幅、預(yù)加重、去加重等技術(shù),其中輸出擺幅通常是用來(lái)增加信號(hào)的幅度;在接收端使用了均衡技術(shù)。

1、預(yù)加重后加重技術(shù)

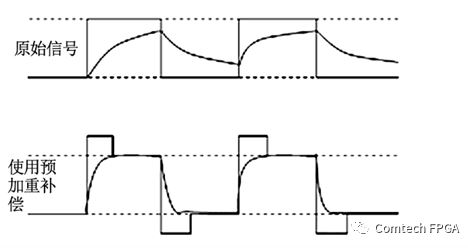

為便于信號(hào)的傳輸,而對(duì)某些頻譜分量的幅值相對(duì)于其他分量的幅值預(yù)先有意予以增強(qiáng)的措施。 預(yù)加重是在電平轉(zhuǎn)換開(kāi)始前有意過(guò)量驅(qū)動(dòng)。信號(hào)傳輸線表現(xiàn)出來(lái)的是低通濾波器特性,傳輸過(guò)程中信號(hào)的高頻成分衰減大,低頻部分衰減小,預(yù)加重技術(shù)的思想就是在傳輸新的始端增強(qiáng)信號(hào)的高頻成分,以補(bǔ)償高頻分量在傳輸過(guò)程中的過(guò)大衰減。信號(hào)的高頻分量主要出現(xiàn)在信號(hào)的上升沿和下降沿處,預(yù)加重技術(shù)就是增強(qiáng)信號(hào)上升沿和下降沿的幅度。

圖二 預(yù)加重信號(hào)變化

我們從時(shí)域上看去加重對(duì)波形的影響,看上去波形更奇怪一些,所以去加重有些像無(wú)線通訊中的一個(gè)術(shù)語(yǔ)“預(yù)失真”。

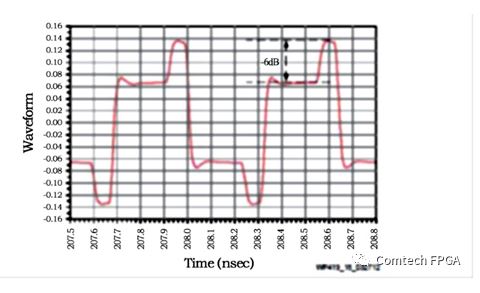

圖三 預(yù)加重時(shí)域波形

圖四 后加重時(shí)域波形

我們可以看到pre-cursor和post-cursor處理的位置不同。預(yù)加重是在信號(hào)變化前處理,后加重是在信號(hào)變化后處理。

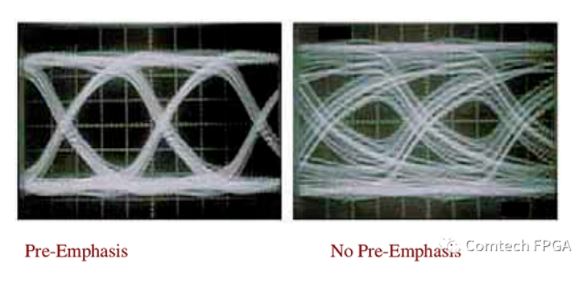

圖五 使用預(yù)加重前后眼圖對(duì)比

從圖中我們可以看到,左邊是經(jīng)過(guò)去加重的接收眼圖,右邊是沒(méi)有經(jīng)過(guò)去加重的接收眼圖。我們可以看到眼圖的“眼睛”變得更大了。

2、 接收均衡技術(shù)

對(duì)于GTX/GTH收發(fā)器,基于系統(tǒng)級(jí)的功耗和性能的權(quán)衡,有兩種類型的自適應(yīng)濾波可用:

·功耗優(yōu)化和低通道損耗的低功耗模式LPM

·均衡更低損耗通道的判決反饋均衡模式DFE

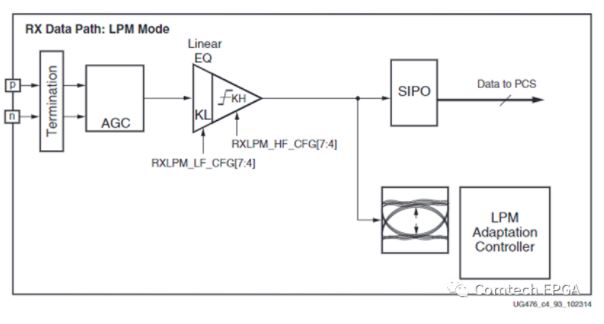

a、LPM

LPM模式下應(yīng)用接收的線性濾波器,可衰減低頻信號(hào)分量,放大奈奎斯特頻率附近的分量,并衰減更高頻率,這樣就抵消了通道的低通特性。

圖六 Serdes LPM Mode

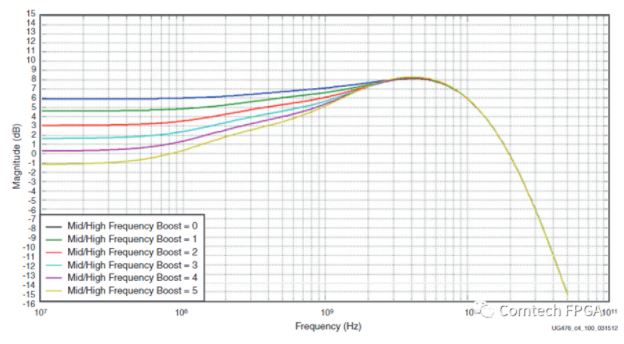

可以調(diào)整連續(xù)時(shí)間線性均衡增益以優(yōu)化低頻衰減與高頻放大的比率。缺點(diǎn)則是放大高頻分量的同時(shí)噪聲和串?dāng)_也被放大。

在GT Wizard中選擇LPM 模式參數(shù)已經(jīng)是自動(dòng)調(diào)整模式,不需要我們?nèi)ピO(shè)置。

LPM模式的功耗比DFE模式小10%-15%,在通道損耗小于12db時(shí)候建議使用LPM模式。板內(nèi)互聯(lián)情況下通道衰減基本上都小于12db,使用LPM模式是一個(gè)比較好的的選擇。

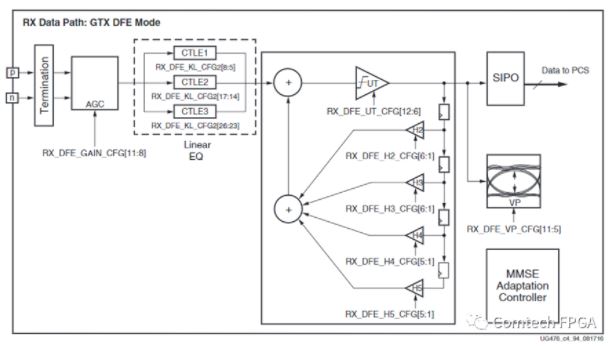

圖七 AMD-Xilinx FPGA 線性均衡響應(yīng)曲線 b、DFE DFE模式通過(guò)提供更接近的調(diào)整濾波器參數(shù),提供更好的傳輸通道補(bǔ)償。但是,DFE模式不能移除發(fā)送bit的預(yù)加重,只能補(bǔ)償post-cursor。線性均衡GTX/GTH RX DFE模式是一個(gè)離散時(shí)間自適應(yīng)高通濾波器,該濾波器系數(shù)TAP由自適應(yīng)算法設(shè)置。

圖八 AMD-Xilinx FPGA Serdes DFE Mode

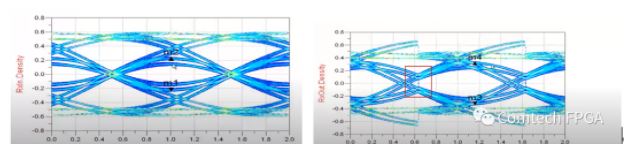

圖九 使用DFE前后對(duì)比

左圖不使用DFE均衡,右圖是使用DFE均衡后,眼圖張開(kāi)的比左圖要大,紅圈位置是數(shù)據(jù)的變化沿,DFE延遲0.5個(gè)UI,因此在下一個(gè)數(shù)據(jù)的跳變沿就開(kāi)始減去前一個(gè)bit帶來(lái)的影響,而不是只在數(shù)據(jù)的采樣位置才作用,這樣眼圖都變大了,所以DFE的眼圖看起來(lái)有不連續(xù)性。

c、LPM和DFE模式的選擇

DFE模式推薦用于中長(zhǎng)距離應(yīng)用,在奈奎斯特頻率下的信道損耗為8dB或者以上。DFE和CTLE相比不會(huì)放大噪聲和串?dāng)_,數(shù)據(jù)經(jīng)過(guò)衰減很大的通道后接收的數(shù)據(jù)信號(hào)幅度已經(jīng)很小了,這個(gè)時(shí)候高頻的噪聲和串?dāng)_對(duì)信號(hào)影響就會(huì)很大。 目前DFE的參數(shù)在FPGA中都是算法自動(dòng)調(diào)整,不需要我們?nèi)ピO(shè)置。在使用8B10B編碼的協(xié)議而且數(shù)據(jù)沒(méi)有加擾的情況下,如果線路上長(zhǎng)時(shí)間發(fā)送固定碼型會(huì)使得DFE自動(dòng)調(diào)整算法漂移,引起負(fù)面效果。因此在8B/10B編碼而且數(shù)據(jù)沒(méi)有加擾的協(xié)議里面是不建議使用DFE的。而更高速的協(xié)議都是64B/66B、128B/130B編碼, DFE一般用在這種場(chǎng)合。

另外,在高速收發(fā)器通過(guò)背板連接的應(yīng)用中,因?yàn)檫^(guò)孔和連接器阻抗不匹配引起反射,通道的衰減就像圖中淺綠的線,在某些頻率點(diǎn)衰減很大。在這種情況下CTLE的效果就比較差,DFE的效果就會(huì)比較好。

更多信息可以來(lái)這里獲取==>>電子技術(shù)應(yīng)用-AET<<