FPGA工程師怎么把算法用RTL實現(xiàn)?FPGA工程師實現(xiàn)算法的時候科學步驟是什么?FPGA的開發(fā)設計怎樣進行仿真驗證?

群友們提到一個很多人都會遇到的現(xiàn)實問題:

“把一個算法用RTL實現(xiàn),有哪些比較科學的步驟?第一步干什么?第二步干什么?第三步干什么……?”

這個問題,對于FPGA、ASIC等邏輯電路設計人員來講,是非常重要的問題。

通常來講,我們做算法實現(xiàn),需要有對標的算法模型,作為驗證硬件邏輯設計是否正確的參考依據(jù)。

我們首先要根據(jù)實際需求,針對某方面的信號處理問題,做一個鏈路級或模塊級快速仿真驗證設計。最常見的比如通過MATLAB/C/C++等軟件環(huán)境進行設計和驗證。

軟件環(huán)境可以快速搭建仿真模型,并且進行驗證,為硬件RTL實現(xiàn)提供參考依據(jù)。在具體算法設計時,必須考慮數(shù)據(jù)流的處理過程:數(shù)據(jù)從哪里來,數(shù)據(jù)需要經(jīng)過哪些步驟處理,處理之后送到哪里。

接下來,我們需要將MATLAB、C++等算法模型由浮點轉為定點,這個工作可以做好之后再去做邏輯設計,也可以省略,但一定要清楚是如何定點的。

做好算法設計后,需要進行性能評估,看是否符合預期要求,不符合則進一步優(yōu)化,或者換一種設計方法。

在做邏輯實現(xiàn)之前,還有一個重要工作,就是對算法處理步驟進行一步一步分解,解決如何從a到b再到c的過程,落實到加減乘除。

當算法實際滿足要求后,則考慮邏輯實現(xiàn)的問題。

首先,建議采用自頂向下的設計思想,進行系統(tǒng)架構設計,明確整個處理過程,需要執(zhí)行哪些功能,涉及哪些接口。

接下來,選芯片器件,評估資源占用情況,評估需要用多少乘法器,除法器,DSP,BRAM,GT等。

其次,評估處理時間要求,是否需要實時性處理,給予多少時間來處理,進而評估所需時鐘頻率,以及是否需要存在多個時鐘域處理。

對于信號處理系統(tǒng),有的需要實時處理,有的則不需要實時處理。最具挑戰(zhàn)的無疑是實時性要求高的通信、雷達和圖像等領域的信號處理問題。

首先解決信號處理中的算法問題,為實現(xiàn)某一處理過程,需要分哪些步驟,最終得到什么樣的結果。

為了實現(xiàn)實時處理,邏輯電路該怎么去設計?

于是,算法問題既要研究如何處理數(shù)據(jù)流的問題,也要研究如何快速處理的問題。

電路實現(xiàn)時,則需要考慮資源消耗、并行處理結構,流水處理和控制邏輯。

如果有處理速率要求,則需考慮并行+流水的處理方式,并考慮單時鐘下的數(shù)據(jù)位寬。

同時,務必明確數(shù)據(jù)流向,前后級接口,功能模塊內(nèi)部RTL邏輯處理,細化到每個時鐘應該怎么處理,step by step。

以上都比較明確后,可以著手進行RTL設計。RTL設計的核心,便是寄存器、RAM和FSM的靈活使用。其中,F(xiàn)SM占據(jù)了大部分功能。通常情況下,我們不只是操作純數(shù)據(jù)流,而是在各種控制信號和參數(shù)下進行設計,此時涉及各種FSM和選擇器設計,并注意是否需要進行流控。

RTL代碼設計完成之后,進行TestBench平臺搭建和仿真驗證是必要的,特別是對于復雜功能模塊或系統(tǒng)設計而言。經(jīng)驗再豐富的工程師,也不敢保證,不經(jīng)過仿真驗證直接上板一定沒問題。

驗證也是一門重要的技術,這也是為什么存在IC驗證崗位,目的就是為芯片成功流片嚴格把關,一旦流片失敗,損失重大,影響深遠。

FPGA的開發(fā)設計,同樣需要進行仿真驗證。通常,我們可以通過算法鏈路產(chǎn)生所需激勵源,通過TestBench對功能模塊進行驗證,并進行結果對比分析。重點解決兩個問題:

一是驗證邏輯時序是否存在問題,比如信號是否對齊,有無接口處理不當導致數(shù)據(jù)丟失等。

二是信號處理過程是否得當,數(shù)據(jù)位寬、精度等是否符合算法要求。

解決功能性問題后,就需要考慮性能問題。定點是否合適,與浮點算法性能的差異有多大,或者軟件中的定點處理與邏輯電路定點處理,誤差有多大。在不斷驗證過程中,優(yōu)化算法設計和邏輯電路設計。

剩下的邏輯綜合、實現(xiàn)、比特流生成和調(diào)試等環(huán)節(jié),屬于常規(guī)操作,但對于邏輯綜合、實現(xiàn)中的時序約束和相關策略設置,也是十分重要的。

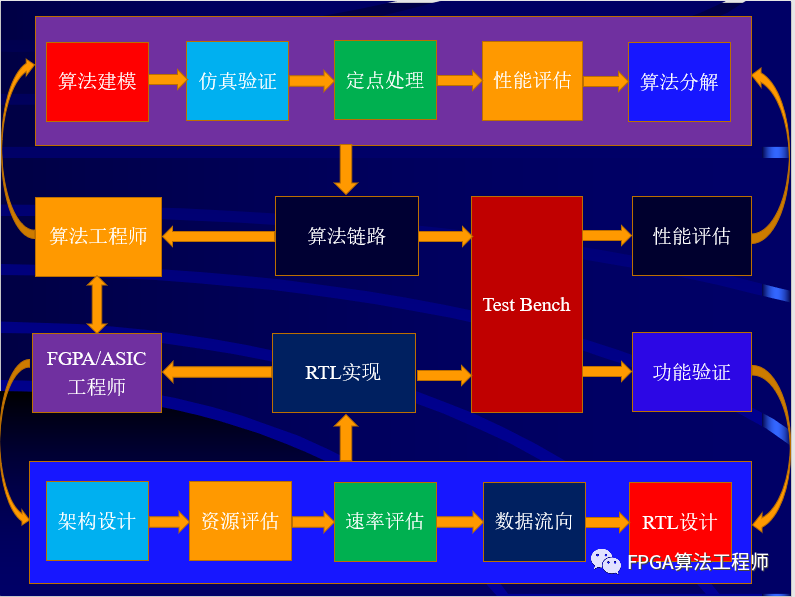

最后,用一張圖總結如何從算法到RTL實現(xiàn)。

本文只是粗略地分析了算法到RTL代碼實現(xiàn)之間的邏輯關系,以及從實現(xiàn)角度,我們應該怎么去著手。

具體到某個信號處理算法實現(xiàn)時,必須清楚整個信號處理過程,對算法一步一步分解,再對信號流、定點和接口進行設計。

做任何事情之前,先謀劃布局,磨刀不誤砍柴工,扎扎實實做好每一步,功到自然成。

更多信息可以來這里獲取==>>電子技術應用-AET<<