大多數(shù) FPGA 設(shè)計(jì)人員都充滿熱情地開展專業(yè)化問題解決和創(chuàng)造性工作,當(dāng)然,他們工作壓力也相當(dāng)大,工作流程也非常單調(diào)乏味。幸運(yùn)的是,EDA 公司和 FPGA 廠商不斷開發(fā)新的工具和方法,推進(jìn)繁瑣任務(wù)的自動(dòng)化,幫助設(shè)計(jì)團(tuán)隊(duì)集中精力做好創(chuàng)造性工作。下面我們就來看看 FPGA 工具流程的演進(jìn)發(fā)展,了解一下現(xiàn)代 FPGA 團(tuán)隊(duì)是如何利用 RTL分析、約束生成和綜合導(dǎo)向來減少設(shè)計(jì)迭代的。

如果您已經(jīng)是一名 FPGA 設(shè)計(jì)專業(yè)人士,那么將擁有輝煌的職業(yè)發(fā)展前景,因?yàn)樵絹碓蕉鄠鹘y(tǒng)上需要 ASIC 實(shí)現(xiàn)的設(shè)計(jì)現(xiàn)已改用 FPGA。隨著新一代芯片工藝技術(shù)的推出,設(shè)計(jì) ASIC的成本正呈幾何級(jí)數(shù)增加。與此同時(shí),F(xiàn)PGA 廠商則能利用最新工藝技術(shù)實(shí)現(xiàn)新一代產(chǎn)品,且不會(huì)讓客戶承擔(dān)過重的成本負(fù)擔(dān)。

但不容樂觀的是,F(xiàn)PGA 設(shè)計(jì)相當(dāng)復(fù)雜,需要跟 ASIC 流程一樣復(fù)雜的工具流程,這往往需要整個(gè)設(shè)計(jì)團(tuán)隊(duì)的共同努力才能完成,而不能光靠一名設(shè)計(jì)人員。因此,F(xiàn)PGA 設(shè)計(jì)團(tuán)隊(duì)在著手ECO 或新項(xiàng)目之前應(yīng)認(rèn)真分析現(xiàn)有的工具套件。那么好消息呢?就是新一代EDA 工具如雨后春筍般涌出,可助他們一臂之力。設(shè)計(jì)人員可選擇采用標(biāo)準(zhǔn)數(shù)據(jù)格式且易于安裝和使用的工具,簡(jiǎn)化流程集成工作,而且能夠在選定的平臺(tái)(不管是 Windows 還是 Linux)上實(shí)現(xiàn)本機(jī)運(yùn)行。

FPGA 工具流程的發(fā)展演進(jìn)

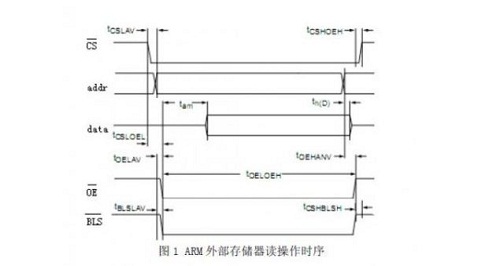

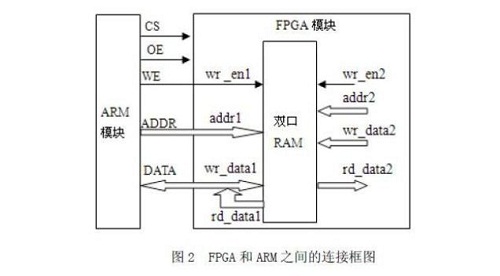

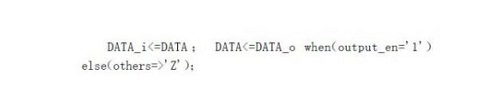

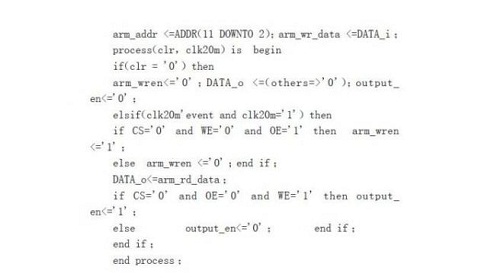

這些年來,F(xiàn)PGA 設(shè)計(jì)日趨復(fù)雜,工具流程也隨之發(fā)展,而且越來越像 ASIC流程。上世紀(jì) 90 年代,F(xiàn)PGA 流程(見圖 1 的流程 A)跟當(dāng)時(shí)的簡(jiǎn)易 ASIC 流程一樣,最初以 RTL 為基礎(chǔ),并采用綜合及布局布線工具。隨著設(shè)計(jì)變得進(jìn)一步復(fù)雜化,F(xiàn)PGA 團(tuán)隊(duì)在流程中增加了時(shí)序分析功能,幫助客戶確保設(shè)計(jì)能按指定的頻率運(yùn)行。今天的 FPGA已經(jīng)發(fā)展為龐大的系統(tǒng)平臺(tái),設(shè)計(jì)團(tuán)隊(duì)通常要通過 RTL 分析來最小化設(shè)計(jì)迭代,并確保設(shè)計(jì)能夠?qū)崿F(xiàn)相應(yīng)的性能目標(biāo)。

進(jìn)而言之,由于今天的 FPGA 設(shè)計(jì)項(xiàng)目非常龐大復(fù)雜,所以設(shè)計(jì)人員需要想盡一切辦法更好地了解設(shè)計(jì)的規(guī)模和復(fù)雜性,以便更好地控制流程中的工具,加速設(shè)計(jì)上市進(jìn)程。現(xiàn)代FPGA 設(shè)計(jì)團(tuán)隊(duì)正在采用一種新型方法,那就是在整個(gè)設(shè)計(jì)流程中貫穿約束機(jī)制。我們不妨看看當(dāng)下最流行的、現(xiàn)已得到賽靈思最新 Vivado 流程支持的一種約束方法——Synopsys 設(shè)計(jì)約束 (SDC) 格式,以及了解如何通過 SDC 讓設(shè)計(jì)項(xiàng)目受益。

什么是 SDC?

SDC 是一款基于 TCL 的格式,可用來設(shè)定設(shè)計(jì)目標(biāo),包括設(shè)計(jì)的時(shí)序、功耗和面積約束。一些產(chǎn)品能讀取或?qū)懭?SDC。一些示例 SDC 約束包括時(shí)序約束(如創(chuàng)建時(shí)鐘、創(chuàng)建生成時(shí)鐘、設(shè)置輸入延遲和設(shè)置輸出延遲)和時(shí)序例外(如設(shè)置錯(cuò)誤路徑、設(shè)置最大延遲、設(shè)置最小延遲以及設(shè)置多周期路徑)。這些 SDC 約束通常應(yīng)用于寄存器、時(shí)鐘、端口、引腳和網(wǎng)絡(luò)(連線)等設(shè)計(jì)對(duì)象。

需要指出的是,盡管 SDC 是標(biāo)準(zhǔn)化格式,但生成的 SDC 和讀取 SDC之間還是略有差異(不同工具之間有差異)。了解這些差異并積極采取措施,有助于避免意外情況的發(fā)生。

SDC 不應(yīng)過于復(fù)雜

SDC 最常見的應(yīng)用就是約束綜合。一般說來,設(shè)計(jì)人員要考慮設(shè)計(jì)的哪些方面需要約束,并為其編寫 SDC。設(shè)計(jì)人員通常要執(zhí)行流程 B 中描述的流程,首次肯定無法進(jìn)行時(shí)序收斂。隨后要反復(fù)手動(dòng)盲目嘗試添加 SDC,以實(shí)現(xiàn)時(shí)序收斂,或讓設(shè)計(jì)能在指定的頻率上工作。許多從事過上述工作的設(shè)計(jì)人員都抱怨說設(shè)計(jì)迭代要花好幾個(gè)星期,往往會(huì)拖延設(shè)計(jì)進(jìn)程。

迭代的另一個(gè)問題在于,數(shù)名設(shè)計(jì)人員可能在不同的地點(diǎn)為 SDC 設(shè)計(jì)不同的模塊。這樣設(shè)計(jì)工作會(huì)變得非常復(fù)雜,設(shè)計(jì)團(tuán)隊(duì)必須想辦法驗(yàn)證SDC,避免在芯片級(jí)封裝階段出現(xiàn)層級(jí)名稱的沖突。要確保進(jìn)行有效的設(shè)計(jì)協(xié)作,就必須采用適當(dāng)?shù)墓ぞ吆头椒ā?/p>

流程 C 是現(xiàn)代化流程,除了流程B 的工具之外還采用了分析、SDC 約束和高層次綜合技術(shù),在解決上述問題方面發(fā)揮了重大作用。

綜合向?qū)?/b>

對(duì)典型的 FPGA 設(shè)計(jì)而言,綜合解決方案還處于探索階段,不管是面積、速度還是功耗的優(yōu)化,都存在多個(gè)局部最大值和局部最小值。利用智能向?qū)В覀兡軐?shí)現(xiàn)最佳解決方案,避免綜合工具聚集到任意的局部最小值。最有效的向?qū)е痪褪遣捎缅e(cuò)誤路徑和多周期路徑,避免綜合工具為不必要的組件浪費(fèi)寶貴的優(yōu)化時(shí)間。

不過,找到設(shè)計(jì)中的所有錯(cuò)誤路徑 (FP) 和多周期路徑 (MCP) 并不容易。花上足夠的時(shí)間,我們能找到一些簡(jiǎn)單的 FP 和 MCP,不過一些涉及狀態(tài)機(jī)和計(jì)數(shù)器的復(fù)雜 FP 和 MCP(特別是在多個(gè)層級(jí)中)則很難找到。幸運(yùn)的是,F(xiàn)PGA 設(shè)計(jì)人員可采用Blue Pearl Software 等創(chuàng)新公司推出的工具執(zhí)行自動(dòng)化 FP 和 MCO 生成,從而確保完整性、全面性和準(zhǔn)確性。此外,這些工具還能為每個(gè) FP 和MCP 提供不同的機(jī)制,包括原理圖、斷言和審核路徑,從而讓用戶驗(yàn)證其正確性。

由于 FPGA 廠商和商用 EDA 廠商的合作進(jìn)一步加強(qiáng),采用通用接口,設(shè)計(jì)團(tuán)隊(duì)就能夠?qū)?Blue Pearl 軟件套件集成到他們所青睞的工作流程中。既然賽靈思的最新 Vivado 設(shè)計(jì)套件支持 SDC,那么在不同工具之間溝通設(shè)計(jì)意圖就變得極其簡(jiǎn)單(圖 2)。

除了與賽靈思及其他 FPGA 廠商協(xié)作外,Blue Pearl 公司還同Synopsys 開展密切合作。這兩家公司共同研究如何讓綜合工具接受盡可能多的自動(dòng)生成的 SDC,同時(shí)避免設(shè)計(jì)人員進(jìn)行任何手動(dòng)修改。由于 SDC 格式對(duì)不同工具的使用差異很小,因此工作團(tuán)隊(duì)快速明確命名方案是順利實(shí)現(xiàn)互操作性的一大挑戰(zhàn)。

這里的解決方案是在綜合的第一階段(編譯)后截取映射名稱,在 BluePearl 軟件套件的 SDC 生成工具中使用名稱(見圖 3),并為綜合工具的第二階段(優(yōu)化)提供適當(dāng)?shù)?SDC。該方法給 FPGA 設(shè)計(jì)人員提供了一個(gè)最佳解決方案,無需花時(shí)間處理格式化問題。

以下給出非優(yōu)化型約束編寫示例:

set_false_path -from

[get_cells

{i_tv80_core.SP[*]}] -to

[get_cells

{i_tv80_core.i_reg.RegsL}]

優(yōu)化后則為:

set_false_path -from

[get_cells

{i_tv80_core.SP[*]}] -to

[get_cells

{i_tv80_core.i_reg.RegsL_2[7:0]}]

能取得哪些實(shí)際的效果?

Blue Pearl 軟件套件能實(shí)現(xiàn)一些任務(wù)的自動(dòng)化, 設(shè)計(jì)人員對(duì)其結(jié)果質(zhì)量(QoR) 很滿意。表 1 顯示了用 Blue Pearl 軟件套件自動(dòng)生成 SDC,能將示例設(shè)計(jì)的 QoR 提升 20%,該示例采用多個(gè) IP 核,其中包括 Verilog 的R1200 和 VHDL 的 AES 加密。

運(yùn)行 1 未采用 Blue Pearl 軟件,結(jié)果沒有實(shí)現(xiàn)時(shí)序收斂。設(shè)計(jì)人員用RTL 設(shè)計(jì)或工具約束進(jìn)行迭代以滿足60MHz 的要求很容易就要花上好幾個(gè)星期的時(shí)間。在運(yùn)行 2 中,Blue Pearl軟件套件幾分鐘就能生成 SDC,而自動(dòng)生成的SDC 足以指導(dǎo)下游工具滿足時(shí)序要求。

顯然,對(duì) FPGA 設(shè)計(jì)人員來說,降低壓力、簡(jiǎn)化工作的一個(gè)好辦法就是跟別人一樣添加 RTL 分析、SDC 生成和綜合向?qū)Чぞ摺?/p>