門控時(shí)鐘的設(shè)計(jì)初衷是實(shí)現(xiàn)FPGA的低功耗設(shè)計(jì),本文從什么是門控時(shí)鐘、門控時(shí)鐘實(shí)現(xiàn)低功耗的原理、推薦的FPGA門控時(shí)鐘實(shí)現(xiàn)這三個(gè)角度來(lái)分析門控時(shí)鐘。

一、什么是門控時(shí)鐘

門控時(shí)鐘技術(shù)(gating clock) 是通過在時(shí)鐘路徑上增加邏輯門對(duì)時(shí)鐘進(jìn)行控制,使電路的部分邏輯在不需要工作時(shí)停止時(shí)鐘樹的翻轉(zhuǎn),而并不影響原本的邏輯狀態(tài)。在ASIC和FPGA設(shè)計(jì)中都存在門控時(shí)鐘的概念(前者應(yīng)用更廣)。

典型的門控時(shí)鐘邏輯如下圖所示:

二、門控時(shí)鐘降低功耗的原理

1. FPGA功耗分類

靜態(tài)功耗:靜態(tài)功耗又叫泄漏功耗,它是指電路處于等待或不激活狀態(tài)時(shí)-泄漏電流所產(chǎn)生的功耗。通常由FPGA制造工藝的優(yōu)化而提升。同一代的FPGA產(chǎn)品中,也有專門的低功耗版本(譬如Intel開發(fā)的Cyclone10 GX與Cyclone 10 LP,后者為低功耗版本low power但前者性能更強(qiáng))。可以在FPGA選型時(shí)加以考慮。

動(dòng)態(tài)功耗:是指電容充放電功耗和短路功耗,是由電路的翻轉(zhuǎn)造成的。FPGA中的動(dòng)態(tài)功耗主要體現(xiàn)在元件的電平翻轉(zhuǎn)時(shí)對(duì)負(fù)載電容的充放電及時(shí)鐘的翻轉(zhuǎn)。

2. 為什么門控時(shí)鐘可以降低功耗

當(dāng)系統(tǒng)中某模塊電路完成既定任務(wù)后(譬如TDC中對(duì)BIN的標(biāo)定等初始化類任務(wù)),通過門控時(shí)鐘使能信號(hào)的控制,使得驅(qū)動(dòng)該模塊的時(shí)鐘停止翻轉(zhuǎn),相應(yīng)的時(shí)序元件不再更新,那么其間的組合邏輯也恢復(fù)到靜態(tài)。此時(shí)該模塊的功耗相當(dāng)于靜態(tài)功耗,從而降低了整個(gè)系統(tǒng)的功耗。

三、不合理的門控時(shí)鐘設(shè)計(jì)

1.偽門控時(shí)鐘

如下圖所示,設(shè)計(jì)中有意識(shí)地使用使能信號(hào),意圖維持寄存器的數(shù)據(jù)。但是僅對(duì)寄存器組的數(shù)據(jù)輸入端添加選擇器和使能信號(hào),并不妨礙寄存器組時(shí)鐘輸入端的翻轉(zhuǎn),輸出維持不變只是因?yàn)榇嬖诜答伝芈吩诓粩嗟倪M(jìn)行使能判斷、輸出、使能判斷、輸出的循環(huán)。實(shí)則并沒有起到低功耗的作用。

當(dāng)然某些情況下確實(shí)需要用到這種設(shè)計(jì),此處僅用來(lái)和門控時(shí)鐘做區(qū)分,避免混淆。

2.直接門控時(shí)鐘

將使能信號(hào)直接連接在AND門,結(jié)構(gòu)簡(jiǎn)單。不足之處在于產(chǎn)生使能信號(hào)的組合邏輯的毛刺將完全地反應(yīng)到AND門,造成門控時(shí)鐘輸出質(zhì)量變差(clk_en將會(huì)有占空比不良和毛刺等情況)。

四、推薦的門控時(shí)鐘設(shè)計(jì)

1.基于鎖存器的門控時(shí)鐘

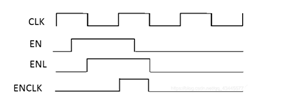

鎖存器是電平敏感的元件,此圖中當(dāng)CLK信號(hào)為低電平時(shí),鎖存器透明,EN端數(shù)據(jù)直接傳輸至AND門的一端(ENL),AND門另一端連接CLK。

當(dāng)產(chǎn)生使能信號(hào)的組合邏輯不復(fù)雜時(shí),產(chǎn)生使能信號(hào)的時(shí)間小于半個(gè)時(shí)鐘周期。在CLK高電平時(shí),鎖存器的引入有效地過濾了前段組合邏輯競(jìng)爭(zhēng)冒險(xiǎn)產(chǎn)生的毛刺;在時(shí)鐘低電平時(shí),前段組合邏輯的毛刺將受到AND門控制將無(wú)法輸出。較好地實(shí)現(xiàn)了門控時(shí)鐘的要求。

當(dāng)產(chǎn)生使能信號(hào)的組合邏輯復(fù)雜時(shí),產(chǎn)生使能信號(hào)的時(shí)間大于半個(gè)時(shí)鐘周期。考慮鎖存器的延時(shí),那么對(duì)于首個(gè)ENCLK周期而言,占空比將被削減;當(dāng)EN信號(hào)拉低時(shí),則有可能產(chǎn)生毛刺。均不利于后續(xù)寄存器組的時(shí)序過程。

這種情況難以通過在鎖存器前端加同步寄存器避免,因?yàn)榇藭r(shí)的使能信號(hào)是不滿足寄存器的建立時(shí)間的,大概率會(huì)產(chǎn)生亞穩(wěn)態(tài)現(xiàn)象。因此產(chǎn)生門控使能信號(hào)的組合邏輯應(yīng)當(dāng)盡可能簡(jiǎn)化,保證在半個(gè)時(shí)鐘周期之內(nèi)得到穩(wěn)定電平。

保險(xiǎn)起見,一方面,保證使能信號(hào)半周期確定;另一方面,在鎖存器之前加一級(jí)上升沿觸發(fā)的寄存器,過濾輸入鎖存器的信號(hào)。

2.基于寄存器的門控時(shí)鐘

上面介紹的基于鎖存器的門控時(shí)鐘實(shí)際上更適合在ASIC中實(shí)現(xiàn),一方面FPGA中沒有專門的鎖存器資源,需要利用其中的組合邏輯資源外加寄存器來(lái)等效地實(shí)現(xiàn),不經(jīng)濟(jì);另一方面,鎖存器本身的特性沒法進(jìn)行靜態(tài)時(shí)序分析,出問題了不易排查。

真正適合在FPGA中實(shí)現(xiàn)的是基于寄存器的門控時(shí)鐘,如下圖所示。

前段使用加法器產(chǎn)生計(jì)數(shù)值,通過比較器產(chǎn)生使能信號(hào),送入使能寄存器。值得注意的是,前端產(chǎn)生使能邏輯時(shí)序元件是上升沿觸發(fā),而使能寄存器是下降沿觸發(fā)。如此一來(lái),同樣需要滿足產(chǎn)生使能信號(hào)的組合邏輯簡(jiǎn)單這一前提要求(半周期內(nèi)達(dá)到en寄存器的建立時(shí)間)。好處在于,AND門時(shí)時(shí)刻刻都只有一個(gè)輸入在變,不容易產(chǎn)生毛刺。時(shí)序圖如下:

為了便于理解,此處給出若使能寄存器也是上升沿觸發(fā)的時(shí)序圖:

可見,AND門變化時(shí)兩個(gè)個(gè)輸入在變,容易產(chǎn)生毛刺。

五、討論

只有當(dāng)FPGA工程需要大量降低功耗時(shí)才有必要引入門控時(shí)鐘,若必須引入門控時(shí)鐘,則推薦使用基于寄存器的門控時(shí)鐘設(shè)計(jì)。

在時(shí)鐘樹的枝干處使用門控,而不是在枝丫處使用門控。

使用門控時(shí),應(yīng)該注意時(shí)鐘的質(zhì)量(使用專用時(shí)鐘網(wǎng)絡(luò)),畢竟好的時(shí)鐘才能產(chǎn)生好的使能信號(hào)和門控時(shí)鐘信號(hào)。同時(shí),產(chǎn)生使能信號(hào)的邏輯不能太復(fù)雜,確保可以滿足使能寄存器的建立時(shí)間和保持時(shí)間。

與或門控輸出的時(shí)鐘信號(hào),需要在timeanalyzer中設(shè)置為base clock。否則將會(huì)引入人為的時(shí)鐘偏斜。如下,將會(huì)以沒有使能寄存器的門控路徑作為最短分析路徑,以有寄存器的路徑作為最長(zhǎng)路徑分析。

類似地,產(chǎn)生門控時(shí)鐘信號(hào)最好只有一個(gè)兩輸入AND門(OR門)。附加邏輯越多,產(chǎn)生毛刺可能性越大。