集成電路工藝節(jié)點(diǎn)的提升帶來(lái)了芯片集成度的極大提高,同時(shí)也導(dǎo)致了功耗的急速增加。另外,市場(chǎng)對(duì)電子設(shè)備的大量需求使得系統(tǒng)功耗成為系統(tǒng)性能的一個(gè)重要指標(biāo),功耗的高低成了芯片廠商競(jìng)爭(zhēng)力的焦點(diǎn)之一,功耗控制與管理已成為絕大多數(shù)芯片廠商首要考慮的問(wèn)題。SoC設(shè)計(jì)的功耗包含兩部分:靜態(tài)功耗和動(dòng)態(tài)功耗。靜態(tài)功耗主要由泄漏電流引起,在130 nm工藝下,靜態(tài)功耗相對(duì)較小,可以忽略不計(jì)。動(dòng)態(tài)功耗主要包括短路功耗和翻轉(zhuǎn)功耗,是本設(shè)計(jì)功耗的主要組成部分。短路功耗即內(nèi)部功耗,指由器件內(nèi)部由于P管和N管在某一瞬間同時(shí)導(dǎo)通引起的瞬時(shí)短路引起。翻轉(zhuǎn)功耗由CMOS器件的輸出端負(fù)載電容充放電引起。芯片工作時(shí),很大一部分功耗是由于時(shí)鐘網(wǎng)絡(luò)的翻轉(zhuǎn)消耗的,如果時(shí)鐘網(wǎng)絡(luò)較大,這部分引起的功耗損失會(huì)很大。在眾多低功耗技術(shù)中,門(mén)控時(shí)鐘對(duì)翻轉(zhuǎn)功耗和內(nèi)部功耗的抑制作用最強(qiáng)。本文主要講述門(mén)控時(shí)鐘技術(shù)的具體實(shí)現(xiàn)。另外,基于高閾值單元具有較低的功耗,設(shè)計(jì)采用高閾值單元庫(kù)。

1 門(mén)控時(shí)鐘技術(shù)的基本原理

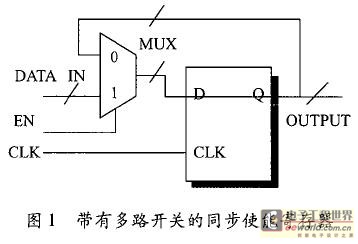

對(duì)于一個(gè)設(shè)計(jì)中的寄存器組,經(jīng)DC編譯后一般會(huì)生成如圖1所示的電路。由圖1可以看出,當(dāng)EN為1時(shí), DATA_ IN的值由多路開(kāi)關(guān)傳至寄存器組的數(shù)據(jù)輸入端,當(dāng)CLK上升沿來(lái)臨時(shí),傳至DATA_OUT。當(dāng)EN為0時(shí), OUTPUT保持不變。但由于時(shí)鐘信號(hào)CLK的翻轉(zhuǎn),寄存器組會(huì)持續(xù)在CLK的上升沿來(lái)臨時(shí)讀取數(shù)據(jù)輸入端的數(shù)據(jù),而這時(shí)讀取的數(shù)據(jù)是不變的,這就消耗了額外的功耗。

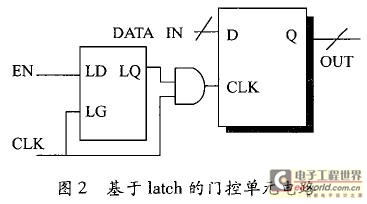

為保證此時(shí)寄存器組不受時(shí)鐘翻轉(zhuǎn)的影響,可在EN信號(hào)為0時(shí)關(guān)斷寄存器組的時(shí)鐘輸入端,使其不受CLK端的變化而變化,這一操作可通過(guò)門(mén)控時(shí)鐘技術(shù)來(lái)實(shí)現(xiàn),如圖2所示。圖中的門(mén)控單元由一個(gè)Latch和一個(gè)與門(mén)組成。門(mén)控單元也可以采用非latch結(jié)構(gòu),直接由與門(mén)或或門(mén)組成。但由于這種電路會(huì)引發(fā)毛刺,故此處采用基于Latch的門(mén)控單元電路。插入門(mén)控時(shí)鐘后,當(dāng)EN為1時(shí), Latch單元在時(shí)鐘低電平時(shí)將EN鎖存至ENL,時(shí)鐘上升沿來(lái)臨時(shí), ENCLK隨CLK變化,寄存器組執(zhí)行正常的讀入讀出操作。當(dāng)EN為0時(shí),寄存器時(shí)鐘輸入端ENCL保持為0,不隨源時(shí)鐘CLK的翻轉(zhuǎn)而變化,故此時(shí)寄存器組不消耗額外功率。

由此可見(jiàn),插入門(mén)控時(shí)鐘能消除寄存器組冗余翻轉(zhuǎn)引發(fā)的內(nèi)部功耗,同時(shí)由于多路選擇器組被一個(gè)基于latch的門(mén)控單元代替,所以也減小了電路的面積。

另外,為了進(jìn)一步減小設(shè)計(jì)的功耗,可采用一些特定的門(mén)控技術(shù)。目前應(yīng)用比較廣泛的有多級(jí)門(mén)控時(shí)鐘,層次化門(mén)控時(shí)鐘等。在多級(jí)門(mén)控時(shí)鐘技術(shù)中,一個(gè)門(mén)控單元還可用來(lái)驅(qū)動(dòng)其他一個(gè)或一組門(mén)控單元。這樣就通過(guò)分級(jí)控制減少了門(mén)控單元的數(shù)目,而且這種方法可組合盡可能多的寄存器組使得門(mén)控單元向頂層靠近,節(jié)省更多功耗。

2 門(mén)控時(shí)鐘的物理實(shí)現(xiàn)

電路在功能仿真通過(guò)后,開(kāi)始進(jìn)行寄存器級(jí)綜合。采用高閾值標(biāo)準(zhǔn)單元庫(kù)和多級(jí)門(mén)控時(shí)鐘技術(shù)相結(jié)合,在RTL階段插入門(mén)控時(shí)鐘單元,并在布局布線時(shí)在IC Compiler中進(jìn)行了基于門(mén)控時(shí)鐘的布局布線優(yōu)化,布局布線正確完成仿真通過(guò)后,在PT中做靜態(tài)時(shí)序分析并進(jìn)行最終的功耗分析。以下分三個(gè)部分講述。

在RTL級(jí),門(mén)控時(shí)鐘的實(shí)現(xiàn)不需要對(duì)設(shè)計(jì)本身進(jìn)行修改,而只需在綜合腳本中加入一些控制項(xiàng)。

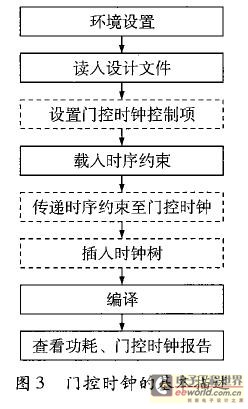

本文采用多級(jí)門(mén)控時(shí)鐘,相關(guān)的腳本如圖3 所示。

圖中,傳統(tǒng)的綜合流程用實(shí)線標(biāo)出。虛線部分為門(mén)控時(shí)鐘的操作。

控制項(xiàng)set_clock_gating_ STyle是門(mén)控時(shí)鐘的核心。它的參數(shù)大小決定門(mén)控時(shí)鐘的質(zhì)量,對(duì)功耗的優(yōu)化效果和對(duì)CTS的影響。目前尚無(wú)完備的體系介紹如何設(shè)置控制項(xiàng)以使門(mén)控效果達(dá)到最優(yōu)。本設(shè)計(jì)中有以下各個(gè)參數(shù)的設(shè)置方法。

首先確定時(shí)序單元的類型。為了避免非Latch單元易產(chǎn)生毛刺的缺點(diǎn),此處選定時(shí)序單元的類型為L(zhǎng)atch。由于庫(kù)中提供基于鎖存器的門(mén)控單元,固正邊沿邏輯positive_edge_ logic采用工藝庫(kù)提供的專用單元。采用集成單元的優(yōu)勢(shì)在于不僅不需要設(shè)置門(mén)控單元輸入端建立時(shí)間和保持時(shí)間,因?yàn)榧蓡卧臅r(shí)序信息在單元庫(kù)中已有說(shuō)明,而且有效緩解了插入門(mén)控單元對(duì)延時(shí)帶來(lái)的不利影響。以下重點(diǎn)闡述實(shí)驗(yàn)中bitwIDTh, fanout和stage的確立方法。

fanout的大小對(duì)功耗和時(shí)序都有影響。數(shù)值越大則表示一個(gè)門(mén)控單元可承受較多的負(fù)載,即代表越節(jié)省功耗,需要的門(mén)控單元也越少,但對(duì)門(mén)控單元輸入端建立時(shí)間的要求也就更加嚴(yán)格。位寬決定一組寄存器能被門(mén)控的最小寬度。級(jí)數(shù)則確定多級(jí)門(mén)控時(shí)鐘的最大級(jí)數(shù)。本設(shè)計(jì)在這三個(gè)參數(shù)的選取上,主要是依據(jù)設(shè)計(jì)本身對(duì)功耗的要求,結(jié)合綜合時(shí)的時(shí)序約束和單元庫(kù)中門(mén)控單元的時(shí)延信息加以估計(jì),確定一個(gè)粗略的數(shù)值范圍。fanout的值在滿足時(shí)序的前提下,不經(jīng)編譯就可確定,方法如下:首先按約束文件中的扇出值約束此處fanout,然后insert_clock_tree,加入時(shí)序約束并傳遞至門(mén)控時(shí)鐘,用re_port_clock_gating– multi_stage查看報(bào)告,重點(diǎn)關(guān)注第1項(xiàng)。發(fā)現(xiàn)fanout按約束文件取值為15時(shí),門(mén)控單元的數(shù)目達(dá)到61個(gè), fanout取值為20或更高時(shí),門(mén)控單元數(shù)目為41,見(jiàn)表1,而被門(mén)控的寄存器數(shù)目卻保持不變,多級(jí)門(mén)控單元的數(shù)目也由fanout取值為15時(shí)的7級(jí)減小到當(dāng)前的6級(jí)。由于門(mén)控單元也會(huì)消耗相當(dāng)大功耗,因此在被門(mén)控的寄存器數(shù)目相同的情況下門(mén)控單元數(shù)越少就越節(jié)省功耗。因此確定fanout為20。

num_stages最初取值為2,插入門(mén)控時(shí)鐘后的報(bào)告顯示平均級(jí)數(shù)為1. 4,其值增至3時(shí),平均級(jí)數(shù)為2. 3,如表1 所示。從對(duì)時(shí)鐘網(wǎng)絡(luò)的平衡性來(lái)講,stage值為2時(shí)要優(yōu)于取值為3時(shí)的情況,但結(jié)合其后的編譯,綜合考慮時(shí)序面積功耗因素,折衷考慮選定stage為3。

bitwidth初值為3,經(jīng)過(guò)編譯,得出了功耗和延時(shí)信息。以此為基準(zhǔn),根據(jù)設(shè)計(jì)改變bitwidth數(shù)值,然后再編譯,對(duì)比功耗延時(shí)。發(fā)現(xiàn)當(dāng)bitwidth取值為5時(shí),設(shè)計(jì)的各個(gè)性能指標(biāo)達(dá)到最優(yōu)。

通過(guò)以上試驗(yàn),得出下列結(jié)論: 對(duì)門(mén)控時(shí)鐘而言,若不考慮設(shè)計(jì)的平衡性,插入的門(mén)控單元越少且被門(mén)控的寄存器越多, 門(mén)控的效果就越好,反之亦然。

經(jīng)編譯,查看時(shí)序功耗報(bào)告,在滿足電路性能指標(biāo)情況下, RTL級(jí)代碼經(jīng)綜合生成層次化門(mén)級(jí)網(wǎng)表和門(mén)級(jí)時(shí)序約束文件。

為查看門(mén)控單元在不同設(shè)置下的插入情況,用report_clock_gating– multi_stage得到表1所示報(bào)告。

從中可知,有23. 68 %的寄存器沒(méi)有被門(mén)控,原因在于位寬, 使能等不滿足門(mén)控要求,對(duì)設(shè)計(jì)無(wú)影響。

2. 2 時(shí)鐘門(mén)控的版圖級(jí)實(shí)現(xiàn)

在布局布線階段,基于門(mén)控時(shí)鐘的功耗優(yōu)化流程主要如下:在布局之前,設(shè)置set_Power_op tiONs–clock_gating true,之后在布局、時(shí)鐘樹(shù)綜合和布線階段的主要命令中添加選項(xiàng)- power即可。上述設(shè)置可實(shí)現(xiàn)最

基本的門(mén)控時(shí)鐘布局布線,但在本設(shè)計(jì)中生成的時(shí)鐘網(wǎng)絡(luò)分布不均勻,而且skew很大。需要采取額外的優(yōu)化措施來(lái)消除其帶來(lái)的不利影響。

門(mén)控單元的加入給CTS帶來(lái)的影響主要有兩個(gè)方面,一方面會(huì)造成整個(gè)時(shí)鐘網(wǎng)絡(luò)分布不平衡,另一方面導(dǎo)致時(shí)鐘偏移增大。單采用上述措施,時(shí)鐘偏移最大可達(dá)到1. 11,見(jiàn)圖4中的第二項(xiàng),嚴(yán)重偏離了不采用門(mén)控時(shí)鐘時(shí)的偏移量0. 12。在優(yōu)化時(shí)鐘偏移上,目標(biāo)有三個(gè)方面:構(gòu)造一個(gè)相對(duì)平衡的時(shí)鐘網(wǎng)絡(luò),使得在各個(gè)層上,層的各個(gè)分支上的單元數(shù)目相近;減小時(shí)鐘偏移至可承受范圍;盡量保持功耗同只采用門(mén)控時(shí)鐘而不優(yōu)化時(shí)鐘偏移狀況下的功耗相近或更小。

分析引起skew偏大的原因,通過(guò)在ICC中跟蹤路徑,查看時(shí)鐘網(wǎng)絡(luò)電路圖,發(fā)現(xiàn)時(shí)鐘層分布極不均勻,分支節(jié)點(diǎn)最大相差6 層。在具體時(shí)序路徑中,兩條路徑延時(shí)過(guò)大,插入了許多不必要的buffer,為構(gòu)造一個(gè)平衡的時(shí)鐘樹(shù),減小skew并減少對(duì)功耗的影響,在CTS階段采取了三個(gè)措施。

第一,設(shè)置set_clock_tree_op tions– LOGIC_ level_bal2ance為true。CTS的操作模式有三種: 模塊模式,頂層模式,邏輯級(jí)平衡模式。默認(rèn)為模塊模式。

此處選取邏輯級(jí)平衡模式可得到最佳的skew,但對(duì)功耗有一定影響。第二,復(fù)制門(mén)控單元。主要是通過(guò)修正ICG輸出端的DRC來(lái)平衡扇出,并添加緩沖單元來(lái)驅(qū)動(dòng)沒(méi)有被門(mén)控的寄存器使得整個(gè)時(shí)鐘樹(shù)的結(jié)構(gòu)更加平衡。首先設(shè)置cts_push _down_ buffer為true。然后split_ clock _ gate – ob2jects { 3 . / Latch} – gate_ sizing– gate_ relocation。

并且在時(shí)鐘樹(shù)綜合時(shí)結(jié)合使用- inter_clock_bal2ance選項(xiàng)。最后,為了彌補(bǔ)功耗優(yōu)化方面的不足,在CTS完畢之后用p synop t– power。不采用門(mén)控時(shí)鐘、采用門(mén)控時(shí)鐘但不做skew優(yōu)化、采用門(mén)控時(shí)鐘且進(jìn)行skew優(yōu)化三種情況下的skew見(jiàn)圖4。由此可見(jiàn),優(yōu)化后的skew較原來(lái)相比雖有所增大,但要遠(yuǎn)小于優(yōu)化前的設(shè)計(jì)。

2. 3 功耗測(cè)量過(guò)程及實(shí)驗(yàn)結(jié)果分析

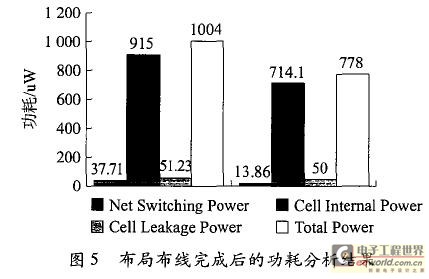

布局布線完成后,導(dǎo)出網(wǎng)表到VCS中進(jìn)行后仿,并得到分析功耗所需的saif文件。將此saif文件和布局布線后帶有實(shí)際延時(shí)信息的網(wǎng)表讀入PT中,加以適當(dāng)?shù)臅r(shí)序約束進(jìn)行功耗分析,得到如圖5所示的分析結(jié)果。

由圖5可知, 采用門(mén)控時(shí)鐘技術(shù)后的設(shè)計(jì)總體功耗下降了22. 6 %。其中, 開(kāi)關(guān)功耗下降了63. 2 % ,內(nèi)部功耗下降了21. 9 %,體現(xiàn)了引入門(mén)控時(shí)鐘技術(shù)的優(yōu)勢(shì),因?yàn)殚T(mén)控時(shí)鐘主要用于降低動(dòng)態(tài)功耗,泄露功耗略有下降。總功耗由原來(lái)的1 mW降低至778 uW,功耗降低效果非常明顯。除此之外,芯片核的面積也略有減小。

3 結(jié)語(yǔ)

越來(lái)越多低功耗設(shè)計(jì)方法的出現(xiàn)為低功耗設(shè)計(jì)提供了無(wú)限的空間。門(mén)控時(shí)鐘技術(shù)作為當(dāng)前比較成熟的一種低功耗方法,已經(jīng)得到普遍應(yīng)用。本設(shè)計(jì)全面講述了門(mén)控時(shí)鐘的后端實(shí)現(xiàn)方法,并提出了一種門(mén)控控制項(xiàng)的設(shè)置方法,解決了由其引起的時(shí)鐘偏移問(wèn)題,對(duì)VLSI深亞微米低功耗電路物理層的實(shí)現(xiàn)有一定的實(shí)用價(jià)值。