文獻(xiàn)標(biāo)識碼: A

DOI:10.16157/j.issn.0258-7998.2015.10.007

中文引用格式: 吳志毅,羅凌. 基于AD9914寬帶線性調(diào)頻源的設(shè)計及實(shí)現(xiàn)[J].電子技術(shù)應(yīng)用,2015,41(10):30-33.

英文引用格式: Wu Zhiyi,Luo Ling. Design and realization of a broadband microwave frequency source[J].Application of Electronic Technique,2015,41(10):30-33.

0 引言

在現(xiàn)代雷達(dá)系統(tǒng)中,對雷達(dá)工作頻率、頻率穩(wěn)定度和頻帶寬度都有很高的要求[1]。因此,雷達(dá)為了獲得較高的分辨率以激勵出目標(biāo)細(xì)節(jié)特征,雷達(dá)微波源的發(fā)射信號必須具有較大瞬時帶寬。

1 方案選擇

目前產(chǎn)生較大瞬時帶寬的雷達(dá)微波中頻源發(fā)射信號主要有四種方式[2],分別為DDS拼接方式、正交調(diào)制方式、多本振混頻拼接方式、高參考時鐘的DDS產(chǎn)生方式。其中DDS是目前數(shù)字產(chǎn)生線性調(diào)頻信號的主要方式。DDS 參考時鐘頻率高低與D/A 轉(zhuǎn)換器的位數(shù)決定了 DDS 產(chǎn)生信號的雜散及最高輸出頻率。

在實(shí)際應(yīng)用中往往是綜合使用,而最常用的是正交調(diào)制方式和多本振拼接方式[3]。正交調(diào)制方式硬件電路簡潔、調(diào)試方便,但受正交調(diào)制器性能的影響,帶寬范圍有限。多本振拼接方式帶寬范圍靈活可變,但拼接處的相位差補(bǔ)償比較困難。

本方案采用高參考時鐘的 DDS產(chǎn)生寬帶微波線性調(diào)頻源的方式。DDS選用ADI公司生產(chǎn)的最高端的AD9914作為寬帶微波線性調(diào)頻信號的核心器件[4]。AD9914是高性能直接數(shù)字頻綜,內(nèi)含12位的DAC,支持高達(dá)3.5 GS/s的采樣速率,輸出最高點(diǎn)頻可達(dá)1.5 GHz,寬帶雜散-50 dB,輸出頻率在1.396 GHz時,相位噪聲≤-128 dBc/Hz@1 kHz。AD9914采用先進(jìn)的制造工藝,不用外部操作就可以降低功率損耗。用戶通過控制3個參數(shù)(頻率、相位和幅度)來控制DDS,DDS 32位累加器提供快速的頻率跳變和頻率轉(zhuǎn)換,它的分辨率為0.23 Hz,DDS還可以進(jìn)行快速相位和幅度轉(zhuǎn)換。通過串行的輸入/輸出口編程內(nèi)部的寄存器來控制AD9914,AD9914通過靜態(tài)的RAM來產(chǎn)生頻率、相位和幅度。為了獲得更多的調(diào)制功能,可以用高速的并行數(shù)據(jù)口控制頻率、幅度和相位的調(diào)制。AD9914有四種工作模式:單音頻模式、RAM模式、鋸齒波調(diào)制模式(DRG)、并行數(shù)據(jù)傳輸模式,模式相關(guān)的數(shù)據(jù)源提供控制DDS的參數(shù),即頻率、相位、幅度,通過特殊的控制字來自動執(zhí)行頻率、相位、幅度的不同組合。

2 方案設(shè)計

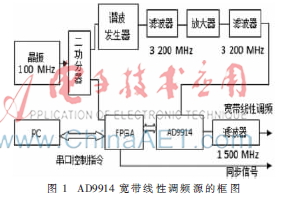

寬頻帶微波中頻信號源的設(shè)計及實(shí)現(xiàn)框圖如圖1所示。

100 MHz晶振通過二功分器,一路100 MHz信號直接激勵諧波發(fā)生器,諧波發(fā)生器按100 MHz間隔輸出梳狀譜信號,通過3 200 MHz窄帶濾波器濾波、放大、濾波輸出3 200 MHz、0 dBm的射頻信號到AD9914的系統(tǒng)時鐘輸入端。另一路100 MHz信號加到FPGA的時鐘輸入端,F(xiàn)PGA在外部計算機(jī)控制下,輸出相應(yīng)的SPI數(shù)據(jù)和控制時序到AD9914數(shù)據(jù)輸入端和時序控制端,AD9914在FPGA控制下產(chǎn)生各種相應(yīng)的寬帶微波線性調(diào)頻信號。FPGA并口控制時序電路內(nèi)部設(shè)計如圖2所示,F(xiàn)PGA并口控制時序仿真如圖3所示。

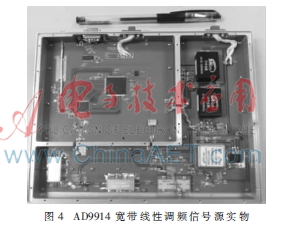

實(shí)際工作中,電源的好壞和腔體的設(shè)計直接關(guān)系到輸出信號頻譜純度。因此電路設(shè)計中為減少輸出信號的雜散,提高輸出信號的相位噪聲指標(biāo),對諧波發(fā)生器、FPGA和AD9914的電源采用兩個獨(dú)立的開關(guān)電源進(jìn)行分配,在器件近端根據(jù)不同的電源品種采用獨(dú)立的低壓差、高噪聲抑制的可調(diào)線性穩(wěn)壓電源進(jìn)行獨(dú)立供電,在電源濾波回路上串接磁珠或電感來提高電源噪聲隔離,AD9914模擬電源與數(shù)字電源進(jìn)行隔離。對3 200 MHz的窄帶濾波器采用回流焊工藝將濾波器外殼直接焊接到印制板上,以提高對100 MHz諧波信號的抑制。電源及微波部分與數(shù)字控制部分采用分腔設(shè)計。AD9914寬帶微波線性調(diào)頻信號源的實(shí)物如圖4所示。

3 測試結(jié)果

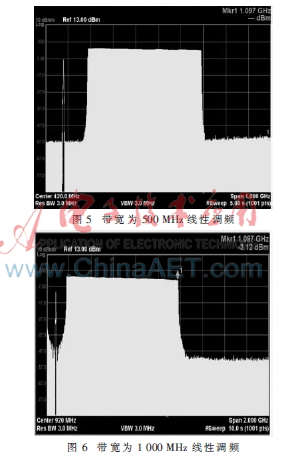

3.1 帶寬

AD9914在輸入3 200 MHz系統(tǒng)時鐘,通過輸入不同的控制指令,分別輸出帶寬為500 MHz、1 000 MHz寬帶微波中頻線性調(diào)頻信號如圖5、圖6所示。從實(shí)際信號頻譜上可以看出,AD9914輸出500 MHz寬帶微波中頻線性調(diào)頻信號幅度起伏小于1 dB,輸出1 000 MHz寬帶微波中頻線性調(diào)頻信號幅度起伏小于2.2 dB,AD9914產(chǎn)生寬帶微波中頻線性調(diào)頻信號調(diào)制斜率指標(biāo)優(yōu)于采用帶寬拼接方式,雜散指標(biāo)優(yōu)于正交調(diào)制+混頻等方式產(chǎn)生的寬帶微波中頻線性調(diào)頻信號10 dB以上。

3.2 相位噪聲與雜散

由頻譜儀測試500 MHz帶寬相位噪聲與雜散如圖7、圖8所示。相噪指標(biāo)達(dá)109.029 dB,雜散指標(biāo)為58.63 dB。

由頻譜儀測試1 000 MHz帶寬相位噪聲與雜散如圖9、圖10所示。實(shí)測相噪指標(biāo)達(dá)104.172 dB,雜散指標(biāo)為51.21 dB。

3.3 寬帶線性調(diào)頻

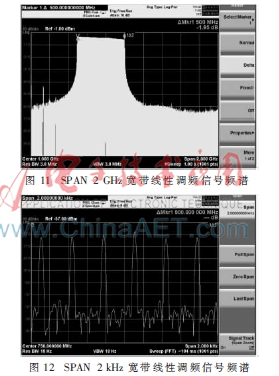

對中心頻率750 MHz、調(diào)頻帶寬500 MHz寬帶線性調(diào)頻信號在SPAN 2 GHz、SPAN 2 kHz調(diào)制信號頻譜如圖11、圖12所示。

3.4 組合線性調(diào)頻信號

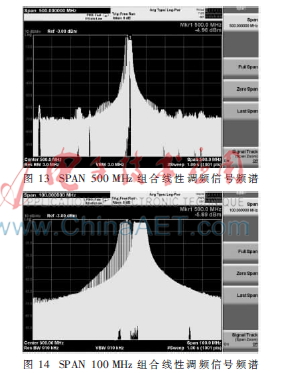

對應(yīng)中心頻率500 MHz、調(diào)頻帶寬16 MHz組合線性調(diào)頻信號在SPAN 500 MHz、SPAN 100 MHz調(diào)制信號頻譜如圖13、圖14所示。

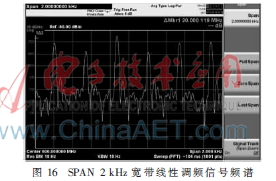

對中心頻率600 MHz、調(diào)頻帶寬1 000 MHz寬帶線性調(diào)頻信號在SPAN 2 GHz、SPAN 2 kHz調(diào)制信號頻譜如圖15、圖16所示。

4 結(jié)束語

本文介紹了基于AD9914產(chǎn)生寬帶微波中頻線性調(diào)頻信號的設(shè)計方法,通過對實(shí)物的測試和技術(shù)評估,產(chǎn)生的寬帶微波中頻線性調(diào)頻信號指標(biāo)優(yōu)于傳統(tǒng)方式產(chǎn)生的線性調(diào)頻信號,對于雷達(dá)在相應(yīng)波段的應(yīng)用,具有通信導(dǎo)航靈活、方便,發(fā)展應(yīng)用前景廣闊。

參考文獻(xiàn)

[1] 費(fèi)元春,蘇廣川.寬帶雷達(dá)信號產(chǎn)生技術(shù)[M].北京:國防工業(yè)出版社,2002.

[2] 祝明波,常文革.采用數(shù)字方法實(shí)現(xiàn)寬帶線性調(diào)頻信號

產(chǎn)生[J].系統(tǒng)工程與電子技術(shù),2000,22(5):93-96.

[3] 吳志毅.射頻電路設(shè)計技術(shù)基礎(chǔ)[M].成都:西南交通大學(xué)出版社,2014.

[4] ADI.1.6 GHz Clock Distribution IC.Dividers,Delay Adjust,Three Outputs.2005.