摘 要: 為滿(mǎn)足近鉆頭電阻率系統(tǒng)測(cè)量的需要,設(shè)計(jì)了一種32位高精度信號(hào)采集系統(tǒng)。該系統(tǒng)以?xún)?nèi)置DSP運(yùn)算單元的高性能、低功耗的信號(hào)處理芯片和FPGA為控制器,進(jìn)行信號(hào)的采集控制。實(shí)現(xiàn)了近鉆頭電阻率測(cè)量信號(hào)的采集數(shù)據(jù)轉(zhuǎn)換功能。該系統(tǒng)采用的32位高精度信號(hào)采集芯片保證了信號(hào)采集的質(zhì)量,并可穩(wěn)定地工作在井下高溫環(huán)境中。

關(guān)鍵詞: 32位高精度信號(hào)采集;FPGA;高溫環(huán)境;電阻率測(cè)量

對(duì)地層有源激勵(lì)模擬信號(hào)采集是對(duì)發(fā)射到不同地層中的電信號(hào)狀態(tài)進(jìn)行采集量化和保存的過(guò)程。它是隨鉆近鉆頭電阻率[1]測(cè)量系統(tǒng)中不可缺少的重要設(shè)備。信號(hào)采集系統(tǒng)各個(gè)單元必須能夠保證穩(wěn)定可靠地工作在井下高溫環(huán)境,并能夠準(zhǔn)確地采集信號(hào)。

1 32位模數(shù)轉(zhuǎn)換芯片簡(jiǎn)介

整個(gè)數(shù)據(jù)采集系統(tǒng)性能的關(guān)鍵是ADC芯片的選擇。經(jīng)過(guò)比較分析并基于高精度、大動(dòng)態(tài)范圍和低噪聲的考慮,本系統(tǒng)選用TI公司的ADS1282作為核心ADC器件[2]。ADS1282的主要特征有:具有高分辨率,并且在高精度模式,數(shù)據(jù)輸出率達(dá)到250 S/s時(shí)具有130 dB信噪比(SNR),甚至在低功耗模式,數(shù)據(jù)輸出率相同時(shí)信噪比(SNR)也可達(dá)127 dB;高精度特性,總諧波失真(THD)為-122 dB,積分非線(xiàn)性(INL)為0.5 ppm;可編程放大器(PGA)具有低噪聲:5 nV,放大倍數(shù)為1~64倍;在高精度模式下其功耗為25 mW,在低功耗模式下的功耗為17 mW,待機(jī)模式下為90 ?滋W,而掉電模式下僅為10 ?滋W,這能幫助系統(tǒng)在井下以電池為能源的情況下發(fā)揮更高效能。ADS1282有多種片內(nèi)數(shù)字濾波器,可選擇Sinc+FIR+IIR濾波的不同組合方式,其中FIR濾波方式可通過(guò)編程設(shè)置為線(xiàn)性或最小相位響應(yīng)。

ADS1282的內(nèi)部由多路選擇器(MUX)、4階△-Σ調(diào)制器、可編程增益放大器(PGA)、增益和失調(diào)校準(zhǔn)模塊、超量程檢測(cè)電路、控制器、可編程數(shù)字濾波器及SPI串行總線(xiàn)接口等組成[3]。

2 高精度數(shù)據(jù)采集電路設(shè)計(jì)

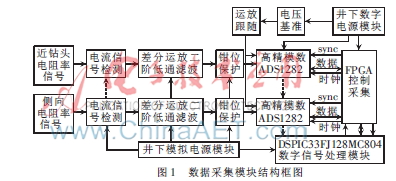

本系統(tǒng)數(shù)據(jù)采集模塊的設(shè)計(jì)結(jié)構(gòu)框圖如圖1所示。由于需要采集的是傳感器輸出的電流信號(hào),而ADS1282要求輸入是全差分電壓信號(hào),所以輸入的電流信號(hào)需要轉(zhuǎn)換為一個(gè)與電流成正比的電壓信號(hào)[4]。這可由一個(gè)高精度低溫漂的采樣電阻和跟隨器來(lái)實(shí)現(xiàn)該功能。所得到的電壓信號(hào)輸入給一個(gè)二階模擬低通濾波器,該低通濾波器由一個(gè)全差分輸出運(yùn)算放大器構(gòu)成,在此起到濾去高頻噪聲的功能。其輸出經(jīng)過(guò)鉗位保護(hù)后,直接輸入到高精度的模數(shù)轉(zhuǎn)換器的差分輸入端。鉗位保護(hù)由鉗位二極管構(gòu)成,用于保護(hù)ADSl282的輸入信號(hào)瞬時(shí)超載。當(dāng)輸入信號(hào)電平超出二極管的額定值時(shí),該鉗位二極管可對(duì)輸入進(jìn)行鉗位,實(shí)現(xiàn)電平保護(hù)的功能。電壓基準(zhǔn)源芯片和運(yùn)放跟隨器組成的ADS1282的基準(zhǔn)源,這樣的組合可提高電壓基準(zhǔn)源芯片攜帶負(fù)載的能力。井下電源模塊將電源的電壓變換成各個(gè)芯片單元所需要的電壓。模數(shù)轉(zhuǎn)換器的數(shù)字通信接口直接接至FPGA,由FPGA構(gòu)建的SPI總線(xiàn)來(lái)讀取轉(zhuǎn)換得到的數(shù)據(jù)[5]。

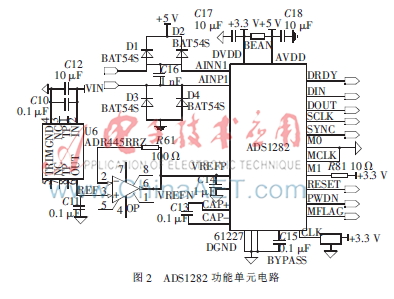

2.1 ADS1282信號(hào)采集單元電路

ADS1282為該采集系統(tǒng)的核心,其單元電路如圖2所示,ADSl282的信號(hào)輸入端為差分輸入,可以有效地抑制共模噪音。為保護(hù)A/D輸入端,需要在輸入端放置鉗位二極管D1、D2、D3和D4,這樣如果輸入電壓超過(guò)從AVDD到AVSS的范圍時(shí)就會(huì)被鉗位在這個(gè)范圍內(nèi)。VREFP和VREFN分別連接到參考電壓和AVSS。ADS1282使用ADR445B來(lái)提供基準(zhǔn)電壓。該芯片具有極低的噪聲,極低的溫飄(1 ppm/℃),寬的工作溫度范圍(-40℃~+125℃)。由于參考電壓源攜帶負(fù)載的能力有限,為防止ADS1282的參考輸入端瞬時(shí)電流輸入較大,拉低參考電壓,造成參考電壓不穩(wěn)定并影響測(cè)量,需要在其后接入運(yùn)放跟隨器,增強(qiáng)基準(zhǔn)電壓的輸出電流并提高攜帶負(fù)載能力,以減少因負(fù)載變化而產(chǎn)生的紋波噪聲。由于ADS1282的調(diào)制器直接輸出端M0、M1和MCLK不能懸空,因此必須接入固定電平,保持其工作穩(wěn)定。ADS1282的SCLK、DOUT和DIN輸入端,與FPGA內(nèi)部編程形成的SPI數(shù)據(jù)總線(xiàn)模塊連接。DRDY引腳由FPGA檢測(cè),當(dāng)A/D的數(shù)據(jù)采樣轉(zhuǎn)換完成時(shí)該引腳為低電平,F(xiàn)PGA檢測(cè)到該引腳為低電平時(shí),開(kāi)始從SPI總線(xiàn)上讀取數(shù)據(jù)。RESET、PWDN和SYNC被FPGA內(nèi)部的控制模塊控制,完成重啟、低功耗待機(jī)和同步采集功能。

2.2前模擬檢測(cè)電路

由于反應(yīng)地層電阻率的電流信號(hào)非常微弱,對(duì)其檢測(cè)精度的要求很高,因此前級(jí)處理電路結(jié)構(gòu)和器件選擇很重要。運(yùn)算放大器需選用高共模抑制比、高精度、低漂移和低噪聲的器件。

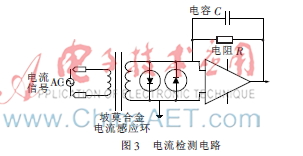

電流檢測(cè)電路如圖3所示,近鉆頭電阻率的最前端為電流互感器,其輸出為微弱電流信號(hào)。輸入的電流信號(hào)經(jīng)過(guò)一個(gè)I/V轉(zhuǎn)換電路后得到與之成正比的電壓信號(hào)[6]。I/V轉(zhuǎn)換電路中運(yùn)放的反饋采樣電阻R選擇非常重要,其性能直接影響所得的電壓信號(hào)的穩(wěn)定性和精度。

選用VISHAY公司生產(chǎn)的VSMP系列超精密金屬箔電阻,它具有極好的穩(wěn)定性,并且其溫漂接近于零,具有極低的噪聲和極高的阻值精度。調(diào)節(jié)電阻R的值可以改變運(yùn)算放大器輸出的電壓值,而電容C用來(lái)補(bǔ)償相位差,調(diào)節(jié)運(yùn)放帶寬增益積范圍內(nèi)的相位裕度,其也可去除干擾尖峰信號(hào)。由于電流互感器次級(jí)和初級(jí)線(xiàn)圈數(shù)比非常大,當(dāng)有意外大電流流入初級(jí)時(shí),為避免次級(jí)產(chǎn)生過(guò)高的電壓對(duì)電子元器件產(chǎn)生有害(或不良)的影響,采用了兩個(gè)反向并聯(lián)的二極管。

該跟隨緩沖運(yùn)放選用AD829,該芯片同樣具有極低的噪聲(1.7 nV/Hz)、高壓擺率(230 V/?滋s)、寬通頻帶(50 MHz以上)、很高的共模抑制比(120 dB)、高開(kāi)環(huán)增益、低輸出偏置電壓、極低的溫度漂移和寬的電源電壓(±15 V)等特性。工作溫度范圍為-55 ℃~+125 ℃,完全適合于井下高溫工作環(huán)境。

2.3 ADS1282信號(hào)調(diào)理電路

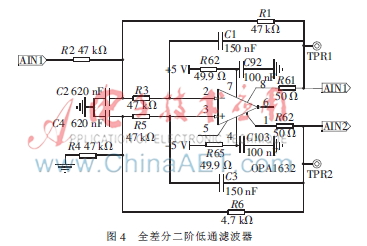

ADS1282的輸入是采用差分電壓輸入形式,差分輸入最明顯的優(yōu)勢(shì)在于其抗干擾能力強(qiáng),并能有效抑制自身對(duì)外界的電磁干擾。當(dāng)環(huán)境存在電磁噪聲干擾時(shí),噪聲會(huì)同時(shí)被耦合到兩條信號(hào)線(xiàn)上,再經(jīng)兩信號(hào)差值后,電磁干擾噪聲信號(hào)幾乎被抵消。并且全差分兩根信號(hào)線(xiàn)上的電信號(hào)對(duì)其他電路輻射的電磁場(chǎng)也可以相互抵消[7]。

由于模數(shù)轉(zhuǎn)換器的輸入端是差分形式,而前端模擬檢測(cè)電路是單端輸出的,因此,需要一個(gè)低噪聲的單端輸入差分輸出的模擬信號(hào)調(diào)理電路來(lái)連接。單端轉(zhuǎn)差分電路主要有兩種方式,一是用多個(gè)運(yùn)算放大器構(gòu)成差分輸出;二是使用全差分運(yùn)放芯片。第一種方法使用多個(gè)運(yùn)放,運(yùn)放的性能和溫漂指標(biāo)會(huì)有一定差距,不可避免地引入了更多的噪聲。而專(zhuān)用全差分運(yùn)放芯片外圍結(jié)構(gòu)簡(jiǎn)單,所用的分立器件很少,因此本系統(tǒng)選取單片全差分運(yùn)算放大器 OPA1632,并用其構(gòu)成濾波功能和模擬信號(hào)調(diào)理電路。

OPA1632是一款高性能和低噪聲的全差分運(yùn)算放大器。信號(hào)失真低,芯片噪聲降低至1.3 nV/Hz。使用OPA1632構(gòu)成二階巴特沃斯低通濾波器,通過(guò)選取不同的電阻電容組合可以實(shí)現(xiàn)濾波器通頻帶寬的改變,如圖4所示。二階巴特沃斯濾波器可以在通頻帶內(nèi)達(dá)到頻率響應(yīng)曲線(xiàn)的最大平坦度,而在阻頻帶則逐漸下降為零。

由于全差分運(yùn)算放大器構(gòu)成的對(duì)稱(chēng)性,在電路設(shè)計(jì)中R1=R6,R2=R4,R3=R5,C1=C3,C2=C4,該二階巴特沃斯濾波器電路的特征頻率為:

![`G5H$UI0~]5)UZ2SIG%M[}9.jpg `G5H$UI0~]5)UZ2SIG%M[}9.jpg](http://files.chinaaet.com/images/2015/05/27/6356835916975079698136788.jpg)

3 高精度數(shù)據(jù)采集軟件設(shè)計(jì)

3.1 ADS1282讀寫(xiě)控制

在ADS1282上電后,其開(kāi)始自動(dòng)采集,在數(shù)據(jù)采集轉(zhuǎn)換完成后DRDY引腳會(huì)產(chǎn)生低電平脈沖,需要在ADC工作前對(duì)其進(jìn)行讀取器件ID操作和初始化操作,用以驗(yàn)證SPI總線(xiàn)上工作時(shí)序是否正確并對(duì)ADC進(jìn)行初始化設(shè)置。通過(guò)邏輯分析儀可以記錄SPI數(shù)據(jù)總線(xiàn)上的時(shí)鐘和數(shù)據(jù)信息并進(jìn)行分析。

讀取器件ID首先發(fā)送停止自動(dòng)采集命令(0X11),時(shí)序圖如圖5所示,從邏輯分析儀采集的結(jié)果可以看出ADS1282接收到該命令后就停止了自動(dòng)采集(MISO自動(dòng)輸出停止)。

讀取ID命令時(shí)序圖如圖6所示。發(fā)送讀寄存器指令+寄存器地址(0X21),發(fā)送0X00代表只讀取一個(gè)寄存器。最后ADS1282返回ID:0X20,證明SPI時(shí)序正確并與ADS1282成功進(jìn)行通信。

初始化設(shè)置ADS1282的配置寄存器0,其主要設(shè)置配置寄存器0的第6位為MODE=1,采用高分辨率模式,DR[2:0]=010:數(shù)據(jù)輸出率為1 000 S/s,Digital Filter Select FILTR[1:0]=10:Sinc+LPF filter blocks數(shù)字濾波器選擇。然后對(duì)ADS1282配置寄存器0數(shù)據(jù)讀回判斷配置結(jié)果是否正確,讀回?cái)?shù)據(jù)如圖7所示。

首先發(fā)送停止自動(dòng)采集命令(0X11),然后發(fā)送讀寄存器指令+寄存器地址(0X21),發(fā)送0X00代表讀取從地址0X01開(kāi)始的一個(gè)寄存器。最后ADS1282返回config0:0X052,證明初始化配置寄存器0成功。

3.2 FPGA控制ADSl282工作流程

外部器件通過(guò)串行接口(SPI)來(lái)訪(fǎng)問(wèn)ADSl282的數(shù)據(jù)和設(shè)置寄存器。ADSl282輸出的轉(zhuǎn)換數(shù)據(jù)是32 bit寬的二進(jìn)制補(bǔ)碼的格式,其中最高位是符號(hào)位,“0”表示正數(shù),“1”表示負(fù)。SPI接口引腳包括SCLK、DIN及DOUT三路基本信號(hào)引腳。數(shù)據(jù)在時(shí)鐘引腳SCLK的上升沿移入數(shù)據(jù)輸入引腳DIN,在時(shí)鐘引腳SCLK的下降沿移出數(shù)據(jù)輸出引腳DOUT。DRDY引腳是輸出信號(hào),當(dāng)其為低電平時(shí),新的轉(zhuǎn)換數(shù)據(jù)已準(zhǔn)備好可以被外部器件讀出了。FPGA可以通過(guò)判斷該引腳電平的狀態(tài)來(lái)決定讀取數(shù)據(jù)時(shí)刻。當(dāng)SPI總線(xiàn)時(shí)鐘引腳SCLK無(wú)效時(shí)需保持低電平。

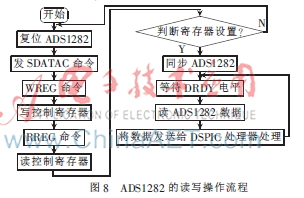

FPGA芯片通過(guò)SPI通信總線(xiàn)和相關(guān)控制引腳對(duì)ADS1282進(jìn)行初始化設(shè)置和讀寫(xiě)控制,對(duì)ADS1282的操作流程如圖8所示,具體操作如下。

(1)對(duì)數(shù)模轉(zhuǎn)換芯片進(jìn)行復(fù)位操作,即在復(fù)位引腳RESET施加低電平脈沖,芯片對(duì)內(nèi)部寄存器進(jìn)行復(fù)位操作,并且是內(nèi)部寄存器的值恢復(fù)到出廠默認(rèn)設(shè)置。復(fù)位脈沖結(jié)束后需要至少100 ms的延時(shí)間隔,再進(jìn)行其他操作,保證芯片內(nèi)部寄存器初始化工作完畢。

(2)向數(shù)模轉(zhuǎn)換芯片發(fā)送停止連續(xù)讀數(shù)據(jù)命令(SDATAC、0X11),使芯片停止向外部器件發(fā)送采集轉(zhuǎn)換完成的數(shù)據(jù),讀寫(xiě)時(shí)序如圖5所示。

(3)向數(shù)模轉(zhuǎn)換芯片發(fā)送寫(xiě)寄存器命令(WREG),然后配置需要設(shè)置的寄存器位形成相應(yīng)的命令字,并通過(guò)SPI數(shù)據(jù)總線(xiàn)寫(xiě)入配置寄存器中,完成芯片工作前工作方式的設(shè)置,保證芯片按照編程的方式工作。

(4)向數(shù)模轉(zhuǎn)換芯片發(fā)送讀寄存器命令(RREG),把寫(xiě)入到芯片寄存器中的數(shù)據(jù)讀出來(lái),并與寫(xiě)入寄存器時(shí)的數(shù)據(jù)進(jìn)行對(duì)比。不一致時(shí)則需要重新開(kāi)始第一步操作。

(5)通過(guò)外部引腳(SYNC)同步ADC工作時(shí)序,使得兩路ADC同時(shí)開(kāi)始采集數(shù)據(jù)。

(6)等待數(shù)據(jù)采集轉(zhuǎn)換完成,信號(hào)引腳(DRDY)的低電平脈沖到來(lái),F(xiàn)PGA通過(guò)SPI總線(xiàn)讀取采集到的數(shù)據(jù),然后把讀取的數(shù)據(jù)通過(guò)串口發(fā)送給DSPIC33FJ128MC804數(shù)字信號(hào)處理芯片,用于進(jìn)一步對(duì)數(shù)據(jù)進(jìn)行分析。數(shù)據(jù)發(fā)送完成后,返回判斷DRDY引腳的狀態(tài),等待下一個(gè)采樣轉(zhuǎn)換完成的數(shù)據(jù),如此循環(huán)工作。

在對(duì)該采集系統(tǒng)進(jìn)行井下試驗(yàn)后,由于發(fā)射到地層中的100 Hz正弦電流信號(hào)經(jīng)過(guò)地層后被接收端接收并放大,如圖9所示,該信號(hào)含有大量的噪聲,但經(jīng)過(guò)傅里葉頻譜分析可以看到該信號(hào)的基頻與發(fā)射信號(hào)頻率相同。該采集系統(tǒng)可準(zhǔn)確采集流經(jīng)地層的電流信號(hào)。

本文根據(jù)實(shí)際應(yīng)用中對(duì)高精度數(shù)據(jù)采集處理的要求,設(shè)計(jì)出了一個(gè)應(yīng)用于井下的基于FPGA以及32位高精度ADC為核心的高精度數(shù)據(jù)采集系統(tǒng)。提出了采用TI公司的32位高精度ADC芯片ADS1282為數(shù)據(jù)轉(zhuǎn)換核心的高精度數(shù)據(jù)轉(zhuǎn)換模塊。根據(jù)設(shè)計(jì)方案對(duì)整個(gè)系統(tǒng)的各個(gè)功能電路進(jìn)行詳細(xì)設(shè)計(jì),并最終研制完成了該系統(tǒng)。

參考文獻(xiàn)

[1] 蘇義腦,竇修榮.隨鉆測(cè)量、隨鉆測(cè)井與錄井工具[J].石油鉆采工藝,2005,27(1):15-17.

[2] 王琳,商周,王學(xué)偉.?dāng)?shù)據(jù)采集系統(tǒng)的發(fā)展與應(yīng)用[J].電測(cè)與儀表,2004,41(8):4-8.

[3] 張春燕.用于數(shù)據(jù)采集的Sigma-Delta調(diào)制器的設(shè)計(jì)與實(shí)現(xiàn)[D].上海:上海大學(xué),2007.

[4] 于麗霞,王福明.微弱信號(hào)檢測(cè)技術(shù)綜述[J].信息技術(shù),2007(2):115-116.

[5] 牛清紅,張春熹,宋凝芳.用A/D和FPGA實(shí)現(xiàn)的加速度計(jì)數(shù)據(jù)讀出系統(tǒng)[J].中國(guó)慣性技術(shù)學(xué)報(bào),2006,14(1):63-64.

[6] 林春方,社先彬,郭立.基于I/F變換的弱電流測(cè)量?jī)x的研制[J].上海交通大學(xué)學(xué)報(bào),2006,40(9):1517-1518.

[7] 李素芬,李剛,孫景發(fā).模數(shù)轉(zhuǎn)換技術(shù)及其發(fā)展[J].電子技術(shù)應(yīng)用,2002,28(4):72-74.