捷聯(lián)慣性組合導(dǎo)航系統(tǒng)是一種完全自主的定位導(dǎo)航系統(tǒng),它可以連續(xù)實(shí)時(shí)地提供位置、速度和姿態(tài)信息,短時(shí)精度較高,但誤差隨時(shí)間增長(zhǎng)而不斷積累。GPS導(dǎo)航系統(tǒng)能夠全天候提供信息,且誤差不隨時(shí)間積累。因此,將它們組合起來,利用卡爾曼濾波技術(shù)進(jìn)行融合,可以發(fā)揮各自優(yōu)勢(shì),提高導(dǎo)航精度。由于捷聯(lián)系統(tǒng)沒有穩(wěn)定的物理平臺(tái),慣性器件測(cè)量的數(shù)值不能直接進(jìn)行導(dǎo)航計(jì)算,必須先經(jīng)過大量、實(shí)時(shí)、精確的數(shù)學(xué)運(yùn)算建立起數(shù)學(xué)平臺(tái),才能得到導(dǎo)航參數(shù),在計(jì)算上較復(fù)雜,對(duì)計(jì)算機(jī)的性能要求高。為減小體積、重量和增加可靠性。文中提出利用PC104嵌入式工控機(jī)和FPGA設(shè)計(jì)一種雙CPU結(jié)構(gòu)的捷聯(lián)慣性組合導(dǎo)航系統(tǒng)。系統(tǒng)中PC/104總線結(jié)構(gòu)的嵌入式工控機(jī)來承擔(dān)姿態(tài)解算任務(wù),采用FPGA控制組合系統(tǒng)的采集模塊,并利用其內(nèi)部資源,設(shè)計(jì)了雙口RAM模塊、串口接口模塊等。雙CPU系統(tǒng)使PC104可以專注于解算,保證了系統(tǒng)的實(shí)時(shí)性。

1 捷聯(lián)慣性組合導(dǎo)航系統(tǒng)總體方案

捷聯(lián)慣導(dǎo)系統(tǒng)是將加速度計(jì)和陀螺儀沿載體坐標(biāo)系安裝,在進(jìn)行導(dǎo)航參數(shù)計(jì)算時(shí),需要是導(dǎo)航坐標(biāo)系中的量。因此應(yīng)先將慣性器件測(cè)得的比力和角加速度誤差補(bǔ)償后送入計(jì)算機(jī)進(jìn)行實(shí)時(shí)計(jì)算,可以得到將比力從載體坐標(biāo)系轉(zhuǎn)換到導(dǎo)航坐標(biāo)系的姿態(tài)矩陣。通過姿態(tài)矩陣可以確定載體的姿態(tài)信息。姿態(tài)矩陣常用的即時(shí)修正方法有歐拉角法、方向余弦法和四元數(shù)法,設(shè)計(jì)采用四元數(shù)法。為進(jìn)行導(dǎo)航解算,選取地理坐標(biāo)系為導(dǎo)航坐標(biāo)系,三軸分別指向東向、北向和天向。

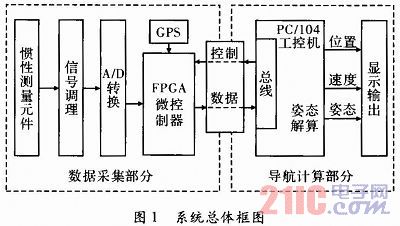

根據(jù)捷聯(lián)慣性組合導(dǎo)航系統(tǒng)的特點(diǎn),提出采用PC104總線嵌入式工控機(jī)的捷聯(lián)慣性組合導(dǎo)航系統(tǒng)的硬件設(shè)計(jì)方案,系統(tǒng)包括數(shù)據(jù)采集和數(shù)據(jù)解算模塊。數(shù)據(jù)采集模塊由FPGA負(fù)責(zé)控制A/D轉(zhuǎn)換將陀螺儀和加速度計(jì)輸出的模擬信號(hào)轉(zhuǎn)換為數(shù)字信號(hào)。在FPGA內(nèi)部開辟一塊存儲(chǔ)單元,F(xiàn)PGA讀取A/D的轉(zhuǎn)換結(jié)果存放在內(nèi)嵌的雙口RAM中。FPGA通過雙口RAM與PC104進(jìn)行實(shí)時(shí)通信,F(xiàn)PGA把采集的數(shù)據(jù)進(jìn)行處理后送入雙口RAM中,然后發(fā)中斷信號(hào)給PC104,通知其已經(jīng)有數(shù)據(jù)可以處理。PC104收到中斷信號(hào)后,將雙口RAM中的數(shù)據(jù)取走進(jìn)行處理和解算。FPGA和PC104同時(shí)工作,提高了系統(tǒng)的運(yùn)行速度。系統(tǒng)要求數(shù)據(jù)采樣頻率為1kHz,數(shù)據(jù)解算頻率為100Hz,外加時(shí)鐘頻率為40MHz。

2 系統(tǒng)硬件設(shè)計(jì)

數(shù)據(jù)采集部分采用Altera公司的EP2C35F672,它是CycloneⅡ系列產(chǎn)品之一,一個(gè)LAB中有16個(gè)LE,增加了乘法器模塊,增強(qiáng)了DSP處理能力。由33 216個(gè)LE組成,片上有105個(gè)M4K RAM塊,片內(nèi)有35個(gè)18 x 18個(gè)硬件乘法器,片上有4個(gè)PLL,可以實(shí)現(xiàn)多個(gè)時(shí)鐘域。PC104總線結(jié)構(gòu)嵌入式工控機(jī)具有功耗低、單5 V供電、工作溫度范圍寬、可靠性高、抗震性好、結(jié)構(gòu)小巧緊湊、浮點(diǎn)運(yùn)算能力強(qiáng)、運(yùn)算速度快等顯著特點(diǎn)。最適合在嵌入式控制系統(tǒng)中應(yīng)用。因此它是開發(fā)導(dǎo)航計(jì)算機(jī)的理想方案。

2.1 數(shù)據(jù)采集模塊

數(shù)據(jù)采集部分由慣性測(cè)量元件、GPS接收機(jī)、信號(hào)調(diào)理部分、A/D轉(zhuǎn)換電路和FPGA控制器等構(gòu)成。在這部分中,F(xiàn)PGA主要完成同步產(chǎn)生A/D轉(zhuǎn)換的時(shí)序,數(shù)字濾波和存儲(chǔ)經(jīng)A/D轉(zhuǎn)換后的陀螺和加表的數(shù)據(jù)。慣性測(cè)量元件主要包括3個(gè)加速度計(jì)和3個(gè)陀螺儀,正交安裝于坐標(biāo)系的X軸、Y軸和Z軸,用于提供載體在載體坐標(biāo)系上的比力和角速度,采用模擬信號(hào)輸出,加速度計(jì)采用差分輸出。由于慣性器件安裝在一個(gè)密閉的容器中,受溫度影響也比較大,必須采集溫度信號(hào)對(duì)慣性器件進(jìn)行補(bǔ)償。A/D轉(zhuǎn)換電路采用TI公司的A/D芯片ADS1258,ADS1258是一個(gè)靈活的、24位低噪聲最優(yōu)化的、快速的、多通道的、高分辨率的模擬/數(shù)字轉(zhuǎn)換芯片。24位的精度是0.000 000 06,其理論值較16位A/D有較大的提高。根據(jù)芯片資料,ADS1258中的轉(zhuǎn)換器可以提供最大23.7ksample/s的通道掃描速度,可以在<700μs的時(shí)間里完成一個(gè)完整的16通道掃描。模擬電壓輸入范圍為±2.5V。

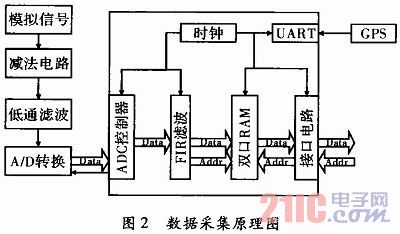

數(shù)據(jù)采集部分的功能之一是將加速度計(jì)和陀螺儀輸出的模擬信號(hào)轉(zhuǎn)換為數(shù)字信號(hào),并將這一數(shù)字信號(hào)送入導(dǎo)航計(jì)算機(jī)。為提高系統(tǒng)的精度,在A/D轉(zhuǎn)換前要先將加速度計(jì)和陀螺儀輸出的信號(hào)進(jìn)行放大,通過減法電路和低通濾波電路進(jìn)行調(diào)理,然后再通過FPGA控制AD1258進(jìn)行轉(zhuǎn)換。讀取轉(zhuǎn)換數(shù)據(jù),利用FPGA內(nèi)部邏輯設(shè)計(jì)FIR數(shù)字濾波器,將處理后的數(shù)據(jù)送入FPGA內(nèi)部的雙口RAM,向主CPU發(fā)出數(shù)據(jù)準(zhǔn)備好中斷。這些由FPGA控制,保證了PC104實(shí)時(shí)處理和接收到的數(shù)據(jù)。用FPGA這種純硬件結(jié)構(gòu)實(shí)現(xiàn)的數(shù)據(jù)采集系統(tǒng)比用MCU等器件用軟件控制的數(shù)據(jù)采集系統(tǒng)速度快,且容易修改。

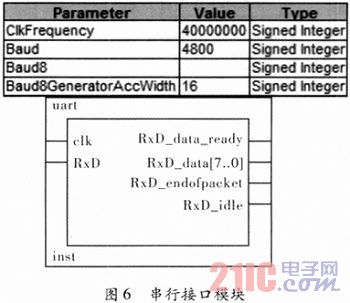

采集模塊的另一個(gè)功能是進(jìn)行GPS數(shù)據(jù)采集。GPS輸出經(jīng)度、緯度和速度等信息。設(shè)計(jì)采用Jupitre21 GPS OEM模塊,體積小、重量輕、功耗低,首次定位和重新捕獲時(shí)間短,具有強(qiáng)大的抗干擾、抗遮擋能力。OEM板的輸入、輸出格式均按RS232串口通信協(xié)議,設(shè)定為8個(gè)數(shù)據(jù)位,1個(gè)起始位,1個(gè)停止位,無奇偶校驗(yàn)。GPS接收機(jī)數(shù)據(jù)輸出通過RS-232串行口,它信號(hào)輸出的頻率比較低,大約每秒更新一次,接收的數(shù)據(jù)要完成解碼才能用于組合系統(tǒng)的修正。本系統(tǒng)用FPGA實(shí)現(xiàn)RS232接口,用于接收GPS的數(shù)據(jù)。

2.2 導(dǎo)航解算模塊

導(dǎo)航解算模塊是捷聯(lián)慣性組合導(dǎo)航系統(tǒng)的核心。該部分的功能主要完成姿態(tài)矩陣的即時(shí)修正、位置姿態(tài)信息的求取和卡爾曼濾波等運(yùn)算。要求導(dǎo)航計(jì)算機(jī)對(duì)浮點(diǎn)數(shù)據(jù)的處理能力強(qiáng),并且整個(gè)導(dǎo)航計(jì)算中涉及大量的矩陣計(jì)算,運(yùn)算量較大。PC104采用中斷機(jī)制工作,需要處理FPGA數(shù)據(jù)準(zhǔn)備好中斷請(qǐng)求、導(dǎo)航計(jì)算、濾波計(jì)算。

2.3 FPGA和PC104之間的通信

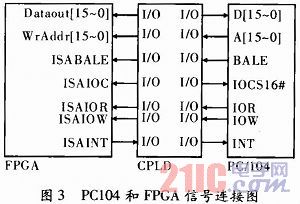

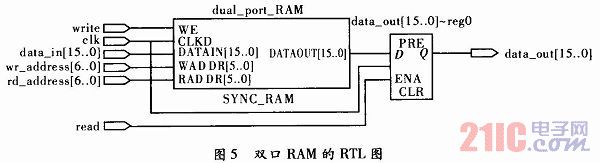

設(shè)計(jì)采用兩個(gè)控制器結(jié)構(gòu),PC104要進(jìn)行導(dǎo)航解算,就要將FPGA采集處理后的數(shù)據(jù)接收。若通過FIFO來傳遞數(shù)據(jù),由于FIFO的先進(jìn)先出原則,則存在一個(gè)采用頻率和解算速率的配合問題。而系統(tǒng)又要求較好的實(shí)時(shí)性,即每次要進(jìn)行解算都能立即得到最新的實(shí)時(shí)數(shù)據(jù)。雙口RAM方式無論是通信速率還是硬件實(shí)現(xiàn)的難易程度上都是處理器問高速通信的最佳選擇。系統(tǒng)采用雙口RAM實(shí)現(xiàn)FPGA和PC104之間的數(shù)據(jù)共享。

雙口RAM存儲(chǔ)器具有兩套獨(dú)立的讀寫控制線、地址線和數(shù)據(jù)線。可以自由訪問,互不干擾。用FPGA實(shí)現(xiàn)雙口RAM的功能可以較好地解決并行性和速度問題,而且其靈活的可配置特性使得基于FPGA的雙口RAM易于進(jìn)行修改、測(cè)試及系統(tǒng)升級(jí),可降低設(shè)計(jì)成本,縮短開發(fā)周期,減小了導(dǎo)航計(jì)算機(jī)的體積。因此本設(shè)計(jì)直接采用FPGA構(gòu)建雙口RAM,同時(shí)進(jìn)行讀寫操作控制。PC104總線上的I/O地址范圍為0000H~FFFFH,選取地址段0200H~027FH作為雙口RAM的地址段,共128個(gè)地址單元。FPGA與PC104引腳電平不同,F(xiàn)PGA的I/O口供電電壓為3.3 V,PC104的總線為5 V TTL電平。因此,為使系統(tǒng)安全穩(wěn)定地工作,需要一個(gè)電平轉(zhuǎn)換器件。在PC104和FPGA之間使用起電平轉(zhuǎn)換作用的CPLD,同時(shí)由它產(chǎn)生地址譯碼電路。###反應(yīng)###

3 軟件設(shè)計(jì)

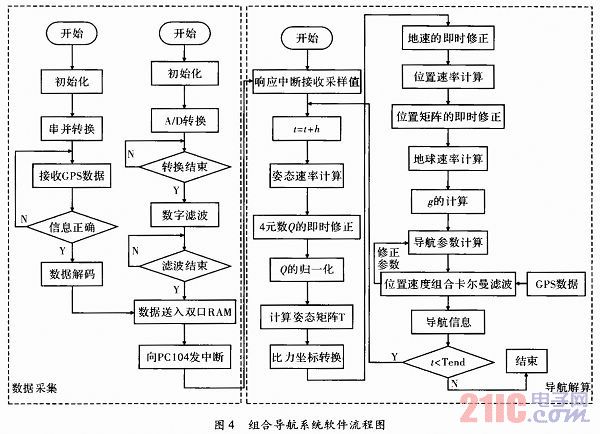

軟件設(shè)計(jì)以滿足導(dǎo)航參數(shù)解算為主,采集模擬的慣性測(cè)量器件及GPS數(shù)據(jù),通過雙CPU之間的軟硬件形成呼叫和應(yīng)答機(jī)制。由FPGA負(fù)責(zé)加速度計(jì)和陀螺儀輸出信息的采集及數(shù)據(jù)處理,采用FPGA接收讀取GPS的數(shù)據(jù);PC/104工控機(jī)負(fù)責(zé)對(duì)FPGA采集到的數(shù)據(jù)進(jìn)行解算。對(duì)控制采樣及數(shù)據(jù)處理模塊的軟件設(shè)計(jì)主要是控制A/D轉(zhuǎn)換,構(gòu)建內(nèi)部存儲(chǔ)器、數(shù)字濾波器和串行接口等,采用硬件描述語言Verilog HDL。組合系統(tǒng)的解算由PC104完成,對(duì)PC104的軟件設(shè)計(jì)采用C語言在DOS系統(tǒng)下在Turbo C中編寫,導(dǎo)航解算應(yīng)有不同的解算周期。因此,導(dǎo)航計(jì)算機(jī)系統(tǒng)軟件設(shè)計(jì)分為FPGA軟件和PC/104主控系統(tǒng)軟件兩部分。

3.1 FPGA軟件設(shè)計(jì)

FPGA是按照主CPU的指令來執(zhí)行對(duì)加速度計(jì)的數(shù)據(jù)采集和數(shù)據(jù)處理任務(wù),然后將預(yù)處理的結(jié)果寫入雙端口RAM,供PC/104使用。FPGA內(nèi)部的邏輯塊包括時(shí)鐘、A/D控制器、數(shù)字濾波器、雙口RAM、接口單元等。數(shù)字濾波器的設(shè)計(jì)直接采用設(shè)計(jì)好的FIR濾波器的IP核。通過Verilog HDL語言對(duì)雙口RAM的描述可以在FPGA內(nèi)部實(shí)現(xiàn)雙口RAM,并且進(jìn)行讀寫控制。雙口RAM在使用上需要注意的問題就是,可能會(huì)發(fā)生共享沖突,出現(xiàn)寫入值和讀出值出現(xiàn)混亂的狀態(tài)。設(shè)計(jì)采用文獻(xiàn)的方法設(shè)計(jì)雙口RAM沖突解決方案。

在FPGA內(nèi)部實(shí)現(xiàn)一個(gè)串口模塊,采用GPS接收機(jī)默認(rèn)的4 800 bit·s-1,首先將系統(tǒng)的40 MHz時(shí)鐘進(jìn)行分頻,一般對(duì)數(shù)據(jù)進(jìn)行過采樣,以便正確接收GPS接收機(jī)的數(shù)據(jù)。取過采樣頻率為波特率的8倍。有了4 800×8 Hz的頻率之后,進(jìn)行串并轉(zhuǎn)換。為防止毛刺信號(hào)被誤認(rèn)為是起始信號(hào),定義一個(gè)2位的計(jì)數(shù)器進(jìn)行判斷起始位4次。接著用狀態(tài)機(jī)實(shí)現(xiàn)對(duì)起始位、數(shù)據(jù)和停止位的檢測(cè),就可進(jìn)行數(shù)據(jù)的接收。通過Verilog HDL語言編寫接收GPS數(shù)據(jù)程序,采用狀態(tài)機(jī)方法檢測(cè)GPS數(shù)據(jù)起始符,本系統(tǒng)采用$GPRMC,(UTC時(shí)間),A,(緯度信息),N,(經(jīng)度信息),E,(速度信息),289.0,020710,10.3,W×5B協(xié)議,本系統(tǒng)只用位置和速度信息對(duì)捷聯(lián)慣導(dǎo)系統(tǒng)進(jìn)行校正。接收到的GPS數(shù)據(jù)為對(duì)應(yīng)ASCII值的二進(jìn)制數(shù)。

3.2 PC104軟件設(shè)計(jì)

數(shù)據(jù)解算采用PC104為核心處理器。采集的陀螺和加速度計(jì)的信息經(jīng)過誤差補(bǔ)償后,將陀螺儀測(cè)量的角速度數(shù)據(jù)進(jìn)行解算,得到姿態(tài)矩陣,再用姿態(tài)矩陣將沿載體坐標(biāo)系的加速度測(cè)量的比力信息轉(zhuǎn)換到導(dǎo)航坐標(biāo)系上,進(jìn)行積分運(yùn)算,同時(shí)根據(jù)姿態(tài)矩陣中的元素可以解算出姿態(tài)角信息。再用GPS測(cè)量得到的位置、速度信息和捷聯(lián)慣導(dǎo)系統(tǒng)解算得到的位置、速度的差值作為觀測(cè)量,通過卡爾曼濾波,修正導(dǎo)航系統(tǒng)的參數(shù),為慣性元件提供誤差修正,以提高導(dǎo)航精度。將得到的位置、速度、姿態(tài)等信息輸出,進(jìn)行控制載體。PC104對(duì)雙口RAM的端口地址讀/寫操作的函數(shù)為inport(int protid)和outport(int portid,int value),protid為端口地址,value為要發(fā)送數(shù)據(jù)。

4 結(jié)束語

文中以PC104為核心處理器,輔以FPGA控制采集和A/D轉(zhuǎn)換,形成雙CPU協(xié)作模式,通過雙口RAM進(jìn)行通信,主CPU可以專心進(jìn)行導(dǎo)航計(jì)算,避免了因數(shù)據(jù)采集工作而降低效率。雙CPU并行工作,相互配合,大大地提高了系統(tǒng)的整體效率。系統(tǒng)體積小、精度高、結(jié)構(gòu)簡(jiǎn)單、功耗小。將導(dǎo)航參數(shù)通過串口輸出,可應(yīng)用于船舶、車輛、飛機(jī)等,能滿足導(dǎo)航和定位的要求。