摘要:根據(jù)有限沖擊響應(yīng)(FIR)數(shù)字濾波器的原理,綜合運(yùn)用Matlab" title="Matlab">Matlab和FPGA" title="FPGA">FPGA的QuartusⅡ" title="QuartusⅡ">QuartusⅡ兩大計(jì)算機(jī)軟件,提出了一種利用QuartusⅡ中參數(shù)化宏功能模塊(LPM)的FIR濾波器設(shè)計(jì)方法。首先利用Matlab設(shè)計(jì)濾波器系數(shù),再利用QuartusⅡ的LPM構(gòu)造的乘法器和加法器,最終得到濾波結(jié)果。相比分布式算法,該法在信號(hào)處理速率要求不高,且濾波器階數(shù)較高的情況下,可更加簡(jiǎn)單地實(shí)現(xiàn)濾波效果。最終在Matlab和Quar-tusⅡ的基礎(chǔ)上,實(shí)現(xiàn)了64階的高階FIR數(shù)字濾波器電路的設(shè)計(jì)與仿真。

關(guān)鍵詞:FlR濾波器;Matlab QuartusⅡ;參數(shù)化功能模塊庫(kù)

相對(duì)無(wú)限沖擊響應(yīng)(IIR)濾波器,有限沖擊響應(yīng)(FIR)能夠在滿足濾波器幅頻響應(yīng)的同時(shí)獲得嚴(yán)格的線性相位特性,而數(shù)據(jù)通信、語(yǔ)音信號(hào)處理等領(lǐng)域往往要求信號(hào)在傳輸過(guò)程中不能有明顯的相位失真,所以FIR濾波器獲得了更廣泛的應(yīng)用。FIR濾波器有多種設(shè)計(jì)和實(shí)現(xiàn)方法,最為常用的是基于分布式算法的FIR濾波器設(shè)計(jì)。該法利用構(gòu)造查找表,流水線操作完成濾波過(guò)程,極大地提高了系統(tǒng)的處理效率。然而,查找表所要求的系統(tǒng)存儲(chǔ)器容量隨濾波器的階數(shù)成指數(shù)上漲。本文基于工程實(shí)際出發(fā),在信號(hào)處理速率要求不高且濾波器階數(shù)較高的情況下,提出了一種基于LPM參數(shù)化宏功能模塊的FIR濾波器設(shè)計(jì)方法,具有一定的工程實(shí)用價(jià)值。

1 FIR濾波器的原理與設(shè)計(jì)方法

1.1 FIR濾波器的原理

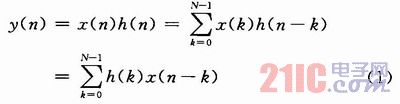

FIR濾波器的數(shù)學(xué)表達(dá)式為:

式中:N為FIR濾波器的抽頭數(shù);x(n)為第n時(shí)刻的輸入樣本;h(k)為FIR濾波器第k級(jí)抽頭系數(shù)。

直接型FIR濾波器結(jié)構(gòu)如圖1所示。

由圖1可見(jiàn),F(xiàn)IR的濾波過(guò)程就是一個(gè)信號(hào)逐級(jí)延遲的過(guò)程,將各級(jí)的延遲輸出加權(quán)累加,即得到FIR的輸出,其中最主要的算法是乘累加運(yùn)算。由于FIR每完成一次濾波過(guò)程就需要進(jìn)行N次乘法和N-1次加法操作,所以FIR濾波的運(yùn)算量完全依賴于N的大小。

1.2 分布式FIR濾波器設(shè)計(jì)

分布式算法(Distributed Arithmetic,DA)早在1973年就已經(jīng)被Croisier提出,直到現(xiàn)場(chǎng)可編程門陣列(Field Programmable Gate Ar-ray,F(xiàn)PGA)的查找表(Look Up Table,LUT)結(jié)構(gòu)出現(xiàn),這種算法才重新受到重視,其主要原理如下。

為了分析簡(jiǎn)單,將FIR濾波器的表達(dá)式(1)改寫為:

可見(jiàn),分布式算法是一種以實(shí)現(xiàn)“乘-加”單元為目的的優(yōu)化解決方案。利用一個(gè)查找表(LUT)實(shí)現(xiàn)映射,即用一個(gè)2k字寬(即2k行),預(yù)先編好程序中LUT接收到的一個(gè)K位輸入向量Xb=[X0b,X1b,…,X(k-1)b]的映射,經(jīng)查找表的查找后直接輸出部分積![]() 。然而,由上述可知,查找表字寬為2k,如果濾波器的抽頭系數(shù)過(guò)多,則查找表的規(guī)模隨抽頭系數(shù)的增加成指數(shù)級(jí)增長(zhǎng),這將使LUT的規(guī)模十分龐大。為了減小規(guī)模,可以利用部分表計(jì)算法,即將一個(gè)大的查找表化分為幾個(gè)小的查找表,然后再將結(jié)果相加。

。然而,由上述可知,查找表字寬為2k,如果濾波器的抽頭系數(shù)過(guò)多,則查找表的規(guī)模隨抽頭系數(shù)的增加成指數(shù)級(jí)增長(zhǎng),這將使LUT的規(guī)模十分龐大。為了減小規(guī)模,可以利用部分表計(jì)算法,即將一個(gè)大的查找表化分為幾個(gè)小的查找表,然后再將結(jié)果相加。

1.3 基于LPM參數(shù)化宏功能模塊的FIR濾波器設(shè)計(jì)

由1.2節(jié)可見(jiàn),分布式算法極大地減少了硬件電路規(guī)模,很容易實(shí)現(xiàn)流水線技術(shù),不僅使電路的執(zhí)行速度得以提高,使得信號(hào)的處理效率大幅度提高。然而,當(dāng)系統(tǒng)所要求的處理速度不高時(shí),可利用QuartusⅡ中的LPM參數(shù)化宏功能模塊來(lái)設(shè)計(jì)FIR濾波器;當(dāng)濾波器系數(shù)較大時(shí),該法不需要像分布式算法那樣構(gòu)造龐大的查找表或多個(gè)小的查找表。

1.3.1 LPM參數(shù)化功能模塊簡(jiǎn)述

LPM是參數(shù)可設(shè)置模塊庫(kù)(Library of Parameterized Modules)的英文縮寫,設(shè)計(jì)者可以根據(jù)實(shí)際電路的需要,選擇LPM庫(kù)中的適當(dāng)模塊,并為其設(shè)定適當(dāng)?shù)膮?shù),以滿足設(shè)計(jì)的要求。常用的LPM宏功能模塊有諸如累加器、加法器和乘法器等的算術(shù)組件;多路復(fù)用器和LPM門函數(shù)還有諸如和I/O組件、存儲(chǔ)器編譯器等等的門電路,用戶可以根據(jù)自身需要查閱相關(guān)的資料。本文正是利用其中的乘法器和累加器來(lái)完成FIR濾波器的設(shè)計(jì)。

1.3.2 FIR濾波器的設(shè)計(jì)

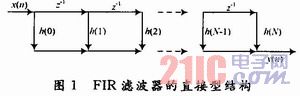

在QuartusⅡ中,利用“Megawizard”向?qū)伤璧哪K,其界面如圖2所示。

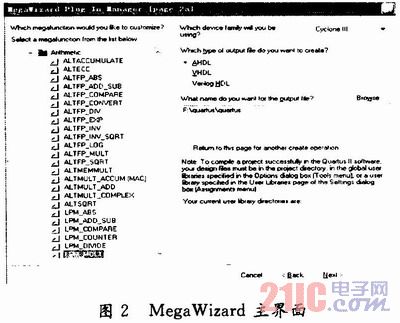

選擇圖中左側(cè)Arithmetic中的LPM_MULT得到圖3的界面,根據(jù)技術(shù)指標(biāo)選擇合適的參數(shù),即可生成乘法器模塊,按其向?qū)В瓿沙朔ㄆ鲄?shù)的設(shè)置(如乘數(shù)的位數(shù),是否有符號(hào)數(shù)相乘等)。加法器模塊的構(gòu)造類似,不再詳述。

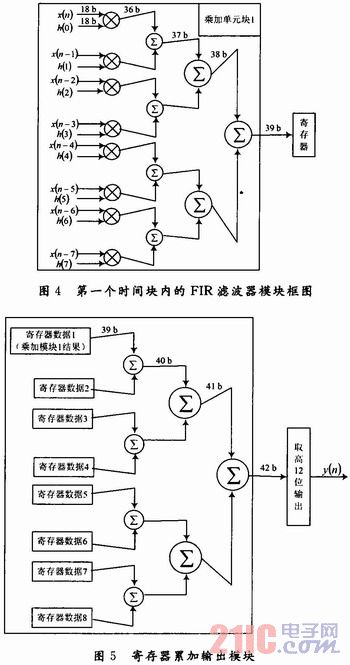

以本文設(shè)計(jì)的FIR濾波器為例(后面詳述),輸入信號(hào)的速率為2 MHz(周期為500 ns),濾波器的階數(shù)為64階,由此構(gòu)造了8個(gè)乘法器(最多可以構(gòu)造25個(gè)),分8次完成所有的乘法。相對(duì)分布式算法的流水速度而言,構(gòu)造的乘法器完成一次乘法需要20 ns,相對(duì)耗時(shí)長(zhǎng)一點(diǎn),但是完成8次乘法也只需8×20=160 ns,小于輸入信號(hào)一個(gè)周期的時(shí)間,因此滿足設(shè)計(jì)需求。將輸入數(shù)據(jù)的一個(gè)周期平均分為8個(gè)時(shí)間塊,每個(gè)時(shí)間內(nèi)的FIR濾波設(shè)計(jì)模塊的框圖如圖4所示。

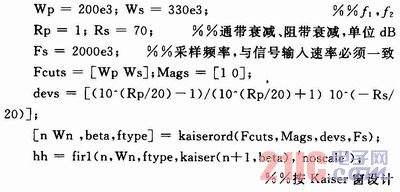

其他7個(gè)時(shí)間塊內(nèi)的FIR濾波器模塊同圖4,所不同的是參與乘法運(yùn)算的信號(hào)輸入數(shù)據(jù)和濾波器抽頭系數(shù)不同,分別從x(n-8)到x(n-63)和h(8)到h(63)。待8個(gè)乘加模塊的結(jié)果均送入寄存器后,再在最后一個(gè)時(shí)間塊內(nèi)完成累加得到最終的輸出(相對(duì)乘法運(yùn)算而言,完成累加的時(shí)間可以忽略),其實(shí)現(xiàn)框圖如圖5。

結(jié)合圖4和圖5,可全部完成基于LPM參數(shù)化宏功能模塊的FIR濾波器設(shè)計(jì)。由兩圖可以發(fā)現(xiàn),有多個(gè)全加器,且輸入數(shù)據(jù)的位數(shù)(bit數(shù))不同,只要調(diào)節(jié)LPM宏功能模塊的參數(shù)即可方便地完成設(shè)計(jì),輸出數(shù)據(jù)y(n)的位數(shù)則根據(jù)工程需要取最終累加結(jié)果的高12位。取高12位帶來(lái)的誤差為![]() (最高位為符號(hào)位,不予數(shù)值考慮),這是可以接受的誤差。

(最高位為符號(hào)位,不予數(shù)值考慮),這是可以接受的誤差。

2 基于Matlab和QuartusⅡ的FIR濾波器設(shè)計(jì)

2.1 利用Matlab進(jìn)行濾波器系數(shù)設(shè)計(jì)

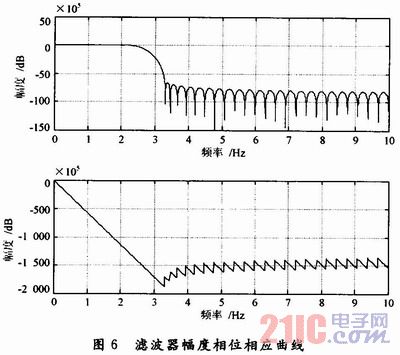

設(shè)計(jì)指標(biāo):采樣頻率為2 MHz,f1=200 kHz,f2=330 kHz,通帶衰減1 dB,阻帶衰減70 dB。通過(guò)參數(shù)指標(biāo)確定所需的階數(shù)和參數(shù)值,部分程序如下:

由圖6驗(yàn)證設(shè)計(jì)指標(biāo)。

如果設(shè)計(jì)指標(biāo)不滿足,則可通過(guò)調(diào)整濾波器參數(shù)直至滿足設(shè)計(jì)要求。

2.2 利用QuartusⅡ進(jìn)行設(shè)計(jì)和仿真

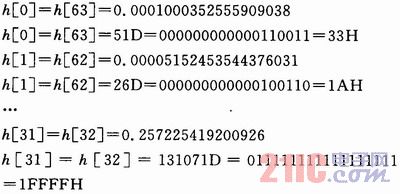

對(duì)Matlab產(chǎn)生的FIR濾波器抽頭系數(shù),用QuartusⅡ進(jìn)行仿真。QuartusⅡ軟件是Altera公司主推的FGPA設(shè)計(jì)軟件,是集設(shè)計(jì)輸入、編譯、綜合、仿真、布線、下載于一體的設(shè)計(jì)軟件。由于Matlab產(chǎn)生的濾波器抽頭系數(shù)為小數(shù),根據(jù)工程需要將其轉(zhuǎn)換為18位二進(jìn)制系數(shù)使用。過(guò)程如下:

由Matlab產(chǎn)生的FIR數(shù)字濾波器系數(shù)如下:

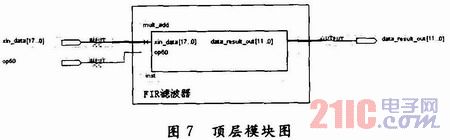

按第2.3節(jié)提出的方法在QuartusⅡ中完成FIR濾波器的設(shè)計(jì),通過(guò)編譯綜合功能對(duì)設(shè)計(jì)文件進(jìn)行編譯和綜合,然后生成頂層模塊,見(jiàn)圖7。

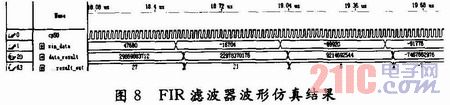

通過(guò)QuartusⅡ的波形仿真功能,對(duì)其進(jìn)行波形仿真并進(jìn)行定量分析。波形仿真如圖8所示。其中,cp50為系統(tǒng)時(shí)鐘,由它控制輸入信號(hào)xin_data的輸入速率(本例為2 MHz)。data_result為濾波器未經(jīng)取高位處理的乘加結(jié)果;data_result_out,為最終濾波輸出結(jié)果。經(jīng)驗(yàn)證,data_result與Matlab的運(yùn)算結(jié)果一致,data_result可滿足工程精度的要求。

3 結(jié)語(yǔ)

本文在結(jié)合Matlab和FPGA軟件QuartusⅡ的基礎(chǔ)上,完成了一種基于LPM參數(shù)化宏功能模塊的FIR濾波器設(shè)計(jì),該法是基于工程實(shí)際應(yīng)用提出的,它對(duì)信號(hào)處理速率的要求不高,但對(duì)濾波器的階數(shù)較高。當(dāng)設(shè)計(jì)指標(biāo)改變,只需調(diào)整各模塊的參數(shù),即可完成新的設(shè)計(jì),該法已應(yīng)用在實(shí)際工程中。