摘要:為提高整個(gè)系統(tǒng)時(shí)間的同步精度,以便為測(cè)量設(shè)備提供可靠的時(shí)間信息和標(biāo)準(zhǔn)頻率信號(hào),給出了一種基于FPGA" title="FPGA">FPGA的IRIG-B編解碼器" title="編解碼器">編解碼器的設(shè)計(jì)與實(shí)現(xiàn)方法。新系統(tǒng)基于模塊化設(shè)計(jì),其中編碼部分完成標(biāo)準(zhǔn)時(shí)間信息及相應(yīng)的BCD碼的產(chǎn)生,并在標(biāo)準(zhǔn)時(shí)間BCD碼中加入幀開始標(biāo)志位、位置識(shí)別標(biāo)志和索引標(biāo)志識(shí)別,從而將BCD格式的時(shí)間信息變成IRIG-B格式碼,同時(shí)數(shù)據(jù)并串處理可通過FPGA的一個(gè)I/O端口發(fā)送串行數(shù)據(jù)。解碼部分則完成串行IRIG-B格式碼的接收并判斷幀開始標(biāo)志位和位置識(shí)別標(biāo)志,再解出相應(yīng)原始時(shí)間信息并存儲(chǔ)到雙端口的RAM" title="RAM">RAM中,最后以并行方式輸出。

關(guān)鍵詞:IRIG-B;可編程邏輯器件;FPGA;編碼器;解碼器

0 引言

時(shí)間統(tǒng)一(以下簡(jiǎn)稱時(shí)統(tǒng))系統(tǒng)是武器系統(tǒng)試驗(yàn)測(cè)試、通信、氣象、航天、工業(yè)控制、電力系統(tǒng)測(cè)量與保護(hù)等領(lǐng)域的關(guān)鍵技術(shù),主要為其他參試測(cè)試設(shè)備提供標(biāo)準(zhǔn)時(shí)間信號(hào)和標(biāo)準(zhǔn)頻率信號(hào)。隨著現(xiàn)代信息技術(shù)的不斷發(fā)展,對(duì)標(biāo)準(zhǔn)化時(shí)間系統(tǒng)設(shè)備的要求越來(lái)越高,IRIG-B碼以其優(yōu)越性成為時(shí)間系統(tǒng)設(shè)備的首選。而對(duì)信號(hào)的幀結(jié)構(gòu)的可編程度、集成度的需求越來(lái)越高,用于時(shí)間系統(tǒng)的IRIG-B碼源的設(shè)計(jì)也趨于高度集成化。FPGA可編程邏輯器件的規(guī)模比較大,適合于時(shí)序、組合等邏輯電路應(yīng)用場(chǎng)合,同時(shí)具有實(shí)時(shí)性好、可靠性高、成本低、可編程等優(yōu)勢(shì)。本文介紹了采用Ahera公司的EP20K200E器件所設(shè)計(jì)的IRIG-B時(shí)統(tǒng)信號(hào)發(fā)生及解碼電路。

IRIG-B編碼模塊主要利用外部時(shí)鐘脈沖信號(hào)來(lái)觸發(fā),它將用于產(chǎn)生IRIG-B碼的各種門電路集成在一個(gè)芯片,以產(chǎn)生標(biāo)準(zhǔn)的IRIG-B串行時(shí)間碼并向設(shè)備終端發(fā)送,從而完成DC碼編碼。通過設(shè)備終端對(duì)接收到的IRIG-B碼進(jìn)行解調(diào),便能產(chǎn)生出系統(tǒng)所需的標(biāo)準(zhǔn)時(shí)間和各種控制信號(hào),然后再存儲(chǔ)到相應(yīng)的雙端口RAM中。

1 系統(tǒng)整體硬件設(shè)計(jì)

IRIG(Inter-Range Instrumentation Group)是美國(guó)靶場(chǎng)司令部委員會(huì)的下屬機(jī)構(gòu),稱為“靶場(chǎng)時(shí)間組”。IRIG-B碼(DC)以其實(shí)際的優(yōu)越性能而成為時(shí)統(tǒng)設(shè)備最佳選擇的標(biāo)準(zhǔn)碼型。IRIG時(shí)間標(biāo)準(zhǔn)有兩大類:一類是并行時(shí)間碼格式,這類碼由于是并行格式,傳輸距離較近,且是二進(jìn)制,因此遠(yuǎn)不如串行格式廣泛;另一類是串行時(shí)間碼,共有六種格式,即A、B、D、E、G、H。它們的主要差別是時(shí)間碼的幀速率不同,B碼的主要特點(diǎn)是時(shí)幀速率為1幀/s;而且攜帶信息量大,經(jīng)譯碼后可獲得1、10、100、1000 c/s的脈沖信號(hào)和BCD編碼的時(shí)間信息及控制功能信息;此外,B碼的分辨率高,調(diào)制后的B碼帶寬能適用于遠(yuǎn)距離傳輸,它分為直流、交流兩種,而且接口標(biāo)準(zhǔn)化,國(guó)際通用。

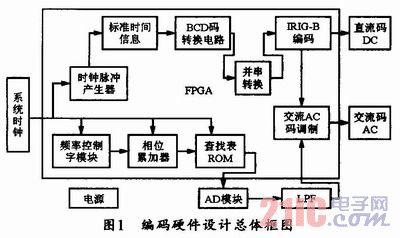

IRIG-B碼編碼器由時(shí)鐘脈沖發(fā)生器模塊、標(biāo)準(zhǔn)時(shí)間形成模塊、BCD碼轉(zhuǎn)換模塊、并串轉(zhuǎn)換、直流碼形成模塊和交流碼模塊組成,其編碼器硬件設(shè)計(jì)總體框圖如圖1所示。

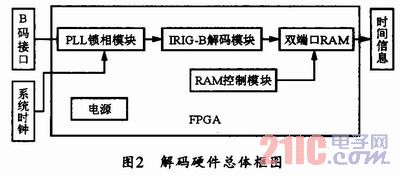

IRIG-B解碼器則由鎖相環(huán)PLL模塊、IRIG-B解碼模塊、雙端口RAM、RAM控制模塊等組成。其解碼硬件的設(shè)計(jì)框圖如圖2所示。

2 IRIG-B編碼模塊的設(shè)計(jì)

2.1 時(shí)鐘脈沖產(chǎn)生模塊設(shè)計(jì)

為了達(dá)到系統(tǒng)所要求的精度,使頻率較為穩(wěn)定,設(shè)計(jì)時(shí)可用更高的頻率作為時(shí)鐘分頻鏈的第一主時(shí)鐘。這里采用鎖相環(huán)實(shí)現(xiàn)倍頻方法來(lái)提供所需的頻率,可選用Quartus II軟件中宏功能庫(kù)中自帶的PLL來(lái)提高整體的運(yùn)算速度,同時(shí)也能合理的進(jìn)行資源綜合。實(shí)事上,使用基本的宏定義模塊可以明顯地提高用戶的設(shè)計(jì)開發(fā)時(shí)間。時(shí)鐘脈沖產(chǎn)生電路是IRIG-B碼產(chǎn)生器不可缺少的單元,該電路主要由幾個(gè)分頻器級(jí)聯(lián)和一些邏輯門組成。

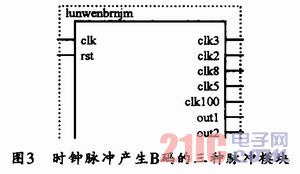

電路中的數(shù)字分頻器可對(duì)外部提供的頻率進(jìn)行分頻,以產(chǎn)生系統(tǒng)所需時(shí)序脈沖和B碼的三種基本編碼形式脈沖,其寬度(高電平)分別為2ms、5 ms、8 ms,頻率為100Hz的脈沖信號(hào):其中第一種是高電平為2 ms、低電平為8 ms的脈沖(代表邏輯“0”);第二種是高、低電平均為5 ms的脈沖(代表邏輯“1”);第三種是高電平為8ms、低電平為2 ms的脈沖(作為位置識(shí)別標(biāo)志和參考碼元)。Quartus II軟件下的仿真模塊結(jié)果如圖3所示。

2.2 標(biāo)準(zhǔn)時(shí)間信息和BCD碼轉(zhuǎn)換模塊設(shè)計(jì)

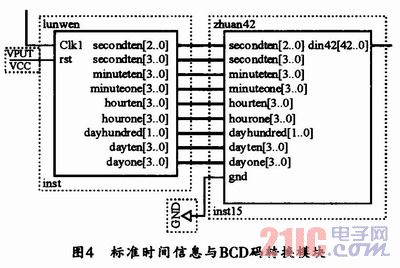

該模塊由百分秒計(jì)數(shù)器、秒計(jì)數(shù)器、分計(jì)數(shù)器、時(shí)計(jì)數(shù)器和天計(jì)數(shù)器級(jí)連而成。它可對(duì)預(yù)置的時(shí)間進(jìn)行秒加一,每隔一秒對(duì)時(shí)間信息刷新一次,從而形成動(dòng)態(tài)BCD碼,并使時(shí)間信息符合IRIG-B碼的格式。標(biāo)準(zhǔn)時(shí)間信息和BCD碼轉(zhuǎn)換模塊如圖4所示。

2.3 IRIG-B碼DC格式的生成

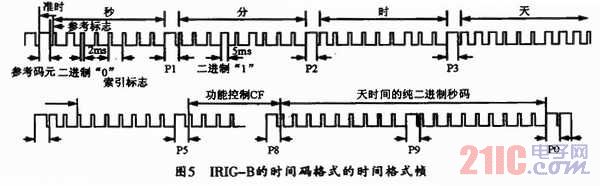

IRIG-B(DC)時(shí)間碼格式的時(shí)間格式幀從幀參考標(biāo)志開始,因此,連續(xù)兩個(gè)8ms寬脈沖中的第二個(gè)8ms脈沖的前沿為秒的準(zhǔn)時(shí)點(diǎn),該點(diǎn)標(biāo)志著一個(gè)時(shí)間格式幀的開始,稱為參考碼元。從第二個(gè)8ms開始,分別為第1、2、…、99、0個(gè)碼元。B碼時(shí)間格式中含有秒、分、時(shí)、天等信息,其位置在P0~P5間。時(shí)間信息中,高電平用5ms脈沖表示,低電平用2 ms脈沖表示,其中秒信息占用第2、3、4、5、7、8、9碼元;分信息占用第11、12、13、14、16、17碼元;時(shí)信息占用第20、21、22、24、26、27碼元;天信息占用第31、32、33、34、36、37、38、38、41、42碼元;P6~P10包含其他控制信息(這里沒有應(yīng)用)。另外,第6、15、25、35、…、95碼元為索引標(biāo)志,用2ms脈沖寬度表示,固定為“0”。時(shí)、分、秒均用相應(yīng)BCD碼表示,低位在前,高位在后,個(gè)位在前,十位、百位在后。圖5所示是IRIG-B時(shí)間碼的格式幀示意圖。

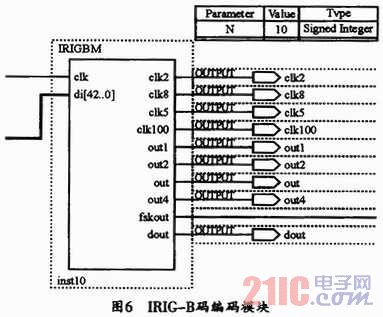

一般每個(gè)IRIG-B碼都包含有豐富的碼信息。它必須包含幀開始標(biāo)志位、位置識(shí)別標(biāo)志和索引標(biāo)志,以使接受方能進(jìn)行數(shù)據(jù)卸載,或通過位置識(shí)別標(biāo)志和索引標(biāo)志識(shí)別出相應(yīng)的天、時(shí)、分、秒等信息。圖6所示是IRIG-B碼編碼模塊的設(shè)計(jì)圖。

3 IRRIG-B解碼模塊設(shè)計(jì)

3.1 鎖相環(huán)PLL模塊

PLL鎖相環(huán)模塊用于實(shí)現(xiàn)系統(tǒng)同步功能,以使外部信號(hào)脈沖和提供的標(biāo)準(zhǔn)時(shí)鐘脈沖相位同步,從而實(shí)現(xiàn)輸入信號(hào)頻率對(duì)標(biāo)準(zhǔn)信號(hào)頻率的自動(dòng)跟蹤。PLL主要由鑒相器(PD)、環(huán)路濾波器(LPF)和壓控振蕩器(VCO)等三個(gè)基本部件組成。本文選用Ouartus II軟件中宏功能庫(kù)中自帶的PIX模塊來(lái)實(shí)現(xiàn)其相位同步功能。

3.2 IRIG-B解碼模塊

對(duì)IRIG-B碼進(jìn)行解碼就是將B中包含的標(biāo)準(zhǔn)時(shí)間信號(hào)和天、時(shí)、分、秒信息提取出來(lái)。解碼的關(guān)鍵在于判別IRIG-B碼的幀開始標(biāo)志位和相應(yīng)的秒、時(shí)、分、天的位置和信息。通過檢測(cè)B碼中各個(gè)碼元的寬度(高電平),可以判斷相應(yīng)的時(shí)間信息。該模塊可完成對(duì)IRIG-B碼的寬度檢測(cè)。如果寬度為8,則確定是位置識(shí)別標(biāo)志,如果檢測(cè)到兩個(gè)連續(xù)的寬度都是8,第二個(gè)寬度為8的脈沖則作為幀開始標(biāo)志位。如果寬度為5,則對(duì)應(yīng)的數(shù)值為“1”,如果寬度為2,則對(duì)應(yīng)的數(shù)值為“0”。

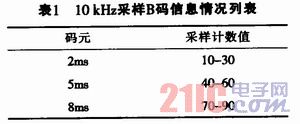

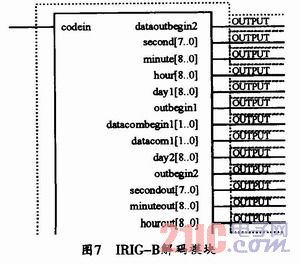

本設(shè)計(jì)采用10 kHz基準(zhǔn)信號(hào)來(lái)采樣IRIG-B碼信號(hào)以提取碼元相關(guān)信息。由于10kHz與外部頻率脈沖不能完全同步,有一定時(shí)間誤差。所以,利用10 kHz脈沖信號(hào)來(lái)采樣B碼信號(hào),可使三種碼元不會(huì)出現(xiàn)重疊,從而可以提高采樣精度。在捕獲方式下,當(dāng)滿足捕獲條件時(shí),硬件可自動(dòng)將計(jì)數(shù)器中的數(shù)據(jù)寫入存儲(chǔ)器中,當(dāng)B碼信號(hào)的上升沿到來(lái)時(shí),計(jì)數(shù)器開始計(jì)數(shù),下降沿到來(lái)時(shí)則停止計(jì)數(shù),并通過采樣計(jì)數(shù)數(shù)值范圍來(lái)判斷對(duì)應(yīng)的碼元,從而將直流碼解出。表1所列是用10kHz采樣B碼的信息表,圖7所示是IRIG-B解碼模塊示意圖。

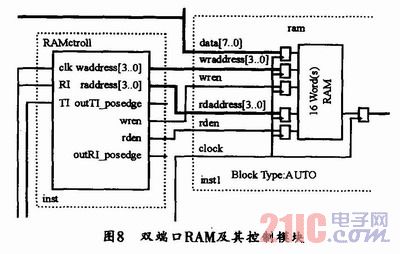

3.3 雙端口RAM和控制模塊

本系統(tǒng)中的RAM模塊主要完成時(shí)間信息的存儲(chǔ),RAM通過讀寫控制信號(hào)來(lái)進(jìn)行讀寫控制。當(dāng)讀寫信號(hào)為高電平時(shí)進(jìn)行寫操作,此時(shí)可以通過寫地址線控制把數(shù)據(jù)存儲(chǔ)到相應(yīng)的存儲(chǔ)單元中;為低電平時(shí)則進(jìn)行讀操作,此時(shí)可通過讀地址線控制把相應(yīng)存儲(chǔ)單元的數(shù)據(jù)讀出。從而完成整個(gè)數(shù)據(jù)存儲(chǔ)的讀取,圖8所示是該雙端口RAM和控制模塊的示意圖。

4 結(jié)束語(yǔ)

基于FPGA的IRIG-B碼編解碼器有利于硬件電路的簡(jiǎn)化并縮短開發(fā)周期,同時(shí)其工作穩(wěn)定,可靠性高,可提供精確時(shí)間信息,在工程實(shí)踐中得到日益廣泛的應(yīng)用。本系統(tǒng)采用模塊化設(shè)計(jì),其系統(tǒng)的各個(gè)模塊之間有較好的關(guān)聯(lián)性,又有一定的獨(dú)立性,便于后期對(duì)系統(tǒng)功能的擴(kuò)展。當(dāng)以串行方式進(jìn)行數(shù)據(jù)傳輸,用一個(gè)I/O端口即可完成數(shù)據(jù)的接收和發(fā)送,因而既節(jié)省系統(tǒng)資源,又可解決并行傳輸通道之間的相互干擾問題。