3D-IC設(shè)計(jì)者希望制作出高深寬比(HAR>10:1)硅通孔" title="通孔">通孔(TSV),從而設(shè)計(jì)出更小尺寸" title="小尺寸">小尺寸的通孔,以減小TSV通孔群在硅片上的占用空間,最終改進(jìn)信號(hào)的完整性。事實(shí)上,當(dāng)前傳統(tǒng)的TSV生產(chǎn)供應(yīng)鏈已落后于ITRS對(duì)其的預(yù)測(cè)。以干法和濕法工藝為基礎(chǔ)的傳統(tǒng)解決方案把那些專門(mén)設(shè)計(jì)應(yīng)用于MEMS或雙嵌入式的昂貴的工具轉(zhuǎn)而應(yīng)用到工藝窗邊緣或工藝窗外部的工藝處理中。這樣做的結(jié)果要么影響產(chǎn)品的性能,要么使工藝占有成本高得無(wú)法接受。當(dāng)AR>5:1時(shí),PVD薄膜會(huì)變得不連續(xù);由于使用納米噴涂工具,電離PVD或ALD的成本變得極其昂貴。

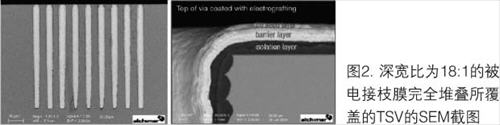

當(dāng)前,采用一種納米技術(shù)解決方案可實(shí)現(xiàn)HAR>20:1的結(jié)構(gòu),而成本只占傳統(tǒng)工藝的一部分。這種工藝被稱為電接枝技術(shù)(Electrografting),通常要沿著TSV的內(nèi)壁形成表面活性共形膜。這種膜比較薄,具有連續(xù)性和粘著性,且十分均勻。這項(xiàng)濕法工藝使用標(biāo)準(zhǔn)電鍍工具,具有極高的成本效益。

TSV對(duì)3D-IC設(shè)計(jì)的影響

雖然把TSV融入主流半導(dǎo)體工藝還需要解決一些技術(shù)難題,但研究TSV對(duì)3D-IC設(shè)計(jì)流程的影響卻十分必要。總的來(lái)說(shuō),TSV技術(shù)革新受到性能和功能進(jìn)步等設(shè)計(jì)要求的帶動(dòng),相反,多芯片模塊(MCM)解決方案受到技術(shù)進(jìn)步的推動(dòng),卻一直不被主流技術(shù)所接納。因此,通過(guò)簡(jiǎn)要討論3D-IC的設(shè)計(jì)問(wèn)題可以對(duì)SAR TSV技術(shù)的主要推動(dòng)力進(jìn)行深層次分析。

我們的研究實(shí)例是一個(gè)移動(dòng)通信應(yīng)用的新型CPU子系統(tǒng),在堆疊封裝(PoP)結(jié)構(gòu)中包含一個(gè)ARM11基微處理器、一個(gè)2Gb NAND存儲(chǔ)芯片和一個(gè)1Mb DRAM芯片,帶有500個(gè)I/O" title="I/O">I/O引腳,其中一半用于電源和接地的布線。此外,需要大約80個(gè)內(nèi)部連接把三個(gè)IC連接到PoP中;這樣,信號(hào)I/O的總數(shù)為330。采用低功率65nm技術(shù)制作的用于最新智能電話的三星S3C6410就是這種CPU子系統(tǒng)的典型實(shí)例。

為了對(duì)這一實(shí)例進(jìn)行分析,我們?cè)O(shè)計(jì)了一個(gè)這種子系統(tǒng)的3D-IC堆疊,并使用TSV技術(shù)把3個(gè)芯片連接起來(lái),其中小型低功率微處理器位于堆疊頂部,兩個(gè)存儲(chǔ)IC位于下部。雖然從功耗的角度來(lái)看這種安排并不一定十分理想,但考慮到對(duì)微處理器的低功耗和小尺寸要求,這種選擇就顯得比較合理了。當(dāng)然也可以使用其它結(jié)構(gòu),不會(huì)影響從這一范例獲得的結(jié)論。

讓我們?cè)敿?xì)介紹一下微處理器的相關(guān)技術(shù)參數(shù),并做出以下假設(shè):IC尺寸為8×8mm,#信號(hào)TSV為330,#電源和接地TSV為660 (經(jīng)驗(yàn)數(shù)據(jù):是#信號(hào) I/O的2倍),晶圓" title="晶圓">晶圓成本/mm2為0.10$。

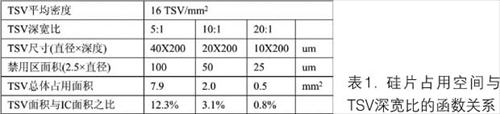

假設(shè)共有1000個(gè)TSV,通孔密度可達(dá)16TSV/mm2。這樣就可以計(jì)算出1000個(gè)TSV在IC上的空間占用情況。對(duì)深寬比分別為5:1、10:1和20:1的三種TSV進(jìn)行了比較,前提條件是使它們保持相同的通孔深度和相同的禁用區(qū)標(biāo)準(zhǔn)。表1概況了所有相關(guān)數(shù)據(jù)并說(shuō)明了硅片的實(shí)際占用情況。

表1清楚地表明了高深寬比TSV對(duì)縮小硅片面積的重要影響。節(jié)省的硅片面積隨TSV深寬比的增大呈指數(shù)增長(zhǎng),隨TSV密度的增大呈線性增長(zhǎng)。換而言之,電接枝技術(shù)使TSV深寬比增大了3倍,使單位面積TSV的數(shù)量增加了8倍。在當(dāng)前的范例中,采用深寬比為20:1的TSV取代5:1的TSV將使每個(gè)晶圓的成本收益達(dá)到731$。

信號(hào)完整性

不斷縮小TSV的直徑可能使信號(hào)完整性下降,這是它的不利之處。通孔排列得越緊密,串?dāng)_和其它寄生效應(yīng)就會(huì)變得越明顯。這個(gè)問(wèn)題應(yīng)當(dāng)屬于設(shè)計(jì)技巧的范疇,而TSV工藝限制卻不屬于設(shè)計(jì)問(wèn)題,而應(yīng)當(dāng)屬于設(shè)計(jì)最佳實(shí)踐。舉例來(lái)說(shuō),由于對(duì)TSV數(shù)量的要求不斷增多,設(shè)計(jì)者便把許多TSV用作信號(hào)通孔周圍的接地屏蔽。通過(guò)合理排列TSV,使每個(gè)TSV傳送不同的信號(hào), 9個(gè)小尺寸TSV的傳輸特性優(yōu)于 1個(gè)大尺寸TSV(圖1)。

在電接枝工藝過(guò)程中,來(lái)源于偏置表面的電子可充當(dāng)先驅(qū)物分子的“鍵合籽晶”,在第一層籽晶先驅(qū)物和表面之間形成共價(jià)化學(xué)鍵。這是一種不使用噴涂或旋涂工藝就能把聚合物絕緣層直接“接枝”到硅表面的有效方法。形成的第一個(gè)接植層可用作絕緣層(襯墊層),也可用作采用化學(xué)接枝技術(shù)進(jìn)行勢(shì)壘" title="勢(shì)壘">勢(shì)壘層淀積" title="淀積">淀積時(shí)的粘接促進(jìn)劑。化學(xué)接枝技術(shù)與電接枝技術(shù)的原理相同,但用于非導(dǎo)體表面。選擇專用化學(xué)材料把勢(shì)壘催化劑與聚合物堅(jiān)固地鍵合在一起。這樣,通過(guò)化學(xué)接枝技術(shù)改進(jìn)了勢(shì)壘和聚合物之間的粘著性。然后再把濕銅籽晶電接枝到導(dǎo)電勢(shì)壘上,即使在高深寬比TSV條件下也能形成高臺(tái)階覆蓋率。電化學(xué)電解槽非常穩(wěn)定;膜生長(zhǎng)速率及厚度分別受電流密度和電荷的控制。圖2示出TSV深寬比為18:1,被電接枝膜完全堆疊所覆蓋的TSV的SEM截圖,還清晰展示了帶有隔離、阻擋和Cu籽晶的高扇形通孔的頂部近觀圖。

占有成本(COO)

商用、批量生產(chǎn)電鍍工具與電接枝技術(shù)所用的工具完全兼容,因此,與干法工藝相比,電接枝技術(shù)有很強(qiáng)的成本優(yōu)勢(shì)。圖3對(duì)深寬比為6:1和10:1的TSV晶圓的批量生產(chǎn)成本優(yōu)勢(shì)進(jìn)行了量化分析。對(duì)每個(gè)晶圓的膜淀積工藝(隔離、阻擋、籽晶)和完整的TSV制造流程(DRIE+隔離、阻擋、籽晶+CMP)的COO進(jìn)行了比較。電接枝技術(shù)的成本效益遠(yuǎn)遠(yuǎn)超過(guò)了薄膜淀積工藝:在進(jìn)行高速(=廉價(jià)的)DRIE工藝時(shí),電接枝膜沒(méi)有受到嚴(yán)重扇形邊緣的影響而產(chǎn)生退化;由于這種膜具有高臺(tái)階覆蓋率特性,晶圓表面只有少量的冗余材料需要通過(guò)CMP去除。這使TSV制造流程的總體成本下降了42%(表3)。

結(jié)論

每次對(duì)樣品范例進(jìn)行批次更新時(shí),都要對(duì)基礎(chǔ)設(shè)施進(jìn)行重新改造,從而補(bǔ)充一些先進(jìn)的技術(shù)要素。TSV也不例外,需要擺脫傳統(tǒng)的真空基晶圓級(jí)工藝對(duì)成本和工藝的限制。電接枝技術(shù)運(yùn)用了最尖端的設(shè)計(jì)原則,是一種適合批量生產(chǎn)的、可靠的TSV納米制作技術(shù)。這種技術(shù)可在兩方面使投資迅速得到回報(bào):在工藝方面,與傳統(tǒng)技術(shù)相比成本減半;在設(shè)計(jì)方面,通過(guò)使用HAR TSV使硅片的面積下降了10倍。隨著當(dāng)前半導(dǎo)體工業(yè)正從歷史最低迷時(shí)期得以恢復(fù),正是考慮資本部署的最佳時(shí)機(jī)。對(duì)于集成器件制造商(IDM)來(lái)說(shuō),要想實(shí)現(xiàn)專用產(chǎn)品的加工能力,只需要在濕法或干法ROI工藝之間做出抉擇。而對(duì)于外包性半導(dǎo)體組裝和測(cè)試供應(yīng)商(OSAT)來(lái)說(shuō),就會(huì)遇到更加嚴(yán)峻的問(wèn)題:是使用現(xiàn)有的制作凸點(diǎn)和WLP的基礎(chǔ)設(shè)施,還是接納前端工藝昂貴的工具購(gòu)置費(fèi)?一些原本具有系統(tǒng)級(jí)收益的前景光明的新型SiP產(chǎn)品,如集成無(wú)源器件(IPD)和Si中間層,可能面臨更大的風(fēng)險(xiǎn)。