摘要:現(xiàn)在市場(chǎng)上的各種電阻和電阻箱有不足之處,不能滿足一些研發(fā)場(chǎng)所的要求,為了解決這一問題,本文介紹一種基于FPGA的可直接輸入阻值提供不同電阻的設(shè)計(jì)方法。FPGA通過控制繼電器的吸合,從而確定與其并聯(lián)的電阻的接入與否,最后通過電阻的疊加得到不同阻值。介紹了該設(shè)計(jì)的工作原理及軟件設(shè)計(jì)思想,并有部分仿真結(jié)果。這種設(shè)計(jì)使用8421編碼原則和硬件描述語言,減少了一些元器件的使用。相比于市場(chǎng)上的產(chǎn)品,其穩(wěn)定性更高,抗干擾性更強(qiáng),體積也更小,同時(shí),它的操作更簡(jiǎn)便,顯示更直觀。

關(guān)鍵詞:現(xiàn)場(chǎng)可編程門陣列;可編程;任意電阻

電阻幾乎是所有電路中必不可少的部分,常見的也有很多不同阻值的電阻,然而在一些電路中同一位置不同時(shí)刻還需要不同阻值,在一些精度要求不高的場(chǎng)合,可用滑動(dòng)變阻器來實(shí)現(xiàn),但是我們不能確定其具體阻值。隨著技術(shù)的進(jìn)一步發(fā)展,為了滿足教學(xué)研某些場(chǎng)合的需要,阻值確定并可調(diào)的電阻箱應(yīng)運(yùn)而生。電阻箱提供阻值的原理是通過電阻的串并聯(lián)得到的不同阻值,因而用到的電阻數(shù)量較多,精度也不夠高,而且還需要對(duì)所需電阻的每一位數(shù)選擇相應(yīng)的檔位,比較麻煩,也不夠直觀。而在一些生產(chǎn)應(yīng)用中(如產(chǎn)品校驗(yàn))需同時(shí)提供幾組不同電阻,且要重復(fù)提供(如做產(chǎn)品老化檢測(cè)實(shí)驗(yàn)),這就需要將該阻值記錄下來,而以前的電阻箱都不具備記憶功能,不能滿足要求。

本文介紹了用FPGA來實(shí)現(xiàn)控制電阻的提供,用軟件的方式來設(shè)計(jì)硬件,設(shè)計(jì)過程中可用有關(guān)軟件進(jìn)行各種仿真,同時(shí)整個(gè)系統(tǒng)可集成在一個(gè)芯片上,體積小、功耗低,可靠性高,又因?yàn)槠鋬?nèi)部有存儲(chǔ)單元,所以能夠滿足上述的“記憶”功能。

1 硬件電路

基于FPGA的可編程電阻系統(tǒng)的硬件系統(tǒng)(如圖1所示)主要由以下幾個(gè)功能模塊組成:

1.1 主控制器FPGA

FPGA(本設(shè)計(jì)中選用的是CyeloneII系列)控制中心是整個(gè)設(shè)計(jì)的核心,主要控制實(shí)現(xiàn)對(duì)系統(tǒng)的鍵盤輸入進(jìn)行處理,并根據(jù)輸入的信息轉(zhuǎn)換成輸出數(shù)據(jù),控制對(duì)應(yīng)的繼電器的吸合,從而得到不同的阻值。

以往可編程網(wǎng)絡(luò)的主控制器有采用數(shù)字電路控制的,也有采用單片機(jī)控制的,本電路采用FPGA控制。EPGA是近幾年來出現(xiàn)并被廣泛應(yīng)用的大規(guī)模集成電路器件,它的特點(diǎn)是直接面向用戶,具有極大的靈活性和通用性,使用方便,硬件測(cè)試和實(shí)現(xiàn)快捷,開發(fā)效率高,成本低,上市時(shí)間短,技術(shù)維護(hù)簡(jiǎn)單,工作可靠性好等。因而用來設(shè)計(jì)可編程電阻其靈活性更好。

目前市場(chǎng)上主要生產(chǎn)FPGA產(chǎn)品的公司有Lattice、Xilinx、Altera。在教學(xué)過程中,一般使用Altera公司生產(chǎn)的FLEX系列和 Cyclone系列較多。鑒于產(chǎn)品的成本和通用性考慮,本實(shí)驗(yàn)中采用CycloneII,它是第二代低成本FPGA系列,它所擁有的獨(dú)特性能有:NiosII嵌入式處理

器支持,嵌入式18*18數(shù)字信號(hào)處理乘法器,中等容量的片內(nèi)存儲(chǔ)器(能夠滿足本設(shè)計(jì)的要求)中等速度的I/O引腳和存儲(chǔ)器接口。在性價(jià)比上更適合本設(shè)計(jì),所以在本設(shè)計(jì)中選用此系列。

1.2 鍵盤輸入電路

鍵盤輸入電路主要實(shí)現(xiàn)輸出電阻值大小的設(shè)定,本設(shè)計(jì)中采用的4*4簡(jiǎn)易鍵盤輸入即可滿足要求,可提供簡(jiǎn)單明了的數(shù)字鍵和功能鍵共16個(gè)鍵,包括:數(shù)字輸入鍵:數(shù)字鍵0~9,按下數(shù)字鍵,輸入一個(gè)數(shù)字,就可在對(duì)應(yīng)的數(shù)碼管上顯示。

功能鍵:“電阻1”、“電阻2”本設(shè)計(jì)可以同時(shí)提供兩組電阻,可以選擇電阻1,也可以選擇電阻2,提供一組電阻,也可以電阻1、電阻2同時(shí)選擇提供兩組電阻。

“存儲(chǔ)”:每輸入完一個(gè)數(shù)字后按一下存儲(chǔ)鍵,以便能夠?qū)讉€(gè)數(shù)據(jù)存儲(chǔ)下來,運(yùn)行后將按數(shù)據(jù)存儲(chǔ)的先后順序及預(yù)置的時(shí)間工作,循環(huán)提供數(shù)據(jù)。

“運(yùn)行”:此鍵作為存儲(chǔ)完數(shù)據(jù)后的啟動(dòng)鍵。

“停止”:停止提供電阻。

“復(fù)位”:可作為修改數(shù)據(jù)時(shí)用,按此鍵后可以使以前存儲(chǔ)的數(shù)據(jù)都清零,然后重置一組數(shù)據(jù)。

1.3 繼電器電阻網(wǎng)絡(luò)

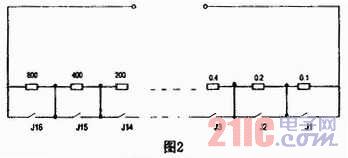

電阻網(wǎng)絡(luò)。其原理圖如圖2所示,從圖中可以看出,開關(guān)的閉合決定與其對(duì)應(yīng)的電阻的接入與否,本設(shè)計(jì)中采用8421編碼原理控制提各阻值。

本設(shè)計(jì)所供用的電阻要精確到0.1 Ω,所以,此電阻網(wǎng)絡(luò)所使用的電阻都是精密電阻。這里我們以提供電阻阻值在1500Ω以內(nèi)的電阻為例來說明。此電阻網(wǎng)絡(luò)采用串聯(lián)的方式來實(shí)現(xiàn),8421編碼方式只要控制相應(yīng)的繼電器,將其對(duì)應(yīng)的精密電阻短接就可以實(shí)現(xiàn)。以1500 Ω以內(nèi)電阻為例,只需16個(gè)電阻就可以滿足要求。通過控制繼電器J1至J16的斷開或閉合,其對(duì)應(yīng)的電阻就會(huì)接入或斷開,最后接入的電阻串聯(lián)相加就得輸出的電阻值。

如通過鍵盤輸入一個(gè)預(yù)置值,如果輸入的數(shù)值為545.7Ω, 輸出的阻值大小就可以表示R=400+100+40+4+1+0.4+0.2+0.1。即只需將這些電阻需要接入,相應(yīng)的繼電器J1、J2、J3、J5、 J7、J11、J13、J15要斷開,其余的繼電器則閉合,對(duì)應(yīng)的二進(jìn)制代碼則為(0101 0100 0101 0111)B,通過此列可以看出用16個(gè)電阻就可以實(shí)現(xiàn)1500Ω以內(nèi)的精度可達(dá)到O.1 Ω的任何電阻,使用電阻數(shù)量小,通過程序來控制電阻的接入,體積更小,同時(shí),維護(hù)起來也更加方便,如果需要大于1500Ω的電阻,同樣可以根據(jù)此原理來增加電阻(如8000、4000、2000、1000等),因?yàn)榇嗽O(shè)計(jì)中同時(shí)提供兩個(gè)電阻,因而還要16個(gè)同樣的電阻,原理同上(根據(jù)不同場(chǎng)合如要提供三組或三組以上的電阻只需相應(yīng)增加即可)。

1.4 輸出顯示電路

輸出顯示電路主要功能是實(shí)時(shí)顯示對(duì)應(yīng)的鍵盤輸入電阻值的大小、當(dāng)前工作的步數(shù)和預(yù)置時(shí)間。根據(jù)要求,本實(shí)驗(yàn)采用數(shù)碼管來顯示其阻值即可,能夠滿足要求,為了顯示以上數(shù)據(jù),每個(gè)阻值的顯示至少需要九個(gè)數(shù)碼管,其中五位用來顯示當(dāng)前阻值的大小,兩位用來顯示當(dāng)前的工作步數(shù),兩位用來顯示數(shù)據(jù)的工作時(shí)間,如果采用靜態(tài)顯示控制將會(huì)需要相當(dāng)多的引腳端資源(9×2×8=144個(gè)),為了減少對(duì)FPGA引腳資源的使用,本設(shè)計(jì)中采用掃描的方式來實(shí)現(xiàn)LED的動(dòng)態(tài)顯示。

2 軟件設(shè)計(jì)及部分仿真結(jié)果

本設(shè)計(jì)中,主要控制程序都是通過FPGA的軟件編程來實(shí)現(xiàn)。軟件設(shè)計(jì)大體可以分為三個(gè)大模塊:鍵盤掃描模塊、LED顯示模塊、繼電器電阻驅(qū)動(dòng)電路模塊。

2.1 鍵盤掃描模塊

鍵盤掃描模塊主要用來檢測(cè)外界輸入的數(shù)據(jù),主要由分頻器電路、鍵盤掃描計(jì)數(shù)器電路、鍵盤行和列按鍵檢測(cè)電路、按鍵抖動(dòng)消除電路和鍵盤編碼電路組成。

因?yàn)楸驹O(shè)計(jì)中外接頻率為一般用6MHz的信號(hào)作為時(shí)鐘信號(hào),但是鍵盤掃描不需要那么高的頻率,所以需要一個(gè)分頻電路將其頻率降低為1kHz。鍵盤掃描計(jì)數(shù)器主要為鍵盤行和列按鍵檢測(cè)電路和鍵盤編碼電路服務(wù),鍵盤行和列按鍵檢測(cè)電路用來檢測(cè)鍵盤輸入所在行列的位置,按鍵抖動(dòng)消除電路主要目的是為了避免按鍵時(shí)鍵盤產(chǎn)生的拉動(dòng)效應(yīng)使按鍵使能位產(chǎn)生不必要的抖動(dòng)變化而造成重復(fù)統(tǒng)計(jì)按鍵次數(shù)的結(jié)果。同時(shí),鍵盤位置的代號(hào),并不是鍵盤上的按鍵值,所以要用鍵盤編碼電路來傳遞真正的按鍵值。

2.2 LED顯示模塊

LED顯示模塊采用動(dòng)態(tài)顯示方式,這種實(shí)現(xiàn)方法是依次點(diǎn)亮各個(gè)LED數(shù)碼管,循環(huán)進(jìn)行顯示,這種顯示方式控制好數(shù)碼管之間的延時(shí)相當(dāng)重要,根據(jù)人眼視覺暫留原理,LED數(shù)碼管每秒的導(dǎo)通16次以上,人眼就無法分辯LED數(shù)碼管短暫的不亮,認(rèn)為是一直點(diǎn)亮的,但延時(shí)也不是越小越好,因?yàn)長(zhǎng)ED數(shù)碼管達(dá)到一定亮需要一定時(shí)間。為了達(dá)到較好的效果,本設(shè)計(jì)中延時(shí)取0.005s。

2.3 繼電器電阻驅(qū)動(dòng)電路模塊

繼電器電阻驅(qū)動(dòng)電路模塊主要是FPGA根據(jù)鍵盤輸入的電阻值,判斷相應(yīng)的一些電阻是否要接入,從而使電阻對(duì)應(yīng)的繼電器閉合或斷開,給予其對(duì)應(yīng)的信號(hào)1或O即可。

2.4 仿真結(jié)果

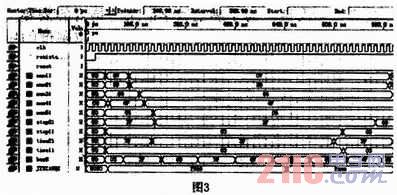

由上述理論可知,電阻1的產(chǎn)生原理和電阻2的產(chǎn)生原理完全一樣,為了使仿真結(jié)果更加明了,這里的仿真波形只用電阻1來驗(yàn)證其正確性,其仿真波形如圖3所示。

此圖是仿真圖中的一部分,只選擇了幾個(gè)有代表性的信號(hào)顯示出來加以說明,從圖中可以看出有時(shí)鐘信號(hào)clk,復(fù)位信號(hào)reset,電阻1選擇信號(hào) resistancel,numll至num51顯示的分別是電阻值的小數(shù)位、個(gè)位、十位、百位、干位。step11和step21分別顯示的是當(dāng)前工作的步數(shù)

的個(gè)位和十位,其中time11和time21分別顯示的是工作時(shí)間的個(gè)位和十位。Bus9則是動(dòng)態(tài)顯示時(shí)的數(shù)據(jù)信號(hào),JIDIANQI則代表的是16個(gè)繼電器的開關(guān)狀態(tài)。從上圖中可以看出該電阻的小數(shù)位的段碼為07H,對(duì)應(yīng)的二進(jìn)制就是00000111,其對(duì)應(yīng)顯示的數(shù)字是7即小數(shù)位為7,同理可知其個(gè)位數(shù)為5,十位數(shù)為4,百位數(shù)為3,千位數(shù)為1,所以其阻值就為1345.7Ω,從圖中可以看出總線上是循環(huán)傳遞著時(shí)間、步數(shù)和數(shù)值信息,根據(jù)阻值,其相應(yīng)的繼電器會(huì)閉合,根據(jù)上述電阻網(wǎng)絡(luò)原理,J4、J6、J8、J9、J10、J12、J14閉合,其余的繼電器均斷開,即對(duì)應(yīng)的二

進(jìn)制代碼為(0010101110101000)B,換算成十六進(jìn)制即為2BA8,從上圖可以看出其驗(yàn)證結(jié)果是正確的。

3 結(jié)束語

系統(tǒng)通過引進(jìn)FPGA來實(shí)現(xiàn)電阻提供這一模塊,且將周圍其他數(shù)字邏輯電路也集成至該芯片中。這樣既解決了系統(tǒng)的特殊性,又增強(qiáng)了系統(tǒng)的抗干擾性,提高了控制精度,也簡(jiǎn)化了調(diào)試。此外,本系統(tǒng)還將驅(qū)動(dòng)電路、編解碼電路等硬件通過VHDL語言在FPGA芯片中實(shí)現(xiàn),相比以前的模擬電路和單片機(jī)的實(shí)現(xiàn)方法,使用的元器件更少,體積也更小,針對(duì)不同場(chǎng)合,修改起來也更加方便。具有很好的市場(chǎng)前景。