摘要:為解決雷達(dá)作用距離和距離分辨力的問(wèn)題,分析了線性調(diào)頻脈沖壓縮的原理及工程實(shí)現(xiàn)方法,并利用Matlab軟件對(duì)加權(quán)前后的線性調(diào)頻信號(hào)脈沖壓縮波形進(jìn)行對(duì)比。簡(jiǎn)述了分布式(DA)算法的基本原理,給出一種基于FPGA分布式算法的時(shí)域脈沖壓縮實(shí)現(xiàn)結(jié)構(gòu),利用QuartusⅡ軟件完成脈沖壓縮處理模塊設(shè)計(jì)以及波形仿真。通過(guò)分析可以得出基于分布式算法實(shí)現(xiàn)的脈沖壓縮可以減少資源利用率,大大節(jié)省硬件資源。

關(guān)鍵詞:脈沖壓縮;匹配濾波器;分布式算法;FPGA

0 引言

隨著現(xiàn)代科技的發(fā)展,對(duì)雷達(dá)的作用距離、距離分辨力等性能提出了越來(lái)越高的要求。根據(jù)雷達(dá)理論,距離分辨力取決于信號(hào)的帶寬,探測(cè)距離取決于信號(hào)的時(shí)寬,所以理想的雷達(dá)信號(hào)應(yīng)具有大時(shí)寬帶寬積。單載頻脈沖信號(hào)的時(shí)寬帶寬積近似為1 ,因此作用距離與距離分辨力存在矛盾。采用脈沖壓縮可以有效解決上述矛盾,這樣既提高了雷達(dá)的作用距離,又保證了較高的距離分辨力。用數(shù)字方式實(shí)現(xiàn)的脈沖壓縮具有可靠性高,靈活性好,可編程、便于應(yīng)用。因此,這里介紹一種在FPGA上用分布式算法實(shí)現(xiàn)時(shí)域脈沖的壓縮,它是一種基于查找表的計(jì)算方法,與傳統(tǒng)算法(乘累加)相比,分布式算法可以極大地減少硬件電路地規(guī)模,易于實(shí)現(xiàn)流水線處理,從而提高電路的執(zhí)行速度。

1 脈沖壓縮原理及Matlab仿真

1.1 線性調(diào)頻信號(hào)脈沖壓縮原理

大時(shí)寬帶寬信號(hào)的實(shí)現(xiàn)是通過(guò)脈沖壓縮濾波器實(shí)現(xiàn)的。這時(shí)雷達(dá)發(fā)射信號(hào)是載頻按一定規(guī)律變化的寬脈沖,即具有非線性相位譜的寬脈沖。然而,脈沖壓縮濾波器具有與發(fā)射信號(hào)變化規(guī)律相反的延遲頻率特性,即脈沖壓縮器的相頻特性應(yīng)該與發(fā)射信號(hào)實(shí)現(xiàn)相位共軛匹配。所以,理想脈沖壓縮濾波器就是匹配濾波器。匹配濾波器的實(shí)現(xiàn)是通過(guò)對(duì)接收信號(hào)si(t)與匹配濾波響應(yīng)h(t)求卷積得到的,即:

![]()

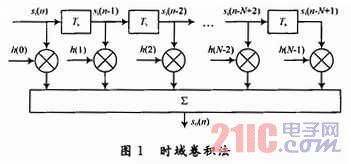

數(shù)字脈沖壓縮的實(shí)現(xiàn)方式有兩種。一是時(shí)域卷積法;二是頻域FFT法。時(shí)域處理方法比較直觀、簡(jiǎn)單,運(yùn)算量相對(duì)較少。另外,由于FPGA等器件的迅速發(fā)展,時(shí)域卷積法得到了更大程度的應(yīng)用。頻域FFT法是先經(jīng)過(guò)FFT的運(yùn)算,再進(jìn)行IFFT運(yùn)算,然后得到脈壓結(jié)果,其處理在本質(zhì)上是與時(shí)域卷積法一樣的。通常脈沖壓縮用數(shù)字濾波器來(lái)實(shí)現(xiàn),這時(shí)輸入信號(hào)si(t)需要通過(guò)A/D轉(zhuǎn)換器將其轉(zhuǎn)換為數(shù)字信號(hào)si(n)。此時(shí),脈沖壓縮匹配濾波器的輸出為:

![]()

其實(shí)現(xiàn)框圖如圖1所示。本文的設(shè)計(jì)就是按圖1的原理而實(shí)現(xiàn)的。

1.2 線性調(diào)頻脈沖壓縮的Matlab仿真

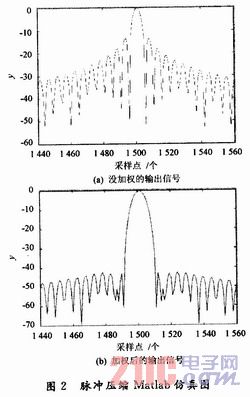

線性調(diào)頻信號(hào)經(jīng)過(guò)匹配濾波器直接得到的脈沖壓縮輸出信號(hào)并不理想,主副瓣比只有13.2 dB,這在多數(shù)情況下是不能滿足要求的。因?yàn)榇蟮母卑陼?huì)在主瓣周?chē)纬商摷倌繕?biāo),而且大目標(biāo)的副瓣也會(huì)掩蓋其鄰近距離上的小目標(biāo),造成小目標(biāo)丟失,所以必須降低輸出信號(hào)的副瓣。常用的方法就是加權(quán)方法。如何選擇加權(quán)函數(shù),應(yīng)根據(jù)應(yīng)用場(chǎng)合的需要,依據(jù)最佳準(zhǔn)則在副瓣抑制、主瓣展寬、信噪比損失、副瓣衰減速度以及技術(shù)實(shí)現(xiàn)的難易等幾個(gè)方面考慮。

下面,給出仿真信號(hào)模型,并在Matlab下進(jìn)行仿真,以分析加權(quán)前后的影響。仿真模型:脈沖寬度為150μs,調(diào)頻帶寬為2 MHz,采樣周期為0.1μs,加權(quán)方式為海明加權(quán)。圖2給出了采用加權(quán)函數(shù)前和采用海明加權(quán)函數(shù)后的脈沖壓縮波形圖。

通過(guò)海明加權(quán),主副瓣比大大改善,即副瓣得到了顯著的抑制。雖然海明加權(quán)后帶來(lái)了一定的信噪比損失,但匹配濾波器的性能得到了大大的提高。

2 分布式算法原理及4階FIR濾波器的設(shè)計(jì)

2.1 分布式算法原理

分布式算法(DA)是一種以實(shí)現(xiàn)乘累加運(yùn)算為目的的運(yùn)算方法,它與傳統(tǒng)乘加運(yùn)算的不同在于執(zhí)行部分積運(yùn)算的先后順序不同。傳統(tǒng)算法是在完成乘加功能時(shí),等到所有乘積產(chǎn)生之后,再進(jìn)行相加來(lái)完成乘加運(yùn)算的。而分布式算法則是通過(guò)將各輸入數(shù)據(jù)的每一對(duì)應(yīng)位產(chǎn)生的部分積預(yù)先進(jìn)行相加,形成相應(yīng)部分積,然后對(duì)各部分積進(jìn)行累加,形成最終結(jié)果的。與乘累加算法相比,分布式算法可極大地減少硬件電路規(guī)模,降低設(shè)計(jì)的復(fù)雜度,極大地提高可靠性和可操作性。分布式算法由串行、并行和串并結(jié)合而構(gòu)成的分布式算法。串行分布式算法是逐位的執(zhí)行,每個(gè)時(shí)鐘周期只能執(zhí)行1位,速度比較慢;并行分布式算法是1個(gè)時(shí)鐘周期完成1個(gè)字的運(yùn)算,速度比較快;串并結(jié)合的分布式算法

1次可以執(zhí)行多位,但是需要多個(gè)時(shí)鐘周期才能完成1個(gè)字的運(yùn)算,控制起來(lái)比較復(fù)雜。

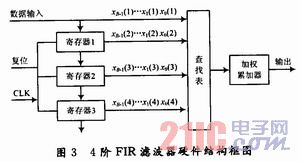

根據(jù)分布式算法的原理得出采用FPGA實(shí)現(xiàn)分布式算法的硬件結(jié)構(gòu),如圖3所示。

圖3中寄存器完成數(shù)據(jù)寄存,查找表完成數(shù)據(jù)查找運(yùn)算,加權(quán)累加器完成查表之后的加法。為了保證信號(hào)的完整性,即減少輸出毛刺,在數(shù)據(jù)輸出前用寄存器寄存一個(gè)時(shí)鐘周期然后輸出。

2.2 4階FIR濾波器的設(shè)計(jì)

本文的脈沖壓縮是通過(guò)并行分布式算法來(lái)實(shí)現(xiàn)的。從圖3可以得出,4階的FIR濾波器主要由移位寄存器、查找表和累加器組成。4為模塊的濾波器階數(shù),那么查找表中應(yīng)有24個(gè)存儲(chǔ)單元,如果濾波器階數(shù)過(guò)多,查找表規(guī)模隨階數(shù)的增加成指數(shù)遞增,因此階數(shù)較大時(shí)要分割查找表,分割查找表可以節(jié)省存儲(chǔ)資源,有利于成本和資源的節(jié)約。

要使4階FIR濾波器完成數(shù)據(jù)的輸入、串/并轉(zhuǎn)換、查表和加權(quán)累加,因?yàn)槭怯蟹?hào)數(shù)的運(yùn)算,所以要考慮累加最高位運(yùn)算符號(hào)。FIR濾波器是線性濾波器,低階濾波器的輸出集合相加,形成一個(gè)高階FIR濾波器的輸出。因此,在設(shè)計(jì)低階FIR時(shí),必須有2個(gè)輸出,一個(gè)用于FIR運(yùn)算的輸出,另一個(gè)輸出數(shù)據(jù)用于下一個(gè)FIR濾波器的運(yùn)算。為了保證信號(hào)的完整性,在程序設(shè)計(jì)時(shí),對(duì)輸入/輸出數(shù)據(jù)進(jìn)行了寄存處理。

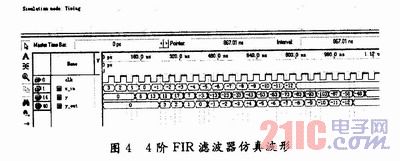

下面給出一個(gè)4階的FIR濾波器設(shè)計(jì)實(shí)例。輸入數(shù)據(jù)為12位有符號(hào)數(shù),匹配濾波系數(shù)為12位有符號(hào)數(shù),4階FIR的仿真波形如圖4所示。仿真結(jié)果與Matlab仿真結(jié)果完全一致,說(shuō)明設(shè)計(jì)是完全正確的。

3 64階匹配濾波器設(shè)計(jì)及仿真

由于匹配濾波器就是有限脈沖響應(yīng)濾波器,具有線性特性,所以通過(guò)低階濾波器的直接級(jí)聯(lián)相加就可以實(shí)現(xiàn)高階濾波器,前一個(gè)濾波器的移位數(shù)據(jù)y_out作為下一個(gè)濾波器模塊信號(hào)的輸入,每個(gè)濾波器模塊都與4階FIR設(shè)計(jì)相同,只需根據(jù)不同系數(shù)更改查找表中的數(shù)據(jù)。

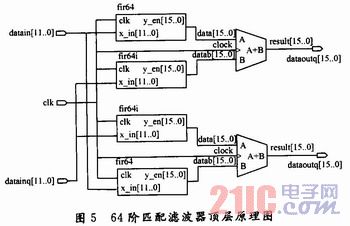

在64階匹配濾波器設(shè)計(jì)中,先用16個(gè)4階的FIR濾波器級(jí)聯(lián)成一個(gè)64階的FIR濾波器,然后再用4個(gè)64階的FIR濾波器組成一個(gè)64階的匹配濾波器,即64階的脈沖壓縮濾波器。64階脈沖壓縮濾波器的邏輯設(shè)計(jì)如圖5所示。

邏輯設(shè)計(jì)是以Altera公司的cycloneⅡ系列EP2C70為平臺(tái),在QuartusⅡ軟件中利用VHDL語(yǔ)言和原理圖進(jìn)行邏輯設(shè)計(jì),頂層為原理圖,底層為VHDL文件。圖5中,fir64模塊為匹配濾波器實(shí)部對(duì)應(yīng)的64階濾波器,fir64I模塊為匹配濾波器虛部對(duì)應(yīng)的64階濾波器,輸出為16 位的I、Q兩路信號(hào)。由Matlab軟件仿真出來(lái)的匹配濾波器的系數(shù)全部是小數(shù),然后進(jìn)行歸一化處理后得到匹配濾波系數(shù)。脈沖壓縮加權(quán)不涉及硬件規(guī)模的增加,只是對(duì)其系數(shù)乘以一個(gè)適當(dāng)?shù)募訖?quán)函數(shù),在實(shí)際的編程實(shí)現(xiàn)過(guò)程中與不加權(quán)的處理方法是完全一致的。

對(duì)該匹配濾波器進(jìn)行波形仿真,輸入為12位的有符號(hào)數(shù)據(jù),系數(shù)為12位有符號(hào)數(shù)據(jù),輸出為16位有符號(hào)數(shù)據(jù)。由于匹配濾波器做的是64×64點(diǎn)的卷積,所以輸出數(shù)據(jù)為64+64-1=127個(gè)。由于仿真數(shù)據(jù)較多,只給出了部分仿真結(jié)果,如圖6所示。

4 結(jié)語(yǔ)

仿真分析表明,脈壓輸出的實(shí)際值與Matlab仿真值十分接近,其誤差是由量化所產(chǎn)生的,系統(tǒng)具有很高的精度。通過(guò)仿真分析整個(gè)設(shè)計(jì),可得出利用基于分布式算法能夠大大減少數(shù)字脈沖壓縮的運(yùn)算量,減少FPGA的資源消耗。另外還可以根據(jù)不同的需求,增加脈沖壓縮階數(shù),更高階數(shù)的脈沖壓縮實(shí)現(xiàn)方法與64階的完全一致。由于匹配濾波器的系數(shù)對(duì)稱,所以可采用線性相位FIR濾波器在FPGA中的實(shí)現(xiàn)算法,這樣同等性能的濾波器設(shè)計(jì)可減小一半的硬件規(guī)模,這樣就會(huì)節(jié)省更多的邏輯單元,實(shí)現(xiàn)更多的功能。