1 引言:

LED視頻顯示屏由于亮度高、視角廣、壽命長(zhǎng)、功耗低、性價(jià)比高,而且具有可與計(jì)算機(jī)同步顯示各種文字、圖形、圖像,可實(shí)時(shí)播放電視、錄像、影碟等視頻信號(hào),可即時(shí)輸入、編輯各種多媒體數(shù)據(jù)等優(yōu)點(diǎn),使其在街頭、廣場(chǎng)、商業(yè)中心、運(yùn)動(dòng)場(chǎng)所、娛樂場(chǎng)所、控制中心等許多公共場(chǎng)合得到了廣泛的應(yīng)用。

隨著人們對(duì)視覺要求的不斷提高,如何在LED 大屏幕上實(shí)現(xiàn)自由立體顯示成為急待解決的問題。為此,筆者提出了一種新的解決方案,使得在LED 顯示屏上實(shí)現(xiàn)自由立體顯示成為可能,同時(shí)還降低了立體真彩LED 顯示系統(tǒng)的復(fù)雜性。

2 系統(tǒng)硬件設(shè)計(jì):

由自由立體顯示原理可知,要實(shí)現(xiàn)LED 立體顯示除了有立體信號(hào)源,對(duì)外還需要有自由立體LED 顯示屏和控制系統(tǒng)。由于自由立體顯示的一幀畫面需要一對(duì)圖像數(shù)據(jù),和現(xiàn)有的LED 大屏幕顯示器相比,要達(dá)到同樣的顯示規(guī)模其顯示數(shù)據(jù)量增加一倍,掃描速度也增加一倍,因此選擇Altera 的Nois 結(jié)構(gòu)。該結(jié)構(gòu)的特點(diǎn)是具有嵌入式系統(tǒng)IP 軟核,含有很多接口模塊,包括可配置高速緩存模塊、SDRAM 控制器、DMA、定時(shí)器、協(xié)處理器等。在植入(配置進(jìn))FPGA 前,用戶可根據(jù)設(shè)計(jì)要求,利用QuartusⅡ和SoPC builder,對(duì)Nois 及外圍系統(tǒng)進(jìn)行構(gòu)建,使該嵌入式系統(tǒng)在硬件結(jié)構(gòu)、功能特點(diǎn)、資源占用等方面全面滿足用戶設(shè)計(jì)系統(tǒng)的要求。特有的Avalon 總線結(jié)構(gòu)通信接口,使用戶可隨意配置32/16 位總線指令集和數(shù)據(jù)通道。

同時(shí)Avalon 的流模式結(jié)構(gòu)還能在沒有CPU 干預(yù)的情況下自動(dòng)按順序進(jìn)行數(shù)據(jù)傳輸,提高運(yùn)行速度,因此充分滿足自由立體LED 顯示器對(duì)速度的要求。

2.1 LED 立體顯示屏的設(shè)計(jì):

自由立體顯示是基于雙目視差原理實(shí)現(xiàn)的, 有4 種不同格式的圖像源,分別是SS 格式、TB 格式、FS 格式和FrS 格式。SS 格式為左、右視圖列交叉顯示;TB 格式、FS格式為左、右視圖行交叉顯示;FrS 格式為第1 幀奇數(shù)列、第2 幀偶數(shù)列列交叉顯示。對(duì)應(yīng)4 種不同的3D 模式,其數(shù)據(jù)存儲(chǔ)方式也有所區(qū)別。根據(jù)人類的視覺原理和SS 格式,本設(shè)計(jì)的LED 自由立體顯示屏設(shè)計(jì)成由特殊排列的紅、綠、藍(lán)子像素構(gòu)成,紅、綠、藍(lán)子像素的排列在水平方向上為自左至右均勻間隔排列構(gòu)成一個(gè)水平行,在垂直方向上為紅、綠、藍(lán)子像素各構(gòu)成一個(gè)垂直列,同樣均勻間隔排列。顯示屏上放置一塊光柵板,利用該光柵板保證觀察者通過光柵左眼只能看到顯示單元顯示的左眼圖像,而右眼只能看到顯示單元顯示的右眼圖像,從而獲得不用佩帶眼鏡就可以觀看的自由立體圖像,通過FPGA 控制器驅(qū)動(dòng)顯示自由立體動(dòng)態(tài)圖像。

2.2 FPGA 結(jié)構(gòu)設(shè)計(jì):

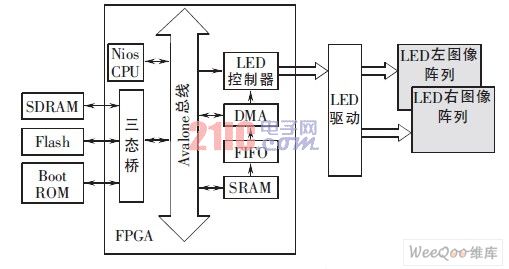

本系統(tǒng)采用可以在線配置Nios 軟核的FPGA 芯片EP1C6QC240C8。系統(tǒng)根據(jù)自由立體LED 的要求利用Avalon 總線配置了32 位CPU 軟核以及ROM,RAM,SRAM,F(xiàn)IFO,SDRAM 和DMA 等片內(nèi)外資源, 用以存儲(chǔ)和快速傳輸數(shù)據(jù), 同時(shí)還專門設(shè)計(jì)了LED 控制器以實(shí)現(xiàn)自由立體LED 顯示功能。

圖1 FPGA 系統(tǒng)結(jié)構(gòu)圖

系統(tǒng)硬件結(jié)構(gòu)如圖1 所示。Nios Ⅱ主端口的時(shí)鐘是內(nèi)部總線的時(shí)鐘,本系統(tǒng)采用50 MHz,用流模式傳輸?shù)淖畲髱捘苓_(dá)到100 Mbit/s。在電路設(shè)計(jì)時(shí),首先用硬件描述語言寫用戶邏輯,創(chuàng)建Alvalon Slave 接口使之直接和DMA 控制器的主端口相連接, 完成硬件設(shè)計(jì)。再在Nios Ⅱ IDE 環(huán)境下,用C 語言編寫DMA 初始化和控制程序,使得流模式的數(shù)據(jù)傳輸在FIFO 與Avalon 總線的接口上,能夠做到無縫連接。

2.3 立體LED 控制器的設(shè)計(jì):

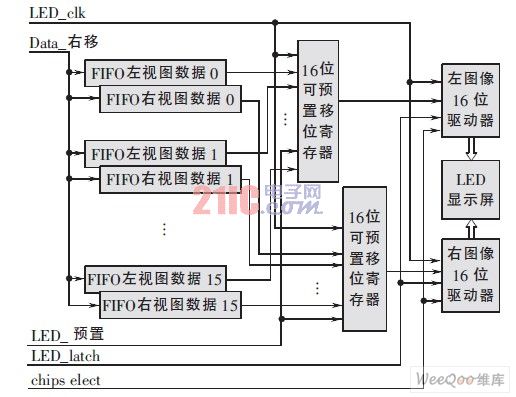

Avalon 流模式LED 控制器硬件結(jié)構(gòu)如圖2 所示,用硬件描述語言設(shè)計(jì)LED 時(shí)序發(fā)生器, 由于LED 各個(gè)像素點(diǎn)的色彩是以RGB 形式的亮度數(shù)據(jù)用二進(jìn)制數(shù)字方式存儲(chǔ)在SDRAM 中的,使用D/T 轉(zhuǎn)換技術(shù)[5]即亮度時(shí)間轉(zhuǎn)換技術(shù)就可以實(shí)現(xiàn)LED 屏的全彩顯示。筆者設(shè)計(jì)了一個(gè)專用的函數(shù)f(i),用此函數(shù)即可統(tǒng)一控制各個(gè)像素點(diǎn)實(shí)現(xiàn)全屏幕所有像素點(diǎn)相互獨(dú)立而又同步的D/T 轉(zhuǎn)換。這里,f(i)作為L(zhǎng)ED_latch 信號(hào)。

圖2 Avalon 流模式LED 控制器結(jié)構(gòu)圖

因?yàn)镕IFO 中的數(shù)據(jù)格式是左、右視圖列交叉顯示,因此LED 控制驅(qū)動(dòng)器的設(shè)計(jì)是以列驅(qū)動(dòng)的。LED 時(shí)序發(fā)生器的設(shè)計(jì)如圖3 所示,將立體圖像對(duì)中左、右眼圖像幀每個(gè)像素的數(shù)據(jù)用乒乓開關(guān)控制存儲(chǔ)在FIFO 緩存之中,以16 個(gè)列像素點(diǎn)的驅(qū)動(dòng)為例,F(xiàn)IFO 緩存之中的左、右視頻數(shù)據(jù)分別各連接一個(gè)16 位可預(yù)置移位寄存器,通過16 個(gè)時(shí)鐘脈沖的移位產(chǎn)生16 個(gè)像數(shù)的驅(qū)動(dòng)數(shù)據(jù),由片選信號(hào)選擇顯示行數(shù),由D/T 轉(zhuǎn)換函數(shù)f(i)作為L(zhǎng)ED_latch信號(hào)鎖存,F(xiàn)IFO 緩存的數(shù)據(jù)經(jīng)過8 次移位即可完成1 個(gè)像素的真彩驅(qū)動(dòng)。

圖3 LED 時(shí)序發(fā)生器內(nèi)部結(jié)構(gòu)圖

每幀畫面顯示1 個(gè)立體像素真彩信號(hào)的時(shí)間需要移位8 次, 即250 個(gè)基本周期。如果LED 大屏幕顯示器每秒最多顯示30 幀, 采用1/8 驅(qū)動(dòng)模式和立體像素的1/2時(shí)分復(fù)用, 再考慮選用16 位移位鎖存LED 恒流驅(qū)動(dòng)電路,實(shí)際要求的時(shí)鐘頻率為2 MHz。

3 系統(tǒng)軟件設(shè)計(jì)與仿真:

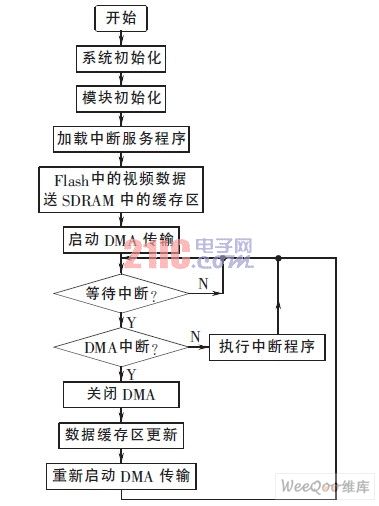

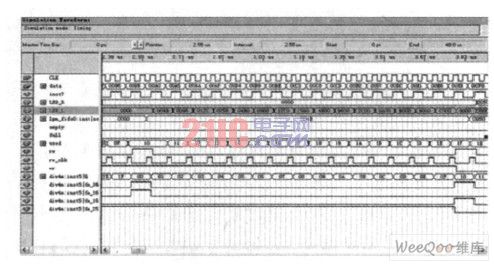

軟件設(shè)計(jì)就是利用SoPC Builder 生成軟件文件,用文本編輯器編寫匯編語言或C/C++源程序,用GUNPro 將源程序編譯成可執(zhí)行文件, 并通過下載電纜對(duì)可執(zhí)行程序進(jìn)行調(diào)試和運(yùn)行。軟件系統(tǒng)分為兩部分:主程序和中斷服務(wù)程序。主程序主要完成系統(tǒng)的初始化,其主要功能是:對(duì)于系統(tǒng)中的每一個(gè)微處理器,從設(shè)備都生成一個(gè)定義該設(shè)備地址的頭文件,為軟件開發(fā)創(chuàng)建存儲(chǔ)器映射文件。DMA 的操作都通過中斷服務(wù)程序執(zhí)行,把需要送出的像素信息排成一行順序送出形成數(shù)據(jù)流,借助于Avalon 流模式外設(shè)的設(shè)計(jì)方法, 實(shí)現(xiàn)一個(gè)Avalon 流模式的LED 控制器。利用DMA 控制器在流模式控制器和SRAM 之間建立一條DMA 傳送通道, 讓硬件來完成像素信息的自動(dòng)讀取。軟件流程如圖4 所示,部分內(nèi)部時(shí)序仿真如圖5 所示。

圖4 軟件流程圖

4 小結(jié):

在本文的設(shè)計(jì)中,利用SoPC 解決方案,選用Nios Ⅱ32 位處理器,根據(jù)人類的視覺原理,將3D 立體顯示SS格式數(shù)據(jù)在專門設(shè)計(jì)的帶有光柵的LED 立體顯示屏上顯示出來。采用了Avalon 總線的流數(shù)據(jù)傳輸結(jié)構(gòu)極大地提高了數(shù)據(jù)處理的速度,加快掃描頻率,同時(shí)專門設(shè)計(jì)了改進(jìn)型的D/T 轉(zhuǎn)換技術(shù), 使得系統(tǒng)只使用一個(gè)函數(shù)就實(shí)現(xiàn)了所有像素點(diǎn)亮度的控制,極大地降低了LED 時(shí)序電路發(fā)生器的復(fù)雜性。通過系統(tǒng)仿真得到了相對(duì)滿意的效果。但是在設(shè)計(jì)過程中發(fā)現(xiàn),LED 大屏幕顯示器前的光柵設(shè)計(jì)極為關(guān)鍵,包括與顯示屏的距離、光柵的具體尺寸、觀看的距離以及其間的相互關(guān)系等還有待進(jìn)一步研究。