引言

作為一種新型的通信技術,脈沖位置調(diào)制(PPM)系統(tǒng)依靠其編碼簡單、傳輸效率高等優(yōu)點,已廣泛應用于超寬帶移動通信、光通信、機載設備的空地數(shù)據(jù)鏈等諸多領域,同時PPM信號的調(diào)制和解調(diào)對整個通信系統(tǒng)的性能影響很大。

本文主要介紹了在QuartusII集成開發(fā)環(huán)境下,充分發(fā)揮數(shù)字設計的優(yōu)勢[1],利用Verilog HDL實現(xiàn)PPM系統(tǒng),并通過時序仿真結果來驗證設計方案。

PPM系統(tǒng)設計

PPM是利用脈沖的相對位置來傳遞信息的一種調(diào)制方式,其基本原理就是將碼元信息表示在一個幀時間段內(nèi)的某個時隙上,若一個碼元由n比特組成,該幀時間段含M個長度為t的時隙,則2^n=M。將n比特位編碼后對應成某個時隙上的脈沖來傳輸該碼元信息,而該幀時間段內(nèi)的其他時隙上則無脈沖,從而產(chǎn)生PPM信號。通常幀時間段還包含一個保護時間間隔Tp ,則系統(tǒng)的比特率為n/(M×t+Tp)。圖1即為一幀16-PPM信號示意圖,其中的脈沖則表示了當前碼元(0111)所對應的時隙。

PPM系統(tǒng)的主要原理相對簡單,所以可將重點放在代碼編寫和系統(tǒng)實現(xiàn)方面。設計過程中最重要的是各個模塊之間的接口設計,競爭冒險現(xiàn)象的避免等。

為透徹理解PPM系統(tǒng)原理及其本質(zhì),簡化PPM系統(tǒng)的設計,故在本文所設計的PPM系統(tǒng)中暫不考慮保護時間間隔Tp,同時取M=4,即設計一個4-PPM系統(tǒng),以便于通過仿真來驗證系統(tǒng)性能。

調(diào)制系統(tǒng)

通過上述原理介紹,可知PPM信號的調(diào)制實際上是一個計數(shù)輸出脈沖的過程[2],對時隙信號進行計數(shù),當它跟調(diào)制數(shù)據(jù)相等時就在相應的時隙輸出高電平“1”,其他時隙均輸出低電平“0”。

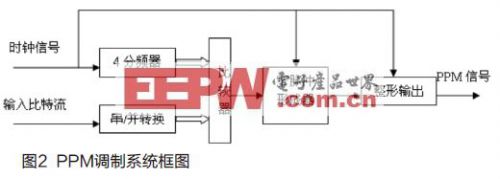

圖2是PPM調(diào)制系統(tǒng)的框圖,主要由串/并轉換、4分頻器、比較器、窄脈沖形成器、整形輸出等5個模塊。其中,串/并轉換模塊主要完成對輸入比特流的二進制編碼[3];4分頻器用于生成幀時間段內(nèi)的4個時隙;比較器完成對上述兩模塊輸出的高低對應位的匹配比較;窄脈沖形成器用于對比較器的輸出做成型濾波,限制PPM脈沖的帶寬,從而減小該PPM脈沖對相鄰頻帶內(nèi)信號造成的干擾;整形電路僅用D觸發(fā)器實現(xiàn),主要功能是鎖存PPM窄脈沖,與時鐘同步,從而避免競爭冒險現(xiàn)象[3~4]。

解調(diào)系統(tǒng)

在設計PPM解調(diào)系統(tǒng)時,考慮到PPM信號的產(chǎn)生原理,不難發(fā)現(xiàn)當輸入比特流為連續(xù)的“1”串或連續(xù)的“0”串時,PPM信號脈沖的間隔保持恒定,為4個時鐘周期。而只有在輸入比特流從“1”變?yōu)?ldquo;0”或者從“0”變?yōu)?ldquo;1”時,PPM信號脈沖的間隔才會發(fā)生變化[5]。所以可根據(jù)接收到的PPM信號脈沖間隔的不同來完成解調(diào),判斷原輸入比特是“1”還是“0”。

根據(jù)上述解調(diào)模型,可設計PPM解調(diào)系統(tǒng)框圖如圖3所示,主要由時鐘提取電路、脈沖位置檢測電路、譯碼器、整形輸出等模塊構成。其中,時鐘提取電路包括時隙同步[6]、幀同步和字同步[7]等,為簡單起見,在本設計中省略了時鐘提取模塊。脈沖位置檢測電路主要包括最短脈沖位置檢測、最長脈沖位置檢測。值得注意的是,在檢測最短脈沖位置時,需要移位兩個時鐘周期后再和原PPM信號相與才能判別出其位置,這是因為當數(shù)據(jù)信號從“1”變?yōu)?ldquo;0”的過渡階段,表示“1”的PPM信號前沿和表示“0”的PPM信號前沿間距為2個時鐘周期。同樣,整形輸出模塊也是依靠觸發(fā)器來鎖存數(shù)據(jù),完成整形。

PPM系統(tǒng)實現(xiàn)及時序仿真

Verilog編碼及原理圖

根據(jù)上述PPM系統(tǒng)的設計思想,基于FPGA的硬線邏輯特性,對各個功能模塊進行Verilog編碼來實現(xiàn),并在頂層利用原理圖輸入的方式完成整機互聯(lián)。而其中又以窄脈沖成型、為防止信號出現(xiàn)毛刺所作的整形電路、脈沖位置檢測電路等為相對重要的模塊。

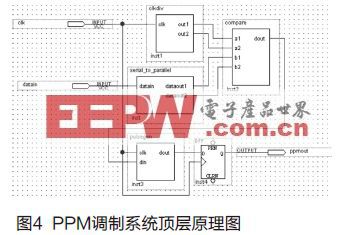

調(diào)制系統(tǒng)的頂層原理圖如圖4所示。

其中窄脈沖成型模塊性能的好壞影響著PPM脈沖對鄰近信道的干擾情況,在設計該模塊時可用觸發(fā)器與附加邏輯來做脈沖成型濾波,較為簡潔,其源代碼如下:

/*to generate the narrow pulse*/

module pulsegen (clk,din,dout) ;

input clk,din;

output dout;

reg temp;

assign dout=(~temp)& din;

always @ (posedge clk)

begin

temp<=din;

end

endmodule

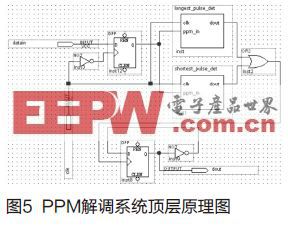

解調(diào)系統(tǒng)的頂層原理圖如圖5所示,最長脈沖位置檢測模塊和最短脈沖位置檢測模塊統(tǒng)一由時鐘的上升沿觸發(fā),起到了良好的同步作用。

其中最短脈沖位置檢測模塊相對更為重要,需要精確地移位兩個時鐘周期,可用串行移位寄存器實現(xiàn),其源代碼如下:

/*to detect the position of the

shortest pulse*/

module shortest_pulse_det

(clk,ppm_in,dout) ;

input clk,ppm_in;

output dout;

reg dout;

reg temp1,temp2,temp4;

wire temp3;

always @ (posedge clk)

begin

temp1<=ppm_in;

temp2<=temp1;

end

assign temp3=temp2&ppm_in;

always @ (posedge clk)

begin

temp4<=temp3;

dout<=temp4;

end

endmodule

時序仿真

對上述調(diào)制與解調(diào)模塊的頂層原理圖互聯(lián)后,在QuartusII平臺下選擇了Cyclone系列芯片EP1C3T100C6,運行時序仿真后得到整機系統(tǒng)的時序仿真圖如圖6所示。

通過圖6,可以發(fā)現(xiàn)該PPM系統(tǒng)的調(diào)制與解調(diào)部分均滿足要求,有著較好的性能。其中輸出比特流(dout)相對于輸入比特流(datain)有一定的延遲,這個延遲來源于兩個方面,一是系統(tǒng)設計中的整形模塊等所引入的延遲,二是布局布線后器件及連線的固有延遲。同時通過查看綜合報告,得知整機系統(tǒng)總共使用了14個LE,對邏輯資源的消耗較少。

結語

本文提出的基于FPGA的PPM系統(tǒng)的設計方案,在用簡明的Verilog HDL代碼實現(xiàn)后,對FPGA的邏輯資源消耗較少,而且電路性能較好,時序仿真結果證明了上述結論。對實際通信中PPM系統(tǒng)的應用具有一定的參考價值。在民用飛機機載設備S模式應答機的應答信號的傳輸過程中,采用的正是PPM體制,筆者將參考本文的設計方案,并做適當?shù)男薷模炞C其是否可用于S模式應答機的空地數(shù)據(jù)鏈中。