1 濾波和抗干擾" title="抗干擾">抗干擾概述

單片機(jī)應(yīng)用系統(tǒng)的輸入信號(hào)常含有種種噪聲和干擾,它們來自被測信號(hào)源、傳感器、外界干擾源等。為了提高測量和控制精度,必須消除信號(hào)中的噪聲和干擾。噪聲有兩大類:一類為周期性的;另一類為不規(guī)則的。前者的典型代表為50Hz的工頻干擾,一般采用硬件濾波,使用積分時(shí)間等于20ms的整數(shù)倍的雙積分A/D轉(zhuǎn)換器,可有效地消除其對(duì)信號(hào)的影響。后者為隨機(jī)信號(hào),它不是周期信號(hào),可用數(shù)字濾波" title="數(shù)字濾波">數(shù)字濾波方法予以消弱或?yàn)V除。所謂數(shù)字濾波,就是通過一定的計(jì)算或判斷程序來減少干擾信號(hào)在有用信號(hào)中的比重,故實(shí)際上它是一種軟件濾波。硬件濾波具有效率高的優(yōu)點(diǎn),但要增加系統(tǒng)的投資和設(shè)備的體積,當(dāng)干擾的性質(zhì)改變時(shí)我們往往不得不重新搭接電路;軟件濾波是用程序?qū)崿F(xiàn)的,不需要增加設(shè)備,故投資少、可靠性高、穩(wěn)定性好,并且可以對(duì)頻率很低的信號(hào)實(shí)行濾波,隨著干擾的性質(zhì)改變只需修改軟件即可,具有靈活、方便、功能強(qiáng)的優(yōu)點(diǎn),但要占用系統(tǒng)資源、降低系統(tǒng)的工作效率。一個(gè)傳統(tǒng)的實(shí)際系統(tǒng),往往采用軟件和硬件相結(jié)合的濾波方法,這種結(jié)合是在兩者的優(yōu)缺點(diǎn)之間尋找一個(gè)平衡點(diǎn)。

硬件抗干擾主要采用隔離技術(shù)、雙絞線傳輸、阻抗匹配等措施抑制干擾。常用的隔離措施有采用A/D、D/A與單片機(jī)進(jìn)行隔離以及用繼電器、光電隔離器、光電隔離固態(tài)繼電器(SSR)等隔離器件對(duì)開關(guān)量進(jìn)行隔離。

軟件抗干擾主要利用干擾信號(hào)多呈毛刺狀、作用時(shí)間短等特點(diǎn)。因此,在采集某一狀態(tài)信號(hào)時(shí),可多次重復(fù)采集,直到連續(xù)兩次或多次采集結(jié)果完全一致時(shí)才視為有效。若多次采集后,信號(hào)總是變化不定,可停止采集,給出報(bào)警信號(hào)。如果狀態(tài)信號(hào)是來自各類開關(guān)型狀態(tài)傳感器,對(duì)這些信號(hào)采集不能用多次平均方法,必須完全一致才行。在滿足實(shí)時(shí)性要求的前提下,如果在各次采集狀態(tài)信號(hào)之間增加一段延時(shí),效果會(huì)更好,能對(duì)抗較寬的干擾。對(duì)于每次采集的最高次數(shù)限額和連續(xù)相同次數(shù)均可按實(shí)際情況適當(dāng)調(diào)整。對(duì)于擾亂CPU的干擾,可以采取指令冗余和軟件陷阱等抗干擾技術(shù)加以抑制。

2 利用CPLD實(shí)現(xiàn)數(shù)字濾波及抗干擾

這里介紹的采用CPLD" title="CPLD">CPLD實(shí)現(xiàn)信號(hào)濾波及抗干擾的方法已經(jīng)在智能儀器泵沖測量儀的開發(fā)中得到驗(yàn)證。下面就如何采用CPLD對(duì)系統(tǒng)的四路外部傳感器脈沖信號(hào)和四路按鍵信號(hào)實(shí)現(xiàn)濾波、鎖存、中斷申請等功能進(jìn)行闡述。

2.1 傳感器信號(hào)濾波

由于要對(duì)傳感器信號(hào)進(jìn)行數(shù)字濾波,CPLD要引入時(shí)鐘信號(hào)。因而我們對(duì)CPLD定義一輸入端clki,作為數(shù)字濾波器的計(jì)數(shù)脈沖輸入端。clki由單片機(jī)定時(shí)器1定時(shí)產(chǎn)生500Hz脈沖。以一路為例,泵沖信號(hào)濾波部分如圖1所示。

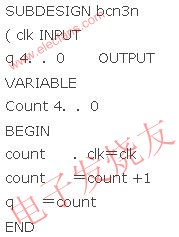

oo0為經(jīng)電平轉(zhuǎn)換后接近開關(guān)輸出的信號(hào)。當(dāng)oo0為低電平時(shí),說明泵1未動(dòng)作,封鎖三端與門,時(shí)鐘信號(hào)clki無法通過,計(jì)數(shù)器bcn3n不計(jì)數(shù)。同理,當(dāng)aa4為高電平時(shí),亦封鎖三端與門(至于aa4如何變化及作用下文有介紹)。故當(dāng)oo0為高、aa4為低時(shí),clki接通計(jì)數(shù)器CLK端。當(dāng)oo0和clr端任意一個(gè)為低時(shí),計(jì)數(shù)器清零。計(jì)數(shù)器bcn3n由MAX+PLUSII的文本編輯器編輯,其文本如下:

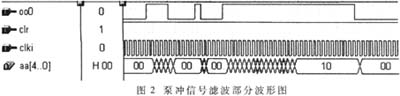

其輸出aa4..0等于計(jì)數(shù)器當(dāng)前的計(jì)數(shù)值。Aa4就是aa4..0的最高位當(dāng)計(jì)數(shù)值達(dá)到10H(十六進(jìn)制)時(shí),即aa4為高電平時(shí),三端與門封鎖,計(jì)數(shù)器保持10H不變,除非有清零信號(hào)。其波形如圖2所示。

由波形可知,oo0為高,計(jì)數(shù)器開始計(jì)數(shù)。對(duì)于小的脈沖,計(jì)數(shù)器的最高位即aa4為低,認(rèn)為是干擾信號(hào);只有當(dāng)aa4為"1"時(shí)才認(rèn)為oo0的脈沖信號(hào)有效,并通過aa4將時(shí)鐘脈沖阻斷,使計(jì)數(shù)器值不再增加。這樣做是為了防止由于oo0的脈沖不定寬,使aa4的電平不定,后面無法進(jìn)行處理。還應(yīng)注意的是,把oo0引入了清零信號(hào)。當(dāng)信號(hào)有較多毛刺時(shí),若oo0為低時(shí)不清零則使計(jì)數(shù)器不斷累加,積累到一定程度,使aa4為1,系統(tǒng)將認(rèn)為有一有效脈沖信號(hào),產(chǎn)生誤動(dòng)作。

2.2 中斷申請信號(hào)產(chǎn)生

中斷申請信號(hào)由圖3電路生成。

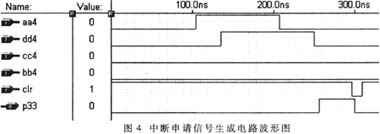

圖中四個(gè)計(jì)數(shù)器的最高位接四端或門,只要有一路信號(hào)為高,或門輸出就為高,并經(jīng)過非門,輸出低電平,接于D觸發(fā)器的時(shí)鐘端。D觸發(fā)器的D端始終為高電平。D觸發(fā)器為上升沿觸發(fā)器,若輸入D為1,在時(shí)鐘脈沖的上升沿,把"1"送入觸發(fā)器,使Q="1"。只有在CLRN端的clr信號(hào)有效時(shí),D觸發(fā)器清零,Q="0"。其波形如圖4所示。

只要有一路信號(hào)為高,D觸發(fā)器時(shí)鐘端為低。當(dāng)所有4路都為低時(shí),時(shí)鐘端由低變高,在上升沿,Q變?yōu)?quot;1",發(fā)出中斷請求信號(hào)。

如果多路脈沖信號(hào)有重疊,例如有兩路信號(hào)發(fā)生重疊,而中斷信號(hào)只有在四路都為低時(shí)才會(huì)產(chǎn)生,因此需要對(duì)信號(hào)進(jìn)行鎖存。本設(shè)計(jì)采用D觸發(fā)器來實(shí)現(xiàn)鎖存,電路如圖5所示。

當(dāng)aa4為由低變高時(shí),a4變?yōu)楦唠娖健S蒫lr信號(hào)清零。

2.3 按鍵消抖及數(shù)據(jù)輸出

按鍵的消抖也通過計(jì)數(shù)器來實(shí)現(xiàn),電路原理圖如圖6所示。

按鍵未按下時(shí)為高電平,封鎖時(shí)鐘信號(hào)。按鍵按下時(shí),計(jì)數(shù)器開始計(jì)數(shù)。當(dāng)計(jì)數(shù)器輸出最高位為"1"時(shí),亦封鎖時(shí)鐘信號(hào),防止按鍵時(shí)間不定使需要的k14信號(hào)不定。當(dāng)按鍵信號(hào)為高電平時(shí),對(duì)計(jì)數(shù)器清零,防止計(jì)數(shù)器累加干擾信號(hào)而造成誤動(dòng)作。波形如圖7所示。

歡迎轉(zhuǎn)載,本文來自電子發(fā)燒友網(wǎng)(www.elecfans.com)

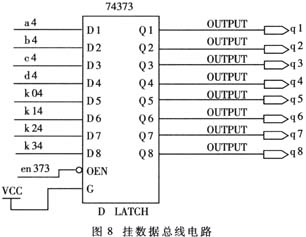

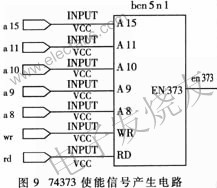

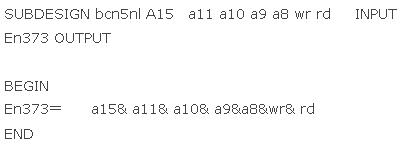

泵沖和按鍵經(jīng)處理后的信號(hào)a4、b4、c4、d4、k04、k14、k24、k34,經(jīng)74373掛于數(shù)據(jù)總線,如圖8所示。74373使能信號(hào)由圖9電路產(chǎn)生。

它采用文本編輯,具體如下:

若單片機(jī)發(fā)出讀81XXH地址中數(shù)的信號(hào),則選通此373,讀出其數(shù)。

以上介紹了采用CPLD實(shí)現(xiàn)數(shù)字濾波及抗干擾。該設(shè)計(jì)已在產(chǎn)品開發(fā)中成功應(yīng)用,效果良好,達(dá)到了預(yù)期的目的。前面我們已經(jīng)提到,一個(gè)傳統(tǒng)的設(shè)計(jì),往往在軟件濾波和硬件濾波兩者的優(yōu)缺點(diǎn)之間尋找一個(gè)平衡點(diǎn)。用我們通常的成語來講,這樣做可以說是揚(yáng)長避短或取長補(bǔ)短。一直以來,我們都把這兩個(gè)成語看成是褒義的,不過細(xì)細(xì)品味一下其中的韻味似乎并不完全是好的代表:發(fā)揚(yáng)長處固然值得稱道,但回避短處未必是解決問題的最佳途徑,畢竟回避并不能解決問題的本質(zhì),哪怕是取其長處來彌補(bǔ)短處,也不是長遠(yuǎn)出路。應(yīng)該直接去克服掉短處為佳。采用CPLD則可將軟硬件濾波的優(yōu)點(diǎn)兼而有之,同時(shí)將它們的缺點(diǎn)摒棄,從而達(dá)到揚(yáng)長去短的目的。用CPLD實(shí)現(xiàn)濾波只占用較少的資源,故可用其實(shí)現(xiàn)其它數(shù)字電路,同時(shí)實(shí)現(xiàn)濾波。