一個(gè)網(wǎng)絡(luò)的頻率特性包括幅頻特性和相頻特性,在系統(tǒng)設(shè)計(jì)時(shí),各個(gè)網(wǎng)絡(luò)的頻率特性對(duì)該系統(tǒng)的穩(wěn)定性、工作頻帶、傳輸特性等都具有重要影響。實(shí)際操作中,掃頻儀" title="掃頻儀">掃頻儀大大簡(jiǎn)化了測(cè)量操作,提高了工作效率,達(dá)到了測(cè)量過(guò)程快速、直觀、準(zhǔn)確、方便的目的,在生產(chǎn)、科研、教學(xué)上得到廣泛運(yùn)用。本設(shè)計(jì)采用數(shù)字頻率合成技術(shù)產(chǎn)生掃頻信號(hào),以單片機(jī)" title="單片機(jī)">單片機(jī)和FPGA" title="FPGA">FPGA為控制核心,通過(guò)A/D和D/A轉(zhuǎn)換器等接口電路,實(shí)現(xiàn)掃頻信號(hào)頻率的步進(jìn)調(diào)整、數(shù)字顯示及被測(cè)網(wǎng)絡(luò)幅頻特性與相頻特性參數(shù)的顯示。

1 系統(tǒng)總體方案及設(shè)計(jì)框圖

1.1 系統(tǒng)總體方案

將輸出頻率步進(jìn)可調(diào)的正弦掃頻信號(hào)源作為被測(cè)網(wǎng)絡(luò)的激勵(lì)Vi,可得被測(cè)網(wǎng)絡(luò)的響應(yīng)為V0。通過(guò)測(cè)量各頻率點(diǎn)的幅度就可得到V0和Vi的有效值,兩者之比就是該點(diǎn)的幅度頻率響應(yīng);對(duì)V0和Vi進(jìn)行過(guò)零比較、整形,再送到FPGA測(cè)量相位差,即可得到相頻特性。

設(shè)激勵(lì)信號(hào)Vi=x(n)=Acos(ω0n+f),穩(wěn)態(tài)輸出信號(hào)V0=y(n)。利用三角恒等式,可將輸入表示為兩個(gè)復(fù)指數(shù)函數(shù)之和: ,式中,

,式中, 。對(duì)于輸入為

。對(duì)于輸入為 ,線性時(shí)不變系統(tǒng)穩(wěn)態(tài)輸出為

,線性時(shí)不變系統(tǒng)穩(wěn)態(tài)輸出為 。根據(jù)線性性質(zhì)可知,輸入g(n)的響應(yīng)v(n)為:

。根據(jù)線性性質(zhì)可知,輸入g(n)的響應(yīng)v(n)為: 。同理,輸入g*(n)的輸出v*(n)是v(n)的復(fù)共軛。于是得到輸出y(n)的表達(dá)式:

。同理,輸入g*(n)的輸出v*(n)是v(n)的復(fù)共軛。于是得到輸出y(n)的表達(dá)式:

因此,輸出信號(hào)和輸入信號(hào)是頻率相同的正弦波,僅有2點(diǎn)不同:1)振幅被 加權(quán),即網(wǎng)絡(luò)系統(tǒng)在ω=ω0的幅度函數(shù)值;2)輸出信號(hào)的相位相當(dāng)于輸入有一個(gè)q(ω0)時(shí)延,即網(wǎng)絡(luò)系統(tǒng)在ω=ω0的相位值。該方案幅度和相位測(cè)量的控制都通過(guò)FPGA實(shí)現(xiàn),能夠使測(cè)量結(jié)果精確。

加權(quán),即網(wǎng)絡(luò)系統(tǒng)在ω=ω0的幅度函數(shù)值;2)輸出信號(hào)的相位相當(dāng)于輸入有一個(gè)q(ω0)時(shí)延,即網(wǎng)絡(luò)系統(tǒng)在ω=ω0的相位值。該方案幅度和相位測(cè)量的控制都通過(guò)FPGA實(shí)現(xiàn),能夠使測(cè)量結(jié)果精確。

1.2 系統(tǒng)總體設(shè)計(jì)框圖

系統(tǒng)通過(guò)鍵盤掃描得到外界設(shè)置的掃頻范圍和頻率步進(jìn),通過(guò)調(diào)用DDS" title="DDS">DDS控模塊控制DAC904,輸出掃頻信號(hào)。由于信號(hào)在被測(cè)網(wǎng)絡(luò)阻帶內(nèi)會(huì)有很大的衰減,故用程控放大處理經(jīng)被測(cè)網(wǎng)絡(luò)的掃頻信號(hào)之后,利用AD637進(jìn)行有效值采樣,LM311進(jìn)行整形。信號(hào)有效值經(jīng)MAXl270進(jìn)行AD轉(zhuǎn)換后得到有效值的數(shù)字量,整形后的信號(hào)經(jīng)測(cè)相模塊處理得到相位差值。在FPGA中寫入2個(gè)RAM存放被測(cè)信號(hào)的有效值和相位差值。完成一次掃頻后通過(guò)波形顯示模塊將幅頻、相頻曲線顯示在示波器上,并將特定頻率點(diǎn)的幅度和相位差值在液晶顯示器上進(jìn)行顯示。系統(tǒng)實(shí)現(xiàn)框圖如圖1所示。

2 系統(tǒng)功能部分設(shè)計(jì)

2.1 掃頻信號(hào)的產(chǎn)生

直接數(shù)字合成(DDFS)信號(hào)源。它是一種完全數(shù)字化的方法:先將一個(gè)周期的正弦波(或者其他波形)的離散樣點(diǎn)幅值的數(shù)字量預(yù)先存儲(chǔ)于ROM或者RAM中,按一定的地址增量間隔讀出,經(jīng)D/A轉(zhuǎn)換后成為不同頻率的模擬正弦波信號(hào)波形,再經(jīng)低通濾掉毛刺即可得到所需頻率的輸入信號(hào)。按此原理,DDS可以合成任意波形,且可以精確控制相位,頻率也非常穩(wěn)定。利用FPGA制作起來(lái)相當(dāng)容易,且掃頻步進(jìn)實(shí)現(xiàn)簡(jiǎn)單。設(shè)FPGA內(nèi)部的參考頻率源的頻率為fclk,采用計(jì)數(shù)容量為2N的相位累加器(N為相位累加器的位數(shù)),頻率控制字為M,則DDS系統(tǒng)輸出信號(hào)的頻率fout=fclk/2N×M。頻率分辨率為:△f=fclk/2N。

若選取晶振頻率為40 MHz,頻率控制字為24位,相位累加器的位數(shù)為31位,則輸出頻率范圍為0.02 Hz~312 kHz,步進(jìn)頻率為40 MHz/231≈0.02 Hz。

系統(tǒng)采用高速14-bit電流輸出型D/A轉(zhuǎn)換器DAC904制作DDS掃頻信號(hào)源。通過(guò)FPGA給其20 MHz的時(shí)鐘信號(hào)以輸出10 Hz~100 kHz的掃頻信號(hào)。該器件制作成的PCB板中,很好地考慮了接地,使得輸出信號(hào)在頻率為1 MHz可以達(dá)到無(wú)明顯失真。DAC904采用內(nèi)部基準(zhǔn)和雙極性接法,輸出信號(hào)幅值范圍為0~5 V。其原理圖如圖2所示。

2.2 幅頻特性測(cè)試方案

使用集成真有效值轉(zhuǎn)換器AD637先檢測(cè)出信號(hào)每個(gè)頻率點(diǎn)的有效值,再經(jīng)過(guò)A/D采樣將得到的數(shù)據(jù)讀到單片機(jī)中進(jìn)行處理即可。該器件外接電路簡(jiǎn)單,工作頻帶很寬,與A/D轉(zhuǎn)換器級(jí)聯(lián),可以對(duì)任何復(fù)雜波形的有效值、平均值、均方值、絕對(duì)值進(jìn)行采樣,測(cè)量誤差小于±(0.2%讀數(shù)+0.5 mV),可以達(dá)到很高的測(cè)量精度。

2.3 相頻特性測(cè)試方案

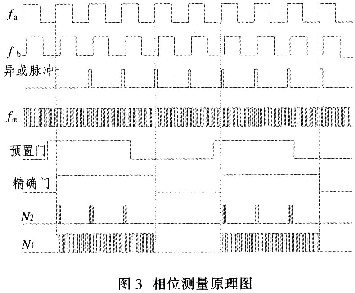

采用計(jì)數(shù)法實(shí)現(xiàn)相位的測(cè)量。計(jì)數(shù)法的思想是將相位量轉(zhuǎn)化為數(shù)字脈沖量,然后對(duì)數(shù)字脈沖進(jìn)行測(cè)量而得到相位差。對(duì)轉(zhuǎn)換后的數(shù)字脈沖量進(jìn)行異或運(yùn)算,產(chǎn)生脈寬為T0、周期為T的另一路方波,若高頻計(jì)數(shù)時(shí)鐘脈沖周期為TCP,則在一個(gè)周期T的時(shí)間內(nèi)的計(jì)數(shù)數(shù)值為:

式中,φx為相位差的度數(shù)。

這種方法應(yīng)用比較廣泛,精度較高,電路形式簡(jiǎn)單,適合FPGA實(shí)現(xiàn)。

實(shí)際測(cè)量中,當(dāng)兩輸入信號(hào)頻率較高且相位差很小時(shí),得到的脈沖很窄,這會(huì)造成較大誤差。為了克服上述缺陷,引入等精度測(cè)量的思想(如圖3),采用多周期同步計(jì)數(shù)法,利用觸發(fā)器產(chǎn)生一個(gè)寬度為被測(cè)信號(hào)fa整數(shù)倍的閘門信號(hào)。利用計(jì)數(shù)器1測(cè)量出閘門信號(hào)內(nèi)通過(guò)高頻脈沖fm的個(gè)數(shù)N1,利用計(jì)數(shù)器2測(cè)量出相同時(shí)間內(nèi)閘門信號(hào)、異或信號(hào)、高頻脈沖三者相與后的脈沖數(shù)N2。因此,相位差值為△φ=N2/N1x36 0°。測(cè)量相位的同時(shí),在FPGA內(nèi)部引入一D觸發(fā)器,用一路方波信號(hào)控制另一路方波,通過(guò)觸發(fā)器輸出的高低以判斷信號(hào)相位差范圍是大于180°還是小于180°。

2.4 系統(tǒng)顯示電路設(shè)計(jì)

為了在示波器上顯示曲線,需要通過(guò)2個(gè)D/A轉(zhuǎn)換器向X、Y軸同步送入掃描信號(hào)和數(shù)據(jù)信號(hào)。X軸方向的DA轉(zhuǎn)換器輸出掃描信號(hào)為O~5 V的鋸齒波信號(hào),而數(shù)據(jù)信號(hào)為-5~5 V,反應(yīng)了各個(gè)頻率點(diǎn)上的信號(hào)幅值和相位,由另一片D/A轉(zhuǎn)換器向Y軸方向輸出。

3 系統(tǒng)軟件設(shè)計(jì)

系統(tǒng)軟件設(shè)計(jì)由單片機(jī)和FPGA組成。整個(gè)系統(tǒng)以用戶按鍵中斷為主線,調(diào)用不同的處理函數(shù),與FPGA中各個(gè)控制模塊之間,以總線的進(jìn)行數(shù)據(jù)的交換,實(shí)現(xiàn)了系統(tǒng)測(cè)量頻率特性的功能。軟件流程圖見圖4。

4 結(jié)束語(yǔ)

本掃頻儀利用數(shù)字頻率合成技術(shù)(DDS)產(chǎn)生掃頻信號(hào),通過(guò)14位D/A轉(zhuǎn)換器DAC904產(chǎn)生了10 Hz~100 kHz的正弦掃頻信號(hào),作用于被測(cè)網(wǎng)絡(luò)。網(wǎng)絡(luò)的輸出信號(hào)通過(guò)有效值采樣電路,以及由比較器LM311配合FPGA內(nèi)部實(shí)現(xiàn)的測(cè)相電路,完成了對(duì)被測(cè)網(wǎng)絡(luò)頻率特性的測(cè)量。

為對(duì)系統(tǒng)的性能進(jìn)行測(cè)試,制作了一個(gè)中心頻率為5 kHz。帶寬為±50 Hz的阻容雙T網(wǎng)絡(luò)。測(cè)試結(jié)果表明,在網(wǎng)絡(luò)的通帶和阻帶內(nèi),相頻特性測(cè)量均達(dá)到了3°以內(nèi)的測(cè)量精度,幅頻特性的測(cè)量誤差均小于50%。此外,該系統(tǒng)可以通過(guò)鍵盤輸入掃頻范圍,通過(guò)示波器顯示幅頻、相頻曲線,并可以在液晶顯示器上顯示該網(wǎng)絡(luò)在特定頻率點(diǎn)上的幅度、相位特性值。該系統(tǒng)操作簡(jiǎn)單,成本低廉,測(cè)量精確,具有很強(qiáng)的實(shí)用性。

,式中,

,式中,![]() 。對(duì)于輸入為

。對(duì)于輸入為![]() ,線性時(shí)不變系統(tǒng)穩(wěn)態(tài)輸出為

,線性時(shí)不變系統(tǒng)穩(wěn)態(tài)輸出為![]() 。根據(jù)線性性質(zhì)可知,輸入g(n)的響應(yīng)v(n)為:

。根據(jù)線性性質(zhì)可知,輸入g(n)的響應(yīng)v(n)為:![]() 。同理,輸入g*(n)的輸出v*(n)是v(n)的復(fù)共軛。于是得到輸出y(n)的表達(dá)式:

。同理,輸入g*(n)的輸出v*(n)是v(n)的復(fù)共軛。于是得到輸出y(n)的表達(dá)式:![]()

![]() 加權(quán),即網(wǎng)絡(luò)系統(tǒng)在ω=ω0的幅度函數(shù)值;2)輸出信號(hào)的相位相當(dāng)于輸入有一個(gè)q(ω0)時(shí)延,即網(wǎng)絡(luò)系統(tǒng)在ω=ω0的相位值。該方案幅度和相位測(cè)量的控制都通過(guò)FPGA實(shí)現(xiàn),能夠使測(cè)量結(jié)果精確。

加權(quán),即網(wǎng)絡(luò)系統(tǒng)在ω=ω0的幅度函數(shù)值;2)輸出信號(hào)的相位相當(dāng)于輸入有一個(gè)q(ω0)時(shí)延,即網(wǎng)絡(luò)系統(tǒng)在ω=ω0的相位值。該方案幅度和相位測(cè)量的控制都通過(guò)FPGA實(shí)現(xiàn),能夠使測(cè)量結(jié)果精確。