摘 要:本控制儀以單片機(jī)80c196kc為核心,集無(wú)功補(bǔ)償、電度量計(jì)量、電能質(zhì)量監(jiān)測(cè)及通信于一體,能實(shí)時(shí)顯示電網(wǎng)的各項(xiàng)參數(shù),通過(guò)鍵盤(pán)可人工設(shè)定系統(tǒng)運(yùn)行的參數(shù)。單片機(jī)外圍芯片PSD8XX及復(fù)雜可編程邏輯器件(CPLD)的使用不僅使系統(tǒng)的硬件電路簡(jiǎn)化,而且使系統(tǒng)的性能提高。本文將討論用CPLD來(lái)實(shí)現(xiàn)控制儀的鍵盤(pán)系統(tǒng),給出了硬件電路和軟件設(shè)計(jì)方法。

1 引言

無(wú)功補(bǔ)償裝置是用于補(bǔ)償電網(wǎng)無(wú)功功率的不足,提高功率因數(shù),保證供電系統(tǒng)安全運(yùn)行和節(jié)約電能的設(shè)備,其核心是控制儀。本控制儀集無(wú)功補(bǔ)償、電度量計(jì)量、電能質(zhì)量監(jiān)測(cè)及通信于一體,對(duì)電網(wǎng)參數(shù)進(jìn)行實(shí)時(shí)采樣與計(jì)算并把各項(xiàng)參數(shù)顯示在LCD上,還可通過(guò)鍵盤(pán)進(jìn)行系統(tǒng)參數(shù)設(shè)置,用于改變控制儀的運(yùn)行模式等。

控制儀的最小系統(tǒng)由單片機(jī)80c196kc和可編程單片機(jī)外圍接口芯片PSD834F2組成,這樣既省去了地址鎖存器和譯碼器等一些小規(guī)模芯片,使硬件電路得到了簡(jiǎn)化,又提高了系統(tǒng)的可靠性。系統(tǒng)運(yùn)行所需要的程序、數(shù)據(jù)和參數(shù)均放在PSD834F2中。用復(fù)雜可編程邏輯器件(CPLD)取代一些數(shù)字器件擴(kuò)展系統(tǒng)的外圍電路,進(jìn)一步提高了系統(tǒng)的性能,還便于調(diào)試和維護(hù)。本文以下將具體介紹如何用CPLD來(lái)擴(kuò)展鍵盤(pán)和顯示電路。

2 鍵盤(pán)輸入模塊的硬件設(shè)計(jì)

鍵盤(pán)輸入主要用于現(xiàn)場(chǎng)電流變比,電容器組數(shù),單組電容器容量,電壓上、下限,諧波上限,控制儀地址編號(hào)等系統(tǒng)參數(shù)設(shè)置。而且與顯示模塊配合用于查看各相電壓、電流,無(wú)功功率,有功功率,功率因數(shù)等的情況。

設(shè)計(jì)鍵盤(pán)時(shí),如果采用軟件掃描的方式,雖然硬件電路簡(jiǎn)單,但掃描會(huì)耗去CPU不少時(shí)間,降低系統(tǒng)的整體性能;如果采用接口芯片8279來(lái)管理鍵盤(pán),雖可代替CPU完成對(duì)鍵盤(pán)的控制,減輕CPU的負(fù)擔(dān),但8279體積大且功能單一。所以,本系統(tǒng)采用復(fù)雜可編程邏輯器件(CPLD)來(lái)設(shè)計(jì)鍵盤(pán)的接口電路,完成對(duì)鍵盤(pán)的掃描工作,當(dāng)有鍵按下時(shí),則產(chǎn)生中斷信號(hào)供CPU讀取掃描碼。除此之外,CPLD還可實(shí)現(xiàn)其它模塊的接口電路以及完成地址譯碼等功能。

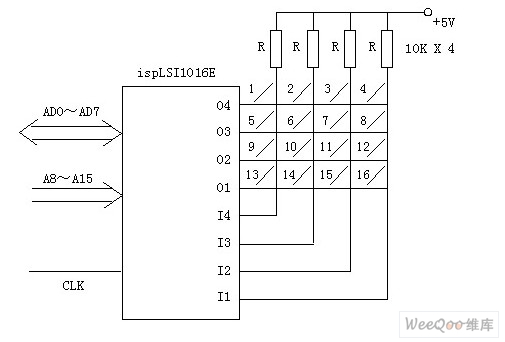

本系統(tǒng)采用4X4鍵盤(pán),其硬件電路如圖1:

圖1 4X4 鍵盤(pán)框圖

CPLD采用LATTICE公司的ispLSI1016E-100L器件,該器件包括32個(gè)I/O引腳,4個(gè)專(zhuān)用引腳,集成密度為2000個(gè)PLD等效門(mén),引腳至引腳的延遲為7.5ns,工作頻率為100MHz。該器件由集總布線區(qū)(GRP)和萬(wàn)能邏輯塊(GLB)構(gòu)成,GLB通過(guò)GRP連接起來(lái)。

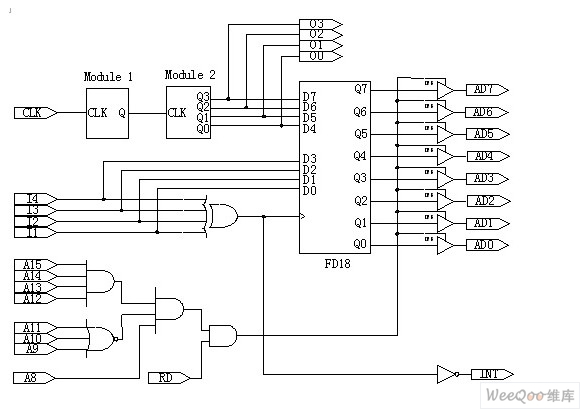

對(duì)復(fù)雜可編程邏輯器件(CPLD)內(nèi)部邏輯功能的描述方式有多種,本系統(tǒng)采用了原理圖輸入與VHDL語(yǔ)言描述相結(jié)合的方式,這樣可以發(fā)揮兩者的優(yōu)勢(shì),加快開(kāi)發(fā)進(jìn)程。設(shè)計(jì)時(shí)采用層次化設(shè)計(jì),描述系統(tǒng)總體功能的最上層使用原理圖輸入,而原理圖中的某些功能模塊采用VHDL編寫(xiě)。實(shí)際原理圖如圖2:

圖2 鍵盤(pán)邏輯實(shí)際原理圖

上圖中Module 1模塊實(shí)現(xiàn)分頻功能,CLK來(lái)自單片機(jī)80C196KC的CLKOUT腳,其周期為3個(gè)時(shí)鐘振蕩周期,占空比為33%。若單片機(jī)用16M晶振,其頻率約為:16M/3=5.33M。Module 1 把頻率降至約1K,Module 2模塊以一秒的間隔使O3~O0依次循環(huán)輸出低電平進(jìn)行鍵盤(pán)掃描 。當(dāng)有鍵按下時(shí),I3~I(xiàn)0中有一個(gè)為低電平,異或門(mén)輸出1個(gè)高電平脈沖,鎖存鍵盤(pán)狀態(tài)并向單片機(jī)申請(qǐng)中斷。系統(tǒng)為鍵盤(pán)分配的地址空間為0xf100~0xf1ff,在此范圍內(nèi)可讀取鍵盤(pán)的掃描碼。

由于篇幅有限,以下只給出Module 2的VHDL語(yǔ)句,具體如下:

LIBRARY ieee;

USE ieee.STd_logic_1164.ALL;

USE ieee.std_logic_unsigned.ALL;

ENTITY Module2 IS

PORT ――定義端口

( clk :IN std_logic;

q :OUT std_logic_vector(3 DOWNTO 0)

);

END Module2;

ARCHITECTURE Module2 of Module2 IS

BEGIN

PROCESS(clk)

VARIBLE sum:integer:=0; ――定義變量sum,初值為0

BEGIN

IF(clk’event AND clk=’1’)THEN

sum:=sum+1; ――clk為上升沿時(shí),sum加1

IF(sum>=5)THEN

sum:=1;

END IF;

END IF;

CASE sum IS ――根據(jù)sum輸出相應(yīng)的值

WHEN 1 => q<=“1110”;

WHEN 2 => q<=“1101”;

WHEN 3 => q<=“1011”;

WHEN 4 => q<=“0111”;

WHEN THERS => q<=“1111”;

END CASE;

END PROCESS;

END Module2;

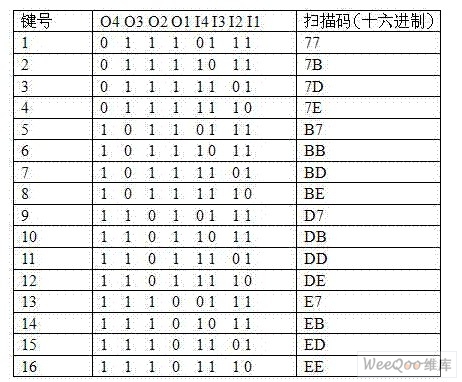

3 鍵盤(pán)掃描碼與相應(yīng)鍵的對(duì)應(yīng)關(guān)系

中斷服務(wù)程序讀取寄存器FD18中的掃描碼,經(jīng)過(guò)判斷就可知道按下的是哪一個(gè)鍵,然后轉(zhuǎn)入相應(yīng)的程序進(jìn)行處理。鍵號(hào)和掃描碼的具體對(duì)應(yīng)關(guān)系如表1:

表1 鍵號(hào)和掃描碼對(duì)應(yīng)表

4 鍵盤(pán)輸入模塊的軟件設(shè)計(jì)

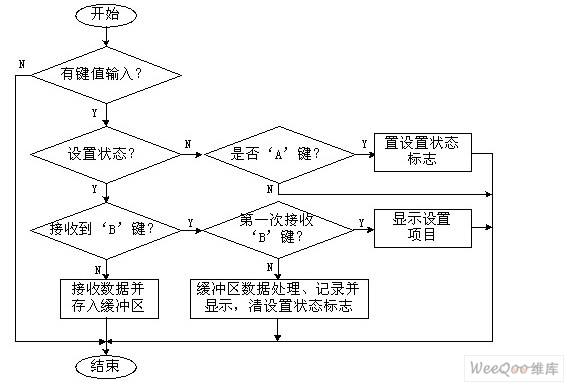

系統(tǒng)的一些基本參數(shù)可以通過(guò)鍵盤(pán)來(lái)設(shè)置或改變,每按下一鍵,CPLD掃描到鍵值后向CPU申請(qǐng)中斷。CPU進(jìn)入鍵盤(pán)管理中斷程序后,讀取、存儲(chǔ)鍵值并置接收到鍵值標(biāo)志。主程序識(shí)別到標(biāo)志,對(duì)接收到的鍵值進(jìn)行處理。

參數(shù)設(shè)置格式是:A**B**…*B。也就是說(shuō),按‘A’鍵進(jìn)入設(shè)置狀態(tài),‘**’的組合表示設(shè)置項(xiàng)目,‘B’確認(rèn)設(shè)置項(xiàng)目,‘**…*’所設(shè)置項(xiàng)目的數(shù)值,最后的‘B’是結(jié)束符,表示此次設(shè)置結(jié)束。設(shè)置步驟的軟件處理流程如圖3:

圖3 系統(tǒng)參數(shù)設(shè)置處理流程圖

5 結(jié)束語(yǔ)

用復(fù)雜可編程邏輯器件(CPLD)擴(kuò)展的鍵盤(pán)接口經(jīng)過(guò)實(shí)用,效果較好,既提高了單片機(jī)的響應(yīng)速度,又簡(jiǎn)化了硬件電路。此外,CPLD還可用于其它的接口設(shè)計(jì),使其性能得到進(jìn)一步體現(xiàn)。