DDS(Direct Digital Freqiaency Synthesizers)廣泛應(yīng)用于雷達系統(tǒng)、數(shù)字通信、電子對抗、電子測量等民用軍用設(shè)備中。它是隨著半導(dǎo)體技術(shù)和數(shù)字技術(shù)的快速發(fā)展而發(fā)展起來的新型的頻率合成技術(shù),與傳統(tǒng)的VCO+PLL的模擬方式產(chǎn)生所需頻率相比,DDS技術(shù)具有頻率分辨率高,相位噪聲低,帶寬較寬,頻譜純度好等優(yōu)點。這些技術(shù)指標(biāo)在一個系統(tǒng)中是至關(guān)重要的,決定著一個系統(tǒng)的成敗。

1 DDS的基本原理

1.1 頻率合成方式的基本原理

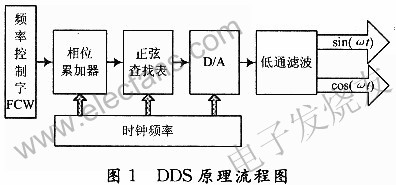

DDFS是根據(jù)余弦函數(shù)相位和幅值的對應(yīng)關(guān)系,從相位出發(fā),由不同的相位給出不同的電壓幅值,再經(jīng)過D/A變換和濾波最后得到一定頻率和調(diào)頻率的模擬信號。由此可見,DDS有很多功能模塊組成,如圖1所示。

若相位累加器有N位,時鐘頻率為fclk,頻率控制字為FCW。N位的相位累加器可以對時鐘頻率進行2N分頻,所以DDS的精度可以達到:

![]()

頻率控制字是用來控制累加器的步進的,累加器的步進為![]() 。假設(shè)初始的相位偏移△φ=0,則經(jīng)過N個時鐘周期后相位累加器的輸出θ=2π*FCW*N*(1/2N)。在相位步進△0時,完成2π的相位變化即為完成一個輸出周期,所以20/△θ*Tclk=T0,即:

。假設(shè)初始的相位偏移△φ=0,則經(jīng)過N個時鐘周期后相位累加器的輸出θ=2π*FCW*N*(1/2N)。在相位步進△0時,完成2π的相位變化即為完成一個輸出周期,所以20/△θ*Tclk=T0,即:

![]()

可見調(diào)節(jié)FCW可以任意地按照要求改變輸出頻率,這就達到了頻率合成的目的。

1.2 直讀方式DDS的原理

直讀法(DDWS)工作流程是,把所需要的DDS的波形,直接用Matlab抽樣量化,然后把量化的數(shù)據(jù)直接存儲到FPGA的BlockRAM中,再在時鐘頻率的控制下直接從BlockRAM中讀取數(shù)據(jù),D/A后輸出原來波形。

2 數(shù)字實現(xiàn)

2.1 DDFS的數(shù)字實現(xiàn)

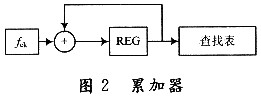

由于D/A之前都是數(shù)字部分,為了分析其原理數(shù)字控制的實現(xiàn)過程,參考如圖2所示結(jié)構(gòu)。

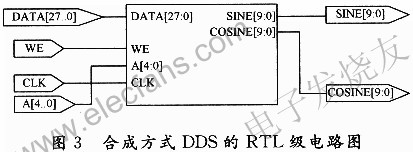

相位累加器是由一個加法器和一個寄存器構(gòu)成,假設(shè)累加器位數(shù)N=6,那么000000代表0弧度,000001代表弧度,相應(yīng)的000010代表(2π/64)*2弧度,111111代表(2π/64)*63弧度。若頻率控制字FCW=000011,并且累加器中的初始相位為O,則經(jīng)過N=21個時鐘周期后形成的二進制序列為000000,000011,…,111111,對應(yīng)的相位分別為O,(2π/64)*3,…,(2π/64)*63。當(dāng)?shù)?2個時鐘周期到來時,加法器溢出,所有位數(shù)重置為0,另一個循環(huán)周期開始。查找表可以用FPGA中BlockRAM做成,前面的二進制序列作為地址,相位對應(yīng)的幅度值作為地址對應(yīng)的值存儲起來,這樣在時鐘頻率的控制下通過二進制序列可從BlockRAM中讀取相應(yīng)的幅值,經(jīng)過D/A后就為所需要的模擬波形。圖3為FPGA綜合后的RTL級電路圖。

2.2 DDWS的數(shù)字買現(xiàn)

DDWS的數(shù)字實現(xiàn)較為簡單,把通過Matlab抽樣量化后的數(shù)據(jù)直接保存為.BAT數(shù)據(jù)格式,然后在FPGA中用IP核的BlockRAM生成一個ROM,把數(shù)據(jù)存儲進去,這樣就可以根據(jù)時鐘要求輸出需要的數(shù)據(jù)了。

圖4為FPGA仿真后的RTL級電路圖。

3 DDS的性能指標(biāo)

3.1 頻率分辨率

對于頻率合成方式的DDS,只要是累加器的位數(shù)足夠多,理論上可以達到任意無限高的頻率分辨率。由式(1),若N=39,fclk=1,分辨率可達到0.000 18 Hz。但是對于直讀方式,分辨率是受到硬件D/A速度限制的,一般如果用四倍的頻率速度采集和恢復(fù),分辨率只能達到O.25 Hz。

3.2 SFDR

最常用的評價DDS工作性能的參數(shù)是帶外抑制比(SFdR),它是指有效信號的頻譜幅度與噪聲頻譜幅度的最大值之差。實際的頻譜合成方式的DDS在累加器的輸出和查找表之間還有個相位折斷的過程。若累加器的輸出A為N位,查找表的輸入B為M位,一般情況下N>M,這是為了節(jié)約查找表的空間。正是由于這種相位折斷才降低了SFDR,使得DDS的性能變壞。以上參數(shù)都是可以根據(jù)實際的要求估算出來的,例如要產(chǎn)生一個4 MHz、分辨率為O.4 Hz、帶外抑制比為60 dB的正弦信號,時鐘頻率為100 MHz。那么根據(jù)式(2),可以得到N=11;根據(jù)實際經(jīng)驗,查找表的每位可以產(chǎn)生6 dB的抑制比,所M=60/6=10 b。由于直接讀取法DDS不存在相位折斷的問題,所以往往能得到比較好的SFDR。

3.3 信噪比

由于SFDR只與最大噪聲的頻譜幅度有關(guān),所以相同的SFDR可能有不同的頻譜純度,為此引入了另外一個DDS的性能指標(biāo)——信噪比(SNR )。信噪比是指信號功率和噪聲功率之比,由于涉及到所有的噪聲,所以跟頻譜純度息息相關(guān),對于頻率分辨率高的DDS,噪聲的能量較低,信噪比較大,頻譜純度好。

4 Matlab仿真結(jié)果

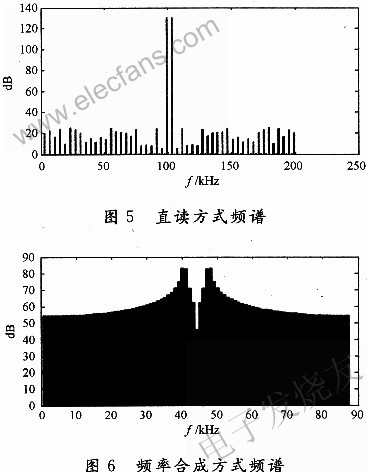

根據(jù)兩種DDS的FPGA的仿真數(shù)據(jù),可以通過Matlab仿真輸出波形,如圖5,圖6所示。

可以根據(jù)圖很明顯地看出以上三個性能參數(shù)的比較情況,直讀DDS的SFDR要大得多,而且頻譜純度也好,合成方式的頻率分辨率高。

5 結(jié)語

從以上比較可以發(fā)現(xiàn)直讀方式是實際應(yīng)用中非常好的選擇,但是對于這種方式,只能輸出有限的預(yù)先設(shè)定好的頻率和調(diào)頻率,不具有通用性適合用在特定的場合。而頻率合成的DDS能合成任意頻率和調(diào)頻率,也能通過一定的措施達到所需指標(biāo),所以這種原理是一種通用的原理,被科研工作者和DDS制造商廣泛采用。在雷達系統(tǒng)(比如高度計、散射計)中,往往只需要某一種或者幾種特定的調(diào)頻率、帶寬、頻率的DDS,所以可以較多地采用直讀方式。