現(xiàn)場(chǎng)可編程器件(FPGA和CPLD)等ISP器件無(wú)須編程器,利用器件廠商提供的編程套件,采用自頂而下的模塊化設(shè)計(jì)方法,使用原理圖或硬件描述語(yǔ)言(VHDL)等方法來(lái)描述電路邏輯關(guān)系,可直接對(duì)安裝在目標(biāo)板上的器件編程。它易學(xué)、易用、簡(jiǎn)化了系統(tǒng)設(shè)計(jì),減小了系統(tǒng)規(guī)模,縮短設(shè)計(jì)周期,降低了生產(chǎn)設(shè)計(jì)成本,從而給電子產(chǎn)品的設(shè)計(jì)和生產(chǎn)帶來(lái)了革命性的變化。

1、系統(tǒng)結(jié)構(gòu)及工作原理

LED點(diǎn)陣顯示控制的傳統(tǒng)方式是采用單片機(jī)或系統(tǒng)機(jī)作為CPU來(lái)實(shí)現(xiàn),當(dāng)系統(tǒng)顯示的信息比較多時(shí),由于單片機(jī)的輸入/輸出端口(I/O)有限,采用此方式的成本將大大增加,系統(tǒng)和程序的設(shè)計(jì)難度也急劇增加;而且,當(dāng)系統(tǒng)完成后修改、改變顯示方式或擴(kuò)展時(shí),所需改動(dòng)的地方比較大,甚至有可能需要重新設(shè)計(jì);另外,在以顯示為主的系統(tǒng)中,單片機(jī)的運(yùn)算和控制等主要功能的利用率很低,單片機(jī)的優(yōu)勢(shì)得不到發(fā)揮,相當(dāng)于很大得資源浪費(fèi)。如果采用現(xiàn)場(chǎng)可編程邏輯器件作為CPU來(lái)設(shè)計(jì)控制器,選擇合適的器件, 利用器件豐富的I/O口、內(nèi)部邏輯和連線資源,采用自頂而下的模塊化設(shè)計(jì)方法,可以方便地設(shè)計(jì)整個(gè)顯示系統(tǒng)。

由于PLD器件的外圍器件很少,且可以利用PLD的編程端口(可復(fù)用)進(jìn)行在系統(tǒng)編程,使得系統(tǒng)的修改、顯示方式的改變和擴(kuò)展都變的非常簡(jiǎn)單、方便。

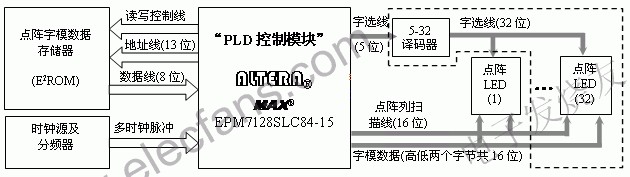

本系統(tǒng)采用單個(gè)16×16LED點(diǎn)陣逐列左移(或右移)顯示漢字或字符,需顯示漢字或符號(hào)的16×16點(diǎn)陣字模已經(jīng)存放在字模存儲(chǔ)器中。顯示控制器由復(fù)雜可編程邏輯器件(CPLD)EPM7128SLC84-15來(lái)實(shí)現(xiàn),系統(tǒng)組成原理框圖如圖1所示。

系統(tǒng)原理是PLD控制模塊首先產(chǎn)生點(diǎn)陣字模地址,并從存儲(chǔ)器讀出數(shù)據(jù)存放在16位寄存器中,然后輸出到LED點(diǎn)陣的列,同時(shí)對(duì)點(diǎn)陣列循環(huán)掃描以動(dòng)態(tài)顯示數(shù)據(jù),當(dāng)需要顯示數(shù)據(jù)字模的列和被選中的列能夠協(xié)調(diào)配合起來(lái),就可以正確顯示漢字或符號(hào)。

圖1 點(diǎn)陣顯示控制器原理框圖

2、控制器設(shè)計(jì)及工作原理

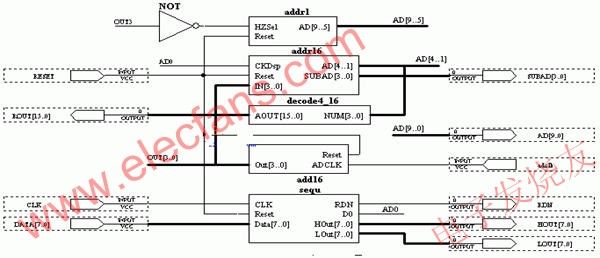

從框圖中可以看出,系統(tǒng)的關(guān)鍵在于控制器的設(shè)計(jì)。LED點(diǎn)陣顯示數(shù)據(jù)地址的產(chǎn)生、點(diǎn)陣列掃描和需顯示數(shù)據(jù)的配合以及點(diǎn)陣顯示方式控制的實(shí)現(xiàn)都必須由控制器來(lái)實(shí)現(xiàn)。對(duì)單個(gè)16×16LED點(diǎn)陣顯示控制器進(jìn)行設(shè)計(jì)的頂層邏輯原理圖如圖2所示。

圖2 控制器頂層電路原理圖

原理圖中包含5個(gè)模塊,其中sequ模塊產(chǎn)生讀信號(hào)RDN和10位地址線(AD[9..0])中的最低位地址AD0,AD0和其它模塊產(chǎn)生的地址配合,通過(guò)8位數(shù)據(jù)線(DATA[7..0])從存儲(chǔ)器讀出列高字節(jié)(AD0=1時(shí))和低字節(jié)(AD0=0時(shí)),由于16×16點(diǎn)陣字模數(shù)據(jù)為32個(gè)字節(jié),每列含兩個(gè)字節(jié)即16位,它由HOUT[7..0]和LOUT[7..0] 來(lái)構(gòu)成;模塊add16由adclk提供一個(gè)慢時(shí)鐘構(gòu)成16進(jìn)制計(jì)數(shù)器,它的輸出送給addr16模塊,為變模計(jì)數(shù)器addr16提供一個(gè)模,通過(guò)模的規(guī)律變化以控制點(diǎn)陣按照左移或右移等顯示方式進(jìn)行顯示;模塊decode4_16是一個(gè)4—16譯碼器,其輸出ROUT[15..0]連接到LED點(diǎn)陣的列,可選中16×16LED點(diǎn)陣的某列,并顯示sequ模塊輸出的點(diǎn)陣高低字節(jié)(字模)數(shù)據(jù);模塊addr16為點(diǎn)陣顯示控制的核心,為了實(shí)現(xiàn)點(diǎn)陣漢字從右到左逐列移動(dòng)顯示,它由add16模塊提供的模,在addr16內(nèi)部構(gòu)成兩個(gè)變模計(jì)數(shù)器,其中一個(gè)用來(lái)產(chǎn)生讀字模數(shù)據(jù)的地址AD[4..1],另外一個(gè)產(chǎn)生16×16LED點(diǎn)陣列掃描選擇地址SUABAD[3..0],列掃描選擇地址由decode4_16譯碼后輸出;模塊addr1為字選擇計(jì)數(shù)器,其輸出可以控制多塊LED顯示器的顯示及其顯示方式。

控制核心模塊addr16采用AHDL語(yǔ)言設(shè)計(jì),在開(kāi)發(fā)軟件MAX+plus Ⅱ10.2中實(shí)現(xiàn),程序如下所示。

SUBDESIGN addr16

(

ckdsp,reset,in[3..0]:INPUT;

ad[4..1],subad[3..0]:OUTPUT;

)

VARIABLE

reg1[3..0]: DFF;

reg2[3..0]: DFF;

reg3[3..0]: DFF;

BEGIN

reg1[].clk=ckdsp;

reg1[].clrn=reset;

reg2[].clk=ckdsp;

reg2[].clrn=reset;

reg3[].clk=!ckdsp;

reg3[].clrn=reset;

reg2[].d=15-in[];

if reg1[].q>=in[] then

reg1[].d=0;

else

reg1[].d=reg1[].q+1;

end if;

ad[]=reg1[];

reg3[].d=reg1[].q+reg2[].q;

subad[]=reg3[].q;

END;

p;

reg2[].clrn=reset;

reg3[].clk=!ckdsp;

reg3[].clrn=reset;

reg2[].d=15-in[];

if reg1[].q>=in[] then

reg1[].d=0;

else

reg1[].d=reg1[].q+1;

end if;

ad[]=reg1[];

reg3[].d=reg1[].q+reg2[].q;

subad[]=reg3[].q;

END;

為了實(shí)現(xiàn)字符由右到左逐列移動(dòng)顯示,模塊addr16內(nèi)部設(shè)計(jì)了兩個(gè)由add16控制的變模加法計(jì)數(shù)器,其中一個(gè)輸出為ad[4..1](4位地址線),另一 個(gè)輸出為subad[3..0](列掃描控制線)。

從程序可以看出,當(dāng)模輸入in[3..0]=0時(shí),ad[4..1]=0,而subad[3..0]=15,此時(shí)ad[9..5]亦等于零,AD0在0和1間變化,即讀出第一個(gè)字符的第一列并顯示在LED的第16列;當(dāng)模輸入in[3..0]=1時(shí),在記數(shù)脈沖AD0的作用下,ad[4..1]和subad[3..0]都為二進(jìn)制加法計(jì)數(shù)器,但ad[4..1]由0加到1返回到0,同時(shí)subad[3..0]由14加到15返回到14,此時(shí)ad[9..5]仍然等于零,AD0在0和1間變化,即讀出第一個(gè)字符的第一、二列并顯示在LED的第15、16列…由此類推,可見(jiàn)當(dāng)模塊add16的加法記數(shù)輸出由0變到15時(shí),LED點(diǎn)陣字符將由左到右逐列移動(dòng)顯示。

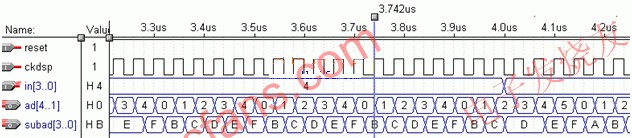

以上程序在MAX+plusⅡ10.2上仿真驗(yàn)證結(jié)果如圖3所示。由仿真結(jié)果可以看到,由計(jì)數(shù)模控制輸入in[3..0]控制的兩個(gè)變模計(jì)數(shù)器輸出ad[4..1]和subad[3..0]的結(jié)果正確無(wú)誤。

圖3 addr16模塊仿真時(shí)序圖

在設(shè)計(jì)中,應(yīng)注意模塊sequ的記數(shù)時(shí)鐘CLK頻率的選擇應(yīng)遠(yuǎn)遠(yuǎn)大于模塊add16的記數(shù)時(shí)鐘adclk的頻率,addr16的記數(shù)時(shí)鐘為地址最低位AD0,字選擇計(jì)數(shù)器的時(shí)鐘脈沖為16進(jìn)制模塊add16的最高位OUT3。這樣,ad[4..1]和subad[3..0]同步變化的足夠快,在點(diǎn)陣LED上可以看到完整的字符,并當(dāng)add16記數(shù)到15產(chǎn)生進(jìn)位返回到0時(shí),字選擇模塊addr1獲得一個(gè)記數(shù)脈沖并加1(上升沿觸發(fā)),此后將顯示下一個(gè)字符。

3、系統(tǒng)擴(kuò)展

以上為顯示單個(gè)字符系統(tǒng),若要同時(shí)顯示多個(gè)字符時(shí),可以按照?qǐng)D1加入虛線框內(nèi)部分,并且模塊addr1設(shè)計(jì)成addr16的格式,把AD4作為addr1的記數(shù)脈沖即可。按照EPM7128SLC84—15的資源(64個(gè)I/O口,2個(gè)全局時(shí)鐘,1個(gè)全局復(fù)位和5個(gè)可復(fù)用專用端口,5000個(gè)等效邏輯門(mén),192個(gè)內(nèi)部寄存器),若不外部擴(kuò)展譯碼器,可以有效控制約16個(gè)字符的顯示;而采用外部譯碼器時(shí),可以控制的字符數(shù)將大大增加,但須注意時(shí)鐘CLK的頻率需要提高,以視覺(jué)不能看到整個(gè)字符的閃爍為基準(zhǔn)。

4、結(jié)論

以上點(diǎn)陣字符顯示系統(tǒng)在開(kāi)發(fā)軟件MAX+plusⅡ10.2上經(jīng)仿真驗(yàn)證無(wú)誤,并且已經(jīng)成功地應(yīng)用在煤礦電力監(jiān)控系統(tǒng)的大屏幕顯示中。另外,由于器件含有豐富的可編程連線資源,當(dāng)系統(tǒng)顯示方式和顯示字符個(gè)數(shù)變化時(shí),只需要通過(guò)開(kāi)發(fā)工具修改控制器的控制邏輯和連接關(guān)系,再將修改完成的程序通過(guò)下載電纜下載到器件即可,而電路板可以不做任何改動(dòng),可見(jiàn),系統(tǒng)的維護(hù)和修改是極其方便和容易的。當(dāng)然,由于CLPD的驅(qū)動(dòng)能力有限,當(dāng)點(diǎn)陣LED顯示亮度不夠時(shí),需要添加LED驅(qū)動(dòng)電路以得到合適的LED顯示亮度。