現(xiàn)代電子戰(zhàn)環(huán)境日趨復(fù)雜,信號(hào)日趨密集,新體制雷達(dá)不斷出現(xiàn),雷達(dá)信號(hào)的各個(gè)參數(shù)以各種規(guī)律變化,因而從密集復(fù)雜的信號(hào)環(huán)境中分選和識(shí)別各種新體制雷達(dá)信號(hào)就成了電子戰(zhàn)信號(hào)處理的一大難題。為了滿足電子支援措施(ESM)實(shí)時(shí)信號(hào)分選的需要,對(duì)處理器的處理時(shí)間提出了較高的要求:不僅要求處理器的硬件結(jié)構(gòu)具有良好的設(shè)計(jì)和可不斷優(yōu)化的空間,而且要求器件有較高的集成性,這些已成為不可忽視的因素。經(jīng)過(guò)對(duì)相關(guān)器件的深入分析和研究,本文采用高速現(xiàn)場(chǎng)可編程門陣列器件(FPGA)替代中小規(guī)模集成芯片來(lái)設(shè)計(jì)三參數(shù)關(guān)聯(lián)比較器,從而實(shí)現(xiàn)預(yù)分選器設(shè)計(jì)。

1 基于關(guān)聯(lián)比較器的信號(hào)預(yù)分選原理

關(guān)聯(lián)比較器技術(shù)對(duì)高密度信號(hào)環(huán)境下的硬件預(yù)分選有著積極和重要的意義。關(guān)聯(lián)比較器用于信號(hào)預(yù)分選的思路源于傳統(tǒng)信號(hào)處理方法中的輻射源參數(shù)匹配方法。目前,電子戰(zhàn)系統(tǒng)中對(duì)雷達(dá)信號(hào)實(shí)時(shí)分選可利用的信息仍然是雷達(dá)信號(hào)的五大參數(shù):載頻(RF)、脈寬(PW)、到達(dá)方位(DOA)、到達(dá)時(shí)間(TOA)、脈幅(PA)。其中RF一般集中在若干離散的頻率點(diǎn)上,聚斂性好,因此是偵察信號(hào)處理中最重要的特征之一;DOA取決于雷達(dá)和偵察機(jī)的相對(duì)方位角,當(dāng)雷達(dá)與偵察機(jī)之間沒(méi)有相對(duì)運(yùn)動(dòng)時(shí),DOA為常數(shù),存在相對(duì)運(yùn)動(dòng)時(shí),DOA變化緩慢,該參數(shù)不受雷達(dá)信號(hào)本身影響,也是偵察信號(hào)處理中最重要的特征之一;由于雷達(dá)信號(hào)PW本身比較穩(wěn)定,數(shù)值分布較集中,具有很好的平穩(wěn)性和聚斂性,因此也可以作為分選特征之一;由于影響PA的因素太多,使PA的平穩(wěn)性較差,可信度不高,一般不作為分選依據(jù);而TOA一般作為主處理器的主要分選、識(shí)別參數(shù),一般也不作為預(yù)處理分選依據(jù)。因此從理論上講預(yù)處理可利用的有3個(gè)參數(shù):RF,PW,DOA。

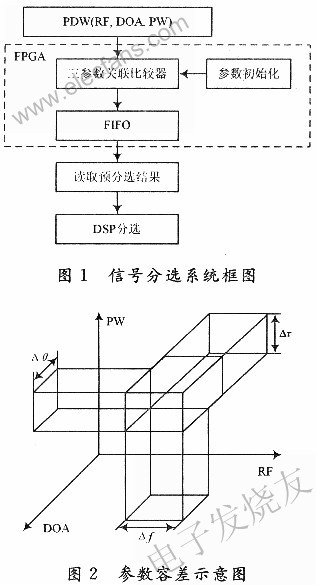

分選系統(tǒng)的框圖如圖1所示,脈沖分選分為預(yù)分選和主分選兩部分,預(yù)分選為RF,PW,DOA三參數(shù)聯(lián)合分選,由FPGA完成;主分選為重頻(PRI)分選,由DSP完成。

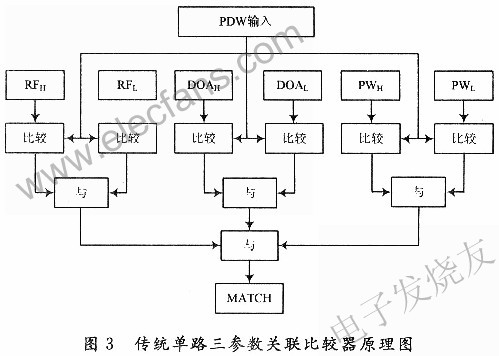

根據(jù)RF,PW,DOA構(gòu)成的三參數(shù)關(guān)聯(lián)比較器原理如圖2所示。每部雷達(dá)信號(hào)在空間占據(jù)一個(gè)小盒,小盒的中心坐標(biāo)可以認(rèn)為是雷達(dá)參數(shù),小盒的尺寸取決于參數(shù)容差,這與接收機(jī)的測(cè)量精確度有關(guān)。只要測(cè)量達(dá)到一定精確度,選取合適的容差范圍,就可以對(duì)此小盒內(nèi)的脈沖進(jìn)行去交錯(cuò),最后確定脈沖序列的存在。

2 關(guān)聯(lián)比較器的設(shè)計(jì)

由于輻射源特征的多樣性以及脈沖參數(shù)測(cè)量誤差的引入,使雷達(dá)截獲系統(tǒng)脈沖去交錯(cuò)存在以下兩方面的問(wèn)題:

(1)由于參數(shù)抖動(dòng)或存在測(cè)量誤差,使得參數(shù)是一個(gè)由上下門限界定的一個(gè)范圍。

(2)由于存在參數(shù)捷變或參數(shù)分集,使得參數(shù)存在多值(如頻率捷變、分集等)。

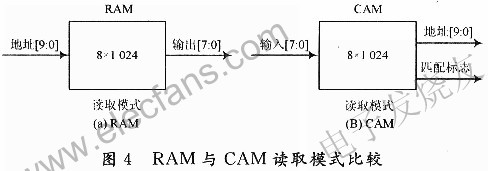

傳統(tǒng)的關(guān)聯(lián)比較器的原理圖如圖3所示,這種方法是給每個(gè)參數(shù)設(shè)定一個(gè)容差,將每個(gè)脈沖的PDW與各參數(shù)容差進(jìn)行比較,實(shí)際上就是與RF,DOA,PW的最大值與最小值做比較,如果都落在容差范圍內(nèi),則產(chǎn)生相應(yīng)路數(shù)的單路匹配信號(hào)MATCH。這種方法能夠解決第一個(gè)問(wèn)題,但是對(duì)于參數(shù)捷變雷達(dá)則不能進(jìn)行分選。另外,由于每一路只能配置一組雷達(dá)參數(shù),對(duì)于日益復(fù)雜的電磁環(huán)境,這種方法已不適應(yīng)。

本文在傳統(tǒng)的關(guān)聯(lián)比較器上進(jìn)行改進(jìn),設(shè)計(jì)了基于CAM(Content.Addressable Memory)的關(guān)聯(lián)比較器。CAM是一種專門為快速查找數(shù)據(jù)地址而設(shè)計(jì)的存儲(chǔ)器,通過(guò)把輸入數(shù)據(jù)與其內(nèi)所存數(shù)據(jù)同時(shí)相比較,能快速確定輸入數(shù)據(jù)是否與其內(nèi)部某個(gè)數(shù)據(jù)或幾個(gè)數(shù)據(jù)相匹配。CAM的數(shù)據(jù)尋址方式因不同應(yīng)用要求而不同,最快方式下僅需要一個(gè)時(shí)鐘周期便可完成對(duì)所有數(shù)據(jù)的尋址。

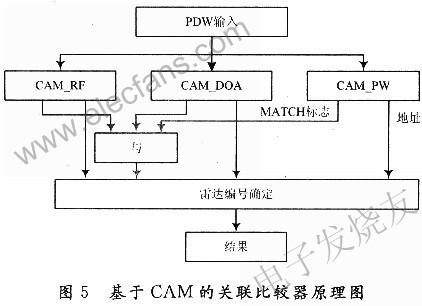

與RAM一樣,CAM也是采取陣列式數(shù)據(jù)存儲(chǔ),其數(shù)據(jù)的寫入方式與RAM相類似,但CAM的數(shù)據(jù)讀取方式卻不同。在RAM中,輸入的是數(shù)據(jù)地址,輸出的是數(shù)據(jù),而在CAM中輸入的是所要查詢的數(shù)據(jù),輸出的是數(shù)據(jù)地址和匹配標(biāo)志。

在RAM中,RAM的存儲(chǔ)容量由地址線寬度所確定。例如,10b寬地址總線的RAM存儲(chǔ)容量為210=1024B,CAM卻沒(méi)有這個(gè)限制,因?yàn)樗皇遣捎脗鹘y(tǒng)的通過(guò)地址讀取數(shù)據(jù)的方式。如要從1024B中查詢某一數(shù)據(jù),輸入數(shù)據(jù)寬度為8b,若數(shù)據(jù)存在,則輸出匹配標(biāo)志和10b寬的數(shù)據(jù)地址。因?yàn)镃AM不是采用傳統(tǒng)的地址線模式讀取數(shù)據(jù),存儲(chǔ)空間可以很容易的擴(kuò)展,輸入數(shù)據(jù)線寬度只由需查詢的數(shù)據(jù)位數(shù)決定。圖4為數(shù)據(jù)讀取模式下的RAM和CAM。

基于CAM的關(guān)聯(lián)比較器原理如圖5所示,三個(gè)CAM中分別存儲(chǔ)了多部雷達(dá)的RF,DOA,PW參數(shù)。當(dāng)PDW進(jìn)來(lái)時(shí),如果CAM中有與之匹配的參數(shù),則MATCH標(biāo)志位輸出1,并輸出參數(shù)地址,根據(jù)輸出三個(gè)CAM輸出的地址和MATCH標(biāo)志位判定輻射源編號(hào)。同傳統(tǒng)方法一樣,這種方法也可以進(jìn)行多路組合,實(shí)現(xiàn)對(duì)PDw的高速處理。

3 基于CAM的關(guān)聯(lián)比較器的FPGA實(shí)現(xiàn)

本文使用的FPGA為Xilinx公司Virtex 4系列的XC4VSX55。ISE11.1為用戶提供了CAM版本為6.1的IP核,其配置界面如圖6所示。

3.1 地址匹配類型

CAM輸出地址匹配類型有三種配置,默認(rèn)為binary encoded,也就是輸出匹配的地址信息。另外,也可以配置成single-match unencoded和multi-match unencoded,這兩種模式輸出的就是一個(gè)位數(shù)與CAM內(nèi)數(shù)據(jù)個(gè)數(shù)相同的二進(jìn)制編碼,與之匹配的位為1,其余為0。例如,CAM中有8個(gè)數(shù)據(jù),輸入的數(shù)據(jù)與第3個(gè)數(shù)匹配,則輸出00100000。

3.2 三態(tài)模式

標(biāo)準(zhǔn)三態(tài)模式是指寫入CAM的內(nèi)容可以為1,O和X,X是指不關(guān)心的位,任何值與X比較的結(jié)果都是認(rèn)為是匹配的,比如與10X1匹配的內(nèi)容為1011,1001。增強(qiáng)三態(tài)模式比標(biāo)準(zhǔn)模式多了一個(gè)U,U和X剛好相反,指的是任何值與U比較的結(jié)果都是認(rèn)為是不匹配的。

經(jīng)過(guò)對(duì)CAM核的分析,三態(tài)模式中X的引入可以實(shí)現(xiàn)一對(duì)多的匹配,這樣CAM中的一個(gè)值不但可以對(duì)應(yīng)容差范圍內(nèi)的多個(gè)值,也可以對(duì)應(yīng)參數(shù)捷變雷達(dá)的中參數(shù)的多個(gè)值。例如,雷達(dá)的頻率參數(shù)范圍是01111100b≤RF≤01111111b,CAM中只要預(yù)存二進(jìn)制數(shù)011111XX就可以實(shí)現(xiàn)。利用這個(gè)原理,本文使用Active-HDL 8.2軟件在FPGA中實(shí)現(xiàn)了預(yù)分選器的設(shè)計(jì)。

對(duì)CAM和RAM單元的初始化數(shù)據(jù)寫入既可預(yù)先初始化,也可在系統(tǒng)工作過(guò)程中實(shí)時(shí)更新。在雷達(dá)信號(hào)預(yù)分選應(yīng)用中可將已知輻射源庫(kù)利用初始化內(nèi)存文件對(duì)CAM和RAM進(jìn)行初始化。對(duì)未知輻射源參數(shù)可在系統(tǒng)工作過(guò)程中實(shí)時(shí)動(dòng)態(tài)寫入。

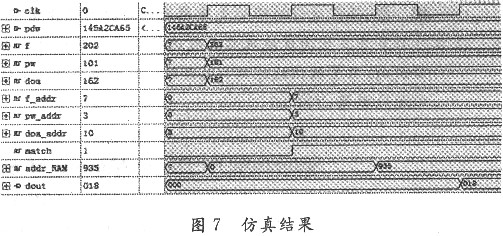

圖7為在Active-HDL8.2中的仿真圖,從輸入的PDW可以得到PW=101,DOA=162,RF=202,三個(gè)參數(shù)分別進(jìn)入相應(yīng)的CAM中得到匹配結(jié)果和匹配標(biāo)志,最終得到與編號(hào)為18的雷達(dá)匹配。

4 結(jié)語(yǔ)

基于CAM的關(guān)聯(lián)比較器在雷達(dá)信號(hào)預(yù)分選中具有重要意義,能夠極大地提高信號(hào)分選的速度,為后端處理節(jié)省更多的時(shí)間。本系統(tǒng)在FPGA內(nèi)設(shè)計(jì)了基于CAM的關(guān)聯(lián)比較器,實(shí)現(xiàn)了雷達(dá)信號(hào)的快速預(yù)分選,達(dá)到了實(shí)時(shí)性和可靠性的要求。