1、引言

在對(duì)采樣率為44.1kHz的AAC音頻進(jìn)行解碼時(shí),一幀的解碼時(shí)間須控制在23.22毫秒內(nèi)。且音頻中每一幀可包含1"48個(gè)聲道的數(shù)據(jù),若遇時(shí)序要求最嚴(yán)格的場(chǎng)合,即一幀包含48個(gè)聲道數(shù)據(jù),實(shí)時(shí)性則很難滿足,因此速度便成為硬件設(shè)計(jì)的重要指標(biāo)。所以在系統(tǒng)設(shè)計(jì)時(shí),為完成解碼的實(shí)時(shí)性要求,各模塊應(yīng)以速度為優(yōu)化目標(biāo)。

在AAC音頻解碼" title="AAC音頻解碼">AAC音頻解碼電路的設(shè)計(jì)中,需要一塊電路連接AAC比特流的存儲(chǔ)電路和和取數(shù)解碼電路,考慮到它須完成數(shù)據(jù)緩沖和移位的功能,我們選擇用移位寄存器" title="移位寄存器">移位寄存器來(lái)實(shí)現(xiàn),示意圖如下。

圖1 移位寄存器功能示意圖

典型的移位寄存器有兩個(gè)特點(diǎn):1)每個(gè)時(shí)鐘周期移一位,2)加載的優(yōu)先級(jí)別高于移位的優(yōu)先級(jí)別,移位需等待加載的完成。而AAC音頻數(shù)據(jù)采用變長(zhǎng)編碼技術(shù),即壓縮比特流中的數(shù)據(jù)部分為可變長(zhǎng)的哈夫曼編碼,所以每次解碼完畢從移位寄存器中移出的位數(shù)不是固定值,若使用典型移位寄存器一位一位地移數(shù)據(jù)降低了工作效率;且每次移位須等待加載完畢進(jìn)行,耗費(fèi)了等待時(shí)間。所以,典型的移位寄存器在時(shí)序要求緊張的場(chǎng)合對(duì)速度提高起到了負(fù)面作用,導(dǎo)致整個(gè)系統(tǒng)不能完成實(shí)時(shí)性要求。因此本設(shè)計(jì)針對(duì)AAC音頻解碼這一特殊應(yīng)用,對(duì)典型移位寄存器在速度方面進(jìn)行改進(jìn)設(shè)計(jì),使之每一周期可移出任意位,且移位無(wú)須等待加載完成,從而加速了移位過(guò)程,使之滿足實(shí)時(shí)性要求。

論文結(jié)構(gòu)如下:首先介紹本設(shè)計(jì)的工作原理,對(duì)其中一些參數(shù)進(jìn)行配置;其次分模塊進(jìn)行電路設(shè)計(jì);再次,將典型移位寄存器和本設(shè)計(jì)分別下載到FPGA開(kāi)發(fā)板,從速度和面積兩方面進(jìn)行實(shí)驗(yàn)結(jié)果的比較;最后,對(duì)設(shè)計(jì)展望,提出可優(yōu)化的方向。

2、工作原理

考慮到本設(shè)計(jì)的特定使用場(chǎng)合,選擇移位寄存器為64位,移位位數(shù)是1"16可變的整數(shù),存儲(chǔ)空間是位寬為32位的fifo。在其他場(chǎng)合下,可基于同樣的設(shè)計(jì)方法通過(guò)改變參數(shù)來(lái)滿足要求。

移位寄存器功能示意如圖1所示,此移位寄存器連接了兩塊電路單元:?jiǎn)卧弧⑿枰?shù)的AAC音頻解碼電路單元;單元二、數(shù)據(jù)的存儲(chǔ)空間。當(dāng)任意時(shí)刻單元一需取數(shù)時(shí),可向移位寄存器發(fā)出取數(shù)信號(hào),并給出要取的位數(shù),移位寄存器就在一個(gè)周期內(nèi)將所需長(zhǎng)度的數(shù)據(jù)移出。當(dāng)移位寄存器中的數(shù)據(jù)少于一定量時(shí)(在此設(shè)為32位),會(huì)自動(dòng)從單元二中加載數(shù)據(jù),且加載與移位同優(yōu)先級(jí)別,所以無(wú)須等待時(shí)間。

3、位數(shù)可選、自動(dòng)加載移位寄存器電路設(shè)計(jì)

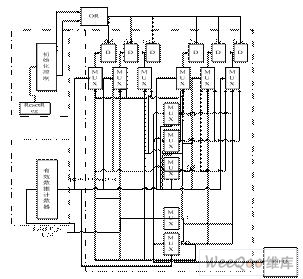

以主要寄存器的不同功能依據(jù),將電路劃分為如下圖所示的虛線框內(nèi)的三個(gè)模塊。下面將分模塊介紹電路的設(shè)計(jì)。

圖2 位數(shù)可選、自動(dòng)加載移位寄存器電路圖

3.1 有效數(shù)據(jù)計(jì)數(shù)器的設(shè)計(jì)

有效數(shù)據(jù)計(jì)數(shù)器是用來(lái)記錄移位寄存器中剩余有效數(shù)據(jù)的位數(shù)。初始化時(shí),存儲(chǔ)器向移位寄存器加載64位有效數(shù)據(jù),計(jì)數(shù)器為64;當(dāng)外界從移位寄存器取數(shù)時(shí),計(jì)數(shù)器在原有計(jì)數(shù)的基礎(chǔ)上減掉所取的位數(shù);當(dāng)移位寄存器從存儲(chǔ)器加載數(shù)據(jù)時(shí),計(jì)數(shù)器在原有計(jì)數(shù)的基礎(chǔ)上加上加載數(shù)據(jù)的位寬(32);當(dāng)移位和加載同時(shí)進(jìn)行時(shí),計(jì)數(shù)器進(jìn)行上述的減法和加法的混合運(yùn)算。

使用計(jì)數(shù)器的目的是為了產(chǎn)生加載數(shù)據(jù)的標(biāo)志信號(hào)(在這里設(shè)為32)。當(dāng)有效數(shù)據(jù)計(jì)數(shù)器中的數(shù)目小于等于32時(shí),產(chǎn)生加載信號(hào),而當(dāng)計(jì)數(shù)器中的數(shù)目大于32時(shí),撤除加載信號(hào)。在這里加載數(shù)據(jù)的標(biāo)志位可以是范圍為16"32的整數(shù),范圍的制定決定于:加載標(biāo)志的下限要滿足一次取數(shù)的最大長(zhǎng)度,上限要保證除有效數(shù)據(jù)外的剩余空間足夠下一次的數(shù)據(jù)加載長(zhǎng)度。

3.2 初始化控制狀態(tài)機(jī)的設(shè)計(jì)

移位寄存器在電路復(fù)位時(shí)須加載上有效數(shù)據(jù),以保證第一次的取數(shù)的正確進(jìn)行。而此時(shí)加載標(biāo)志不能由有效數(shù)據(jù)計(jì)數(shù)器產(chǎn)生,因?yàn)橛行?shù)據(jù)計(jì)數(shù)器在初始化的狀態(tài)下為64不可能產(chǎn)生加載標(biāo)志,所以加載標(biāo)志需由復(fù)位信號(hào)間接產(chǎn)生。且由于移位寄存器的長(zhǎng)度(64位)是存儲(chǔ)器的寬度(32位)的2倍,所以需要加載兩次。

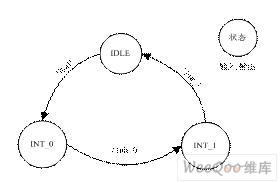

鑒于以上的功能要求,設(shè)計(jì)初始化狀態(tài)機(jī),其中包括三個(gè)狀態(tài): IDLE, INIT_0和 INIT_1。當(dāng)復(fù)位產(chǎn)生時(shí),復(fù)位信號(hào)的兩級(jí)寄存信號(hào)(防止亞穩(wěn)態(tài))為觸發(fā)信號(hào),使?fàn)顟B(tài)由IDLE跳轉(zhuǎn)到INIT_0;下一個(gè)時(shí)鐘周期,狀態(tài)機(jī)自動(dòng)由INIT_0跳轉(zhuǎn)到INIT_1,并產(chǎn)生輸出信號(hào)init_0;再下個(gè)時(shí)鐘周期,狀態(tài)機(jī)自動(dòng)由INIT_1跳轉(zhuǎn)到IDLE,并產(chǎn)生輸出信號(hào)init_1。狀態(tài)機(jī)產(chǎn)生的上述兩個(gè)輸出信號(hào)控制產(chǎn)生移位寄存器在初始化時(shí)的兩次加載信號(hào)。狀態(tài)轉(zhuǎn)換圖如下:

圖3 移位寄存器初始化狀態(tài)轉(zhuǎn)移圖

3.3 移位寄存器的設(shè)計(jì)

之所以選擇64位的移位寄存器,是因?yàn)槿暨x擇一倍于存儲(chǔ)器寬度的移位寄存器長(zhǎng)度(32位),移位后剩余的有效數(shù)據(jù)的位數(shù)可能不夠下一次的移位長(zhǎng)度,為滿足移位長(zhǎng)度的要求,需要在加載后再次移位,因此移位最多要花費(fèi)三個(gè)時(shí)鐘周期的時(shí)間;若選擇三倍于存儲(chǔ)器寬度的移位寄存器的長(zhǎng)度或更長(zhǎng)(>=96位)時(shí),當(dāng)設(shè)定加載數(shù)據(jù)的標(biāo)志為有效數(shù)據(jù)不大于32時(shí),需要加載兩次數(shù)據(jù),當(dāng)設(shè)定加載數(shù)據(jù)的標(biāo)志為有效數(shù)據(jù)不大于64時(shí),此時(shí)移位寄存器中的有效數(shù)據(jù)相對(duì)于需要移位的最長(zhǎng)數(shù)據(jù)偏長(zhǎng)且沒(méi)有必要。所以,將移位寄存器的長(zhǎng)度選擇為2倍于存儲(chǔ)器的寬度(64位)在時(shí)間和空間上都達(dá)到了最優(yōu)。

初始化過(guò)程:初始化狀態(tài)機(jī)產(chǎn)生的輸出信號(hào)init_0和init_1為兩次加載的控制信號(hào),這兩個(gè)信號(hào)控制移位寄存器在初始化的兩個(gè)時(shí)鐘周期內(nèi),從存儲(chǔ)器中取出數(shù)據(jù)并將其分別加載到高32位和低32位。

移位過(guò)程:當(dāng)取數(shù)信號(hào)發(fā)出取數(shù)要求時(shí),輸入的取數(shù)位數(shù)作為多路選擇器的數(shù)據(jù)選擇端,當(dāng)前移位寄存器的值和0作為多路選擇器的數(shù)據(jù)端,通過(guò)數(shù)據(jù)選擇決定移位寄存器下個(gè)周期從高位到低位的值。

加載過(guò)程:當(dāng)加載信號(hào)發(fā)出時(shí),剩余有效數(shù)據(jù)作為多路選擇器的數(shù)據(jù)選擇端,當(dāng)前移位寄存器的值、FIFO輸出的值和0作為多路選擇器的數(shù)據(jù)端,通過(guò)數(shù)據(jù)選擇決定移位寄存器下個(gè)周期從高位到低位的值。

移位和加載同時(shí)發(fā)生的過(guò)程:當(dāng)移位和加載信號(hào)同時(shí)產(chǎn)生時(shí),移位寄存器中剩余的有效數(shù)據(jù)的位數(shù)和輸入的取數(shù)位數(shù)共同作為多路選擇器的數(shù)據(jù)選擇端,當(dāng)前移位寄存器的值、FIFO輸出的值和0作為多路選擇器的數(shù)據(jù)端,通過(guò)數(shù)據(jù)選擇決定移位寄存器下個(gè)周期從高位到低位的值。

4、實(shí)驗(yàn)結(jié)果

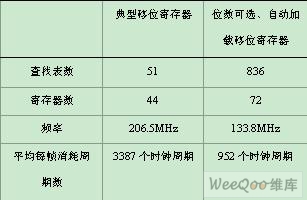

為完成解碼實(shí)時(shí)性的要求,本設(shè)計(jì)對(duì)典型的移位寄存器在速度上進(jìn)行改進(jìn),但控制邏輯變得復(fù)雜,從而消耗了更多資源。因此,我們選擇速度、面積作為性能指標(biāo)對(duì)兩種設(shè)計(jì)進(jìn)行比較。在基于FPGA的硬件設(shè)計(jì)中,面積指標(biāo)通常用查找表數(shù)和寄存器數(shù)來(lái)表示,速度指標(biāo)我們選擇最大時(shí)鐘頻率及解碼時(shí)平均每幀消耗的周期數(shù)來(lái)表示。

我們采用altera公司FPGA開(kāi)發(fā)工具QuartusII分別對(duì)兩塊電路進(jìn)行綜合和時(shí)序分析,從綜合報(bào)告中獲得查找表和寄存器的數(shù)目,從時(shí)序報(bào)告中獲得最大時(shí)鐘頻率。并將兩個(gè)設(shè)計(jì)分別同AAC音頻解碼電路一起整體下載到stratix II EP2S180 的FPGA開(kāi)發(fā)板,以AAC音頻壓縮文件中隨機(jī)抽取的10幀數(shù)據(jù)為測(cè)試矢量,使用一計(jì)數(shù)器記錄下移位寄存器消耗的周期數(shù),將其寫(xiě)入片內(nèi)ram,并將觀測(cè)到的數(shù)據(jù)通過(guò)計(jì)算得平均每幀消耗的周期數(shù)。實(shí)驗(yàn)結(jié)果如下表所示:

表1 實(shí)驗(yàn)數(shù)據(jù)對(duì)比

由對(duì)比數(shù)據(jù)可得以下結(jié)論:

1、典型移位寄存器的工作頻率大于位數(shù)可選、自動(dòng)加載移位寄存器的頻率。但由于此移位寄存器只是更大電路中的一個(gè)小模塊,由實(shí)際結(jié)果可知電路整體的工作頻率并不取決于此模塊的工作頻率,所以在整體電路中對(duì)單獨(dú)模塊的頻率進(jìn)行比較并不能得出速度的優(yōu)劣。

2、由查找表數(shù)和寄存器數(shù)的比較可得:典型移位寄存器消耗的資源遠(yuǎn)小于位數(shù)可選、自動(dòng)加載移位寄存器,即典型移位寄存器在面積上占有較大優(yōu)勢(shì)。

3、由平均每幀消耗周期數(shù)的比較可得:兩者工作在相同的時(shí)鐘頻率下時(shí),位數(shù)可選、自動(dòng)加載移位寄存器消耗的時(shí)間約為典型移位寄存器的28%,單位時(shí)間內(nèi)傳輸?shù)臄?shù)據(jù)量提高到典型移位寄存器的356%,所以位數(shù)可選、自動(dòng)加載移位寄存器在速度上占有較大優(yōu)勢(shì)。

綜上,為完成AAC音頻解碼的實(shí)時(shí)性要求,本設(shè)計(jì)進(jìn)行了速度和面積上的折中處理,相對(duì)于典型移位寄存器本設(shè)計(jì)以犧牲面積為代價(jià)換取了速度上的優(yōu)勢(shì),使之在規(guī)定時(shí)間內(nèi)完成解碼。