目前國內(nèi)數(shù)控機床中的伺服電機一般都是配套增量式編碼器,而增量式編碼器的精度并不太高且輸出的是并行信號,欲提高其精度就必然要增大編碼器的設(shè)計難度和增多并行信號的輸出,這樣就不利于伺服單元與編碼器的長距離通信,而采用絕對式編碼器,除了其精度比增量式編碼器高幾倍以外,其信號的輸入輸出都采用高速串行通信,節(jié)省了通信線路便于長距離的通信,在編碼器的另一端,采用CPLD與絕對式編碼器進(jìn)行高速串行通信,CPLD再把收到的編碼器信息轉(zhuǎn)變?yōu)椴⑿袛?shù)據(jù)傳送給伺服單元中的DSP進(jìn)行運算控制,本文將給出CPLD與絕對式編碼器高速串行通信的軟硬件設(shè)計方案。

硬件設(shè)計

硬件主要由電源、CPLD及其外圍電路和絕對式編碼器接口電路三個模塊組成。

電源模塊

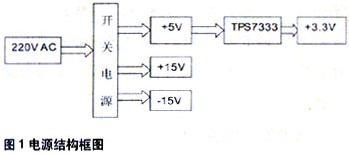

電源模塊由開關(guān)電源電路和DC/DC電源芯片組成,如圖1所示。

圖中的開關(guān)電源將220V交流電網(wǎng)電壓轉(zhuǎn)變成+5V,+15V,-15V,開關(guān)電源可濾除電網(wǎng)中存在的各種干擾,并且開關(guān)電源中的變壓器將220V AC與輸出的+5V,+15V,-15V隔離開,內(nèi)部電路還采用了TL431調(diào)節(jié)開關(guān)管的導(dǎo)通脈沖寬度,因此開關(guān)電源的抗干擾、安全性、穩(wěn)定性及穩(wěn)壓程度都比較好,TPS7333是DC/DC芯片,它將+5V的直流電壓轉(zhuǎn)變成+3.3V的穩(wěn)定直流電壓供給CPLD使用,TPS7333轉(zhuǎn)換效率、可靠性和穩(wěn)壓性都比較好,它在輸入電壓為+3.77V-+10V的電壓范圍內(nèi)都能轉(zhuǎn)換出+3.3V,使CPLD不受輸入電壓過高導(dǎo)致其燒壞。

CPLD及其外圍電路模塊

CPLD及其外圍電路模塊主要由CPLD、CPLD編程下載接口電路(JTAG接口),DSP接口電路、有源晶振、電平轉(zhuǎn)換電路和ADM485及其外圍電路(負(fù)責(zé)與編碼器通信的接口電路)組成(圖2)。

本設(shè)計CPLD采用Altera公司的EPM570T144C5,此芯片屬于Altera公司的MAX II,MAX II相對MAX I成本更加低,功耗更加小,而器件的宏單元數(shù)更加多,且器件延時控制在6ns以內(nèi),具有很高的性價比,EPM570T144C5有570個宏單元數(shù),芯片的引腳數(shù)目為144個,其中可用的I/O口有116個,因此此芯片的資源已經(jīng)足夠用。CPLD主要負(fù)責(zé)與絕對式編碼器的高速串行通信,并受控于DSP的命令把接收到編碼器數(shù)據(jù)和其他信息并行的轉(zhuǎn)送給DSP。

JTAG接口主要用于下載可執(zhí)行文件到CPLD,在PC機安裝Altera公司的開發(fā)環(huán)境-QUARTUS II,并在此開發(fā)環(huán)境中將編寫好的VHDL程序進(jìn)行編譯,保證編譯不出錯并且保證功能已實現(xiàn)后,連接好下載電纜到JTAG接口,通過QUARTUS II提供的編程下載工具,對CPLD電路板進(jìn)行下載。

DSP接口就是由8根數(shù)據(jù)線,3根地址線和1根控制線組成的,8根數(shù)據(jù)線負(fù)責(zé)轉(zhuǎn)送編碼器數(shù)據(jù)及其其他信息,3根地址線負(fù)責(zé)傳送DSP命令,在CPLD終端進(jìn)行譯碼,CPLD根據(jù)譯碼得出的命令將編碼器數(shù)據(jù)或其他信息通過8根數(shù)據(jù)線傳送到DSP,控制線主要是完成CPLD與DSP同步控制。

20M有源晶振主要是為CPLD提供基準(zhǔn)時鐘,在時鐘信號的驅(qū)動下,供CPLD產(chǎn)生2.5Mb/s的波特率與編碼器進(jìn)行通信,和產(chǎn)生10M赫茲時鐘供一些邏輯控制信號使用,此晶振提供20M赫茲的時鐘頻率,需要電源提供3.3V的直流電壓。

電平轉(zhuǎn)換電路主要負(fù)責(zé)將3.3V電壓轉(zhuǎn)換成5V或?qū)?V電壓轉(zhuǎn)換成3.3V,因為CPLD的核和I/O口需要的供電電壓都是3.3V,而ADM485和絕對式編碼器所需的供電電壓和I/O口驅(qū)動電路都為5V,所以需要用電平轉(zhuǎn)換芯片LVC4245A將3.3V轉(zhuǎn)換成5V電壓或?qū)?V轉(zhuǎn)換成3.3V。

ADM485及其外圍電路是CPLD與絕對式編碼器高速通信的硬件銜接。ADM485工作電壓為5V,其最大通信速率為5Mb/s,采用2個ADM485芯片進(jìn)行對接通信可提高通信線路上的抗干擾能力,最長的傳輸距離可達(dá)1.2km。其外圍電路如圖3所示,虛線的右半部屬于絕對式編碼器的外圍電路,上拉和下拉電阻都是1K歐姆,限流電阻則是220歐姆,ADM485的SDAT是數(shù)據(jù)輸出引腳,ADM485是SRQ是數(shù)據(jù)輸入引腳,ADM485的DE是外部控制引腳,該腳受CPLD控制,由于RS-485通信協(xié)議屬于半雙工,所以ADM485只能處在發(fā)送數(shù)據(jù)或接收數(shù)據(jù)的狀態(tài),當(dāng)ADM485得DE為高電平時,ADM485處于數(shù)據(jù)輸出狀態(tài)(即CPLD接收數(shù)據(jù)),當(dāng)ADM485的DE為低電平時,ADM485處于數(shù)據(jù)輸入狀態(tài)(即CPLD發(fā)送數(shù)據(jù))。

絕對式編碼器接口模塊

絕對式編碼器接口模塊是指絕對式編碼器內(nèi)部的電源及信號輸入輸出接口電路,其電路與上述的ADM485及其外圍電路是一致的,同樣是采用ADM485芯片及一些上拉、下拉及限流電阻,如圖3所示,虛線的左半部就是絕對式編碼器內(nèi)部接口電路,它負(fù)責(zé)與外部ADM485(虛線的右半部)銜接,ADM485受編碼器內(nèi)部的控制芯片所控制,當(dāng)編碼器受到CPLD發(fā)來的命令之后,控制芯片做出判斷后發(fā)送出相應(yīng)的數(shù)據(jù),同時控制ADM485的DE為高電平,即使ADM485處于發(fā)送狀態(tài),當(dāng)發(fā)送完數(shù)據(jù)之后,控制芯片又使ADM485的DE處于低電平狀態(tài),便于隨時接收CPLD發(fā)來的命令。

軟件設(shè)計

軟件是指CPLD的VHDL程序,其主要由分頻器、接收DSP控制命令、CPLD邏輯控制、波特率發(fā)生器、接收及發(fā)送數(shù)據(jù)和串并轉(zhuǎn)換及發(fā)送數(shù)據(jù)六個軟件子模塊組成(圖4)。

- 分頻器模塊

分頻器模塊主要是把20M赫茲的輸入時鐘頻率分頻為10M赫茲和2.5M赫茲的時鐘頻率,其中10M赫茲時鐘主要是供給CPLD邏輯控制模塊工作,2.5M赫茲時鐘主要是供給波特率發(fā)生器模塊工作。

- 接收DSP控制命令模塊

接收DSP控制命令模塊實際上是實時的采集DSP發(fā)來的控制信號并及時的將控制信號進(jìn)行譯碼,譯碼完成后立即轉(zhuǎn)送給CPLD邏輯控制模塊。

- CPLD邏輯控制模塊

CPLD邏輯控制模塊是整個CPLD軟件的核心,其接收到譯碼數(shù)據(jù)后,立即作出邏輯控制運算,并快速的控制接收及發(fā)送數(shù)據(jù)模塊和控制串行轉(zhuǎn)換及發(fā)送數(shù)據(jù)模塊。

- 波特率發(fā)生器模塊

波特率發(fā)生器模塊主要是為接收及發(fā)送數(shù)據(jù)模塊提供2.5Mb/s波特率。

- 接收及發(fā)送數(shù)據(jù)模塊

接收及發(fā)送數(shù)據(jù)模塊是整個CPLD軟件的重要組成部分,其主要負(fù)責(zé)與絕對式編碼器高速通信,由于其通信方式是異步串行通信方式,因此其波特率、通信的數(shù)據(jù)格式及RS-485通信協(xié)議都要與絕對式編碼器相同。

- 串并轉(zhuǎn)換及發(fā)送數(shù)據(jù)模塊

串并轉(zhuǎn)換及發(fā)送數(shù)據(jù)模塊主要是將接收到的編碼器串行數(shù)據(jù)轉(zhuǎn)換成并行數(shù)據(jù),并將數(shù)據(jù)鎖存在CPLD鎖存器內(nèi),當(dāng)CPLD邏輯控制模塊控制其發(fā)送數(shù)據(jù)時,就將鎖存在CPLD鎖存器內(nèi)的數(shù)據(jù)以并行的方式放送給DSP,供DSP進(jìn)行運算控制用。

結(jié)語

本設(shè)計已經(jīng)完成了硬件及軟件的全部設(shè)計,讀取帶有絕對式編碼器的電動機轉(zhuǎn)子的任何一個位置數(shù)據(jù)只需31μs,通信速率可達(dá)2.5Mb/s,將本設(shè)計集成在伺服驅(qū)動單元中,驅(qū)動和控制電動機轉(zhuǎn)數(shù)可達(dá)6000轉(zhuǎn)/分,控制電動機轉(zhuǎn)子的位置精度可達(dá)μM級。