現(xiàn)場可編程門陣列(FPGA,F(xiàn)ield Programmable Gate Array)是一種高密度可編程邏輯器件,其邏輯功能是通過把設(shè)計生成的數(shù)據(jù)文件配置進芯片內(nèi)部的靜態(tài)配置數(shù)據(jù)存儲器(SRAM )來實現(xiàn)的,具有可重復(fù)編程性,可以靈活實現(xiàn)各種邏輯功能。由于FPGA器件采用的是SRAM 工藝,在斷電的情況下FPGA內(nèi)的配置數(shù)據(jù)將丟失。所以,在典型的采用FPGA器件的電子系統(tǒng)中通常將FPGA 的配置數(shù)據(jù)存放于其兼容的SPROM 中,上電時由控制電路將SPROM中的配置數(shù)據(jù)裝入FPGA器件中。但是通常的SPROM價格昂貴,且是一次性,不利于FPGA程序的更新,所以有必要分析FPGA 的配置原理,采用廉價、能重復(fù)使用的方式配置FPGA。

本文主要根據(jù)Altera公司手冊及以前的經(jīng)驗,設(shè)計和完成了一種新的FPGA配置文件下載更新的方法。其主要原理是在每次啟動系統(tǒng)時,由配置控制器從Flash中讀出FPGA配置文件,再下載到FPGA中以完成器件的配置功能。當系統(tǒng)需要升級更新FPGA配置文件時,可通過網(wǎng)絡(luò)或者由主機通過JTAG(Joint Test Action Group)接口(未聯(lián)網(wǎng)時)將配置文件發(fā)送給基于Nios II處理器的嵌入式系統(tǒng)中,由Nios II處理器更新系統(tǒng)中的Flash。當Flash內(nèi)容更新后,系統(tǒng)就可實現(xiàn)在加電時由配置控制器自動將配置文件下載到FPGA中。而配置控制器是采用復(fù)雜可編程邏輯器件(CPLD,Complex Programmable Logic Device),主要功能是實現(xiàn)并串轉(zhuǎn)換。這樣在不需要任何硬件動作和專業(yè)軟件的情況下,只需要進行常規(guī)軟件操作就可以更新FPGA的配置文件。不僅節(jié)約了成本,還有效地縮小了系統(tǒng)體積,有利于以后系統(tǒng)工程的升級更新。

1 基于Nios II的嵌入式系統(tǒng)簡介

Nios II是Altera公司在第一代軟核處理器Nios的基礎(chǔ)上于2004年5月為其FPGA產(chǎn)品配套開發(fā)的軟核CPU。Nios II是一種采用流水線技術(shù)、單指令流的基于RISC技術(shù)的通用嵌入式軟核處理器、哈佛體系結(jié)構(gòu),地址、數(shù)據(jù)、指令均為32位,最高性能可達到200DMIPS (Dhrystones MIPS)。Nios II系統(tǒng)中的外設(shè)具有可配置性,用戶可根據(jù)實際應(yīng)用來裁剪,并且Nios II處理器有很好的自定義指令支持,大部分指令均可以在一個時鐘周期內(nèi)完成,這也是可配置處理器的優(yōu)勢所在。Nios II在邏輯功能上是32位的精簡指令集CPU;而在實現(xiàn)方式上,它是在FPGA上通過編程方式實現(xiàn)的,這也是與傳統(tǒng)的CPU一個根本差別。Nios II的總線方式也采用了一種簡單的總線體系結(jié)構(gòu)——Avalon總線。該軟核CPU為可編程片上系統(tǒng)SOPC給用戶提供了一套綜合解決方案,它可以與用戶自定義邏輯結(jié)合構(gòu)成SOC系統(tǒng),并下載到Altera的FPGA 芯片中,使得FPGA在嵌入式系統(tǒng)領(lǐng)域的地位越來越重要。

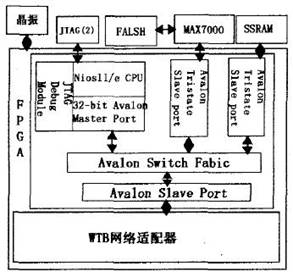

基于Nios II的嵌入式系統(tǒng)主要實現(xiàn)了絞線式列車總線(WTB,Wire Train Bus) 網(wǎng)絡(luò)節(jié)點機的功能,該系統(tǒng)是基于SOPC技術(shù),首先定制Nios II的嵌入式CPU、必要的外部和相關(guān)配置的芯片,然后按照WTB標準和Nios II特有的Avalon總線接口設(shè)計并通過VHDL實現(xiàn)MAU的功能,由Nios II來控制WTB網(wǎng)絡(luò)通信功能。基于Nios II嵌入式軟核WTB網(wǎng)絡(luò)節(jié)點機硬件體系結(jié)構(gòu)主要由FPGA、Flash nemory、SSRAM Memory、MAX7000配置控制器等硬件組成。FPGA 采用Altera公司的Cyclone系列的EP1C6Q240C8,使用Altera公司的MAX7000系列的EPM7256配置控制器完成對EP1C6Q240C8的配置,基于Nios II的嵌入式系統(tǒng)的原理圖如圖1所示。

其中圖中的JTAG2表明有2個JTAG接口,一個用來在線配置調(diào)試,一個用來下載更新配置文件。

2 FPGA 器件的配置方式

FPGA的配置方式分為主動方式(AS,Active Serial)、被動方式(PS,Passive Serial)和JTAG方式,數(shù)據(jù)寬度有8位并行方式和串行方式兩種。在主動模式下,F(xiàn)PGA在上電后,由PLD器件引導(dǎo)配置操作過程,它控制著外部存儲器和初始化過程,自動將配置數(shù)據(jù)從相應(yīng)的外存儲器讀入到SRAM 中,實現(xiàn)內(nèi)部結(jié)構(gòu)映射;而在被動模式下,F(xiàn)PGA則作為從屬器件,由相應(yīng)的控制電路或微處理器提供配置所需的時序,實現(xiàn)配置數(shù)據(jù)的下載。

下面對基于ICR(In-Circuit Reconfigurability)FPGA器件的配置方式進行詳細分析:

(1) 主動串行方式(AS,Active Serial):主要使用EPC配置器件,適應(yīng)用低速設(shè)備的配置;

(2) 被動串行方式(PS,Passive Seria1):使用配置控制器的串行接口;

(3) 被動并行同步方式(PPS,Passive Parallel Synchronous):使用配置控制器的并行同步接口;

(4) 被動并行異步方式(PPA,Passive Parallel Asynchronous):使用配置控制器的并行異步接口;

(5) 邊界掃描方式(JTAG,Joint Test Action Group):使用JTAG下載電纜。

基于AS方式配置使用EPC配置器件進行配置時,首先將配置文件從計算機下載到EPC配置器件中去,然后由EPC配置器件控制配置時序?qū)PGA進行配置。EPC配置器件有一次可編程和可擦寫編程型兩種:一次可編程型芯片只能寫入一次,不適于開發(fā)階段反復(fù)調(diào)試、修改及產(chǎn)品的方便升級;可擦除編程型價格昂貴,且容量有限,對于容量較大的可編程邏輯器件,需要多片配置芯片組成菊花鏈進行配置,增加了系統(tǒng)設(shè)計的難度。

使用PS、PPS、PPA方式配置時,配置文件事先是以二進制形式保存在系統(tǒng)ROM 中,然后通過配置控制器將配置數(shù)據(jù)送進FPGA中。PS是通過串行方式送到FPGA中,PPS是以并行方式送給FPGA。FPGA在其內(nèi)部將并行數(shù)據(jù)轉(zhuǎn)換成串行數(shù)據(jù),該數(shù)據(jù)轉(zhuǎn)換時需要外部配置時鐘的驅(qū)動。比較PS和PPS,所用的配置時間幾乎相同,而PS的接口方式比較簡單,所以嵌入式系統(tǒng)中通常選擇PS方式配置FPGA。使用PPA方式配置數(shù)據(jù)時,配置控制器將配置數(shù)據(jù)以并行方式送給FPGA,然后在FPGA內(nèi)部進行數(shù)據(jù)串行化處理。與PPS不一樣的地方是串行化處理時不需要配置外部時鐘的驅(qū)動,但接口更復(fù)雜,工程中很少使用。

邊界掃描方式需要連接計算機,無法在現(xiàn)場使用,嵌入式系統(tǒng)中很少采用這種方式。

通過上述的分析,在嵌入式系統(tǒng)中要使用FPGA時,可以采用專用EPC配置器件、PS、PPS、PPA和CPLD配置器件,但是PS、PPS、PPA比專用EPC配置更具成本和體積優(yōu)勢。在PS、PPS、PPA中,PS又是最優(yōu)的通信方式。所以在嵌入式系統(tǒng)中,選擇利用CPLD配置器件的PS被動串行方式來配置FPGA最為合適。

而本文正是利用CPLD配置控制器基于PS方式進行FPGA配置的新方法,在每次啟動系統(tǒng)時,由配置控制器從Flash中讀出FPGA配置文件的數(shù)據(jù)信息,再下載到FPGA中以完成器件的配置功能。當系統(tǒng)需要升級更新FPGA配置文件時,可通過網(wǎng)絡(luò)或者由主機通過JTAG接口(未聯(lián)網(wǎng)時)將配置文件發(fā)送給基于Nios II處理器的嵌入式系統(tǒng)中,由Nios II處理器更新系統(tǒng)中的Flash。當Flash內(nèi)容更新后,系統(tǒng)就可實現(xiàn)在加電時由CPLD配置控制器自動將配置文件下載到FPGA中。這樣在不需要任何硬件動作和專業(yè)軟件的情況下,只需要進行常規(guī)軟件操作就可以更新FPGA的配置文件。CPLD配置控制器主要是在配置FPGA時將FLASH存放的配置文件中的并行數(shù)據(jù)轉(zhuǎn)化為串行數(shù)據(jù),實現(xiàn)系統(tǒng)的加電自運行。

3 嵌入式系統(tǒng)中FPGA 的配置電路設(shè)計

3.1 PS方式配置時序

在嵌入式系統(tǒng)中,配置控制器可以產(chǎn)生配置時序,能夠和FPGA直接通信,將FLASH 中的配置文件傳輸?shù)紽PGA 的SRAM 中去。通常使用PS被動串行方式進行配置FPGA,下面就通信中使用到的5根信號線的配置時序進行說明。

5根信號線分別為nCONFIG、nSTATUS、CONF_DONE、DCLK、DATA,連接配置控制器的5個I/O 口和對應(yīng)的FPGA的引腳,配置時序圖如圖2所示。

圖2 PS方式配置信號時序圖

配置控制器上的5個I/O端口連接上述5個信號線。其中連接nCONFIG、DCLK、DATA端口設(shè)置成輸出態(tài),nSTATUS、CONF_DONE端口設(shè)置成輸入態(tài)。當配置控制器開始與FPGA通信時,配置控制器首先在nCONFIG上送出一個大于8 um的負脈沖,并且檢測nSTATUS 上的信號。當FPGA 接收到nCONFIG上的下降沿時,迅速將nSTATUS和CONF_DONE拉低,并且保持低電平信號一直到nCONFIG抬高電平。當nCONFIG上抬高電平后過1 um,nSTATUS也將電平抬高,配置控制器檢測到nSTATUS上的變化后認為FPGA 已經(jīng)做好了接收數(shù)據(jù)的準備。下一步配置控制器將產(chǎn)生配置時鐘脈沖,配置時鐘的第一個上升沿至少要比nSTATUS上升沿晚1 um。又由于配置數(shù)據(jù)和配置時鐘上升沿同步,所以在配置時鐘上升沿發(fā)生之前,數(shù)據(jù)線必須已經(jīng)有了配置數(shù)據(jù)信號。配置數(shù)據(jù)是按照低位在前高位在后的順序把數(shù)據(jù)送上數(shù)據(jù)線。當所有數(shù)據(jù)都傳輸完畢后,CONF_DONE線上電平被抬高以示配置完畢。如果傳輸中出現(xiàn)了異常,F(xiàn)PGA迫使nSTATUS拉低電平,配置控制器一旦檢測到了這種現(xiàn)象將重新開始配置。由于配置文件中已經(jīng)包含了FPGA初始化的一些代碼,所以傳輸完配置文件后,F(xiàn)PGA就可以正常工作了。

3.2 基于CPLD配置控制器的配置電路設(shè)計

CPLD是一種用戶根據(jù)各自需要而自行構(gòu)造邏輯功能的數(shù)字集成電路。其基本設(shè)計方法是借助Quartus II開發(fā)軟件平臺,通過JTAG下載電纜將代碼傳送到目標芯片中,實現(xiàn)系統(tǒng)配置所需的時序要求和功能需求。而更重要的是CPLD配置控制器可以進行上萬次的燒寫操作。

嵌入式系統(tǒng)中FPGA 的PS方式配置方式電路設(shè)計如圖3所示。FPGA和FLASH、SSRAM組成了一個最基本的嵌入式系統(tǒng),其中將Nios II軟核處理器嵌入到FPGA中。FLASH 作為程序的存儲器,其中存儲著系統(tǒng)的整個軟件應(yīng)用程序和配置文件。SSAM作為系統(tǒng)程序運行空間,可以有效地解決配置控制器自身SRAM容量小的問題。

圖3 PS方式配置方式電路設(shè)計

在圖3所示的設(shè)計中,MSEL0和MSEL1是配置專用線,如果MSEL0接高電平(VCC),MSEL1接地(GND),則此時的配置模式為PS模式; 如果MSELO 和MSEL1都接地(GND),則配置模式為AS模式。CPLD控制器的控制信號MAX_control_signal主要包括flash_CS_n (片選)、flash_OE_n (輸出使能)、flash_RW_n (讀寫使能)、flash_RESET_n(重置)、flash_BYTE_n (字節(jié)傳輸)等信號線。

配置文件通過Altera的Quartus II軟件以.pof(Programmer Object Files)文件格式下載到EPM7256配置控制器內(nèi),如果配置有錯誤,該配置控制器可以進行多次下載,直至最終完成配置功能。

FLASH中存儲的程序包括系統(tǒng)配置程序文件、軟件程序,其格式為.flash。系統(tǒng)加電后,配置控制器從FLASH 的0地址開始將配置文件進行并/串轉(zhuǎn)換后(即將圖3中的flash_DATA[7..0]轉(zhuǎn)換為DATA0)加載到FPGA中,完成系統(tǒng)加電時的自動配置功能;同時Nios II處理器將FLASH 中的應(yīng)用程序移至到SSRAM 中運行,從而實現(xiàn)嵌入式系統(tǒng)的初運行。通過Nios II IDE工具可以將配置文件FPGA 的.sof文件格式轉(zhuǎn)換為Flash存儲器所需要的. flash文件格式。

4 配置文件的設(shè)計與實現(xiàn)

為了確保配置過程的正確,提高系統(tǒng)的配置性能,在配置文件設(shè)計時應(yīng)嚴格按照FPGA的Ps配置流程進行,并在配置過程中始終監(jiān)控配置工作狀態(tài),在完善的配置程序配合下可以糾正如上電次序?qū)е屡渲貌徽5儒e誤。該配置程序是采用VHDL語言編寫的,編寫完成后,將配置文通過JTAG接口下載到EPM7256配置控制器內(nèi),根據(jù)圖2的PS配置時序,其配置流程如下:

(1)配置信號的初始化:DATAO=0,DCLK=0,nCONFIG=0,CONF_DONE=1和nSTATUS=1,并保持2 us以上。

(2)檢測nSTATUS,如果為“0”,表明FPGA 已響應(yīng)配置,可開始進行配置,否則報錯,并返回1。正常情況下,nCONFIG=0后1 us內(nèi)nSTATUS為“0”。

(3)置nCONFIG=1,并延時5 us。

(4)DATAO上放置數(shù)據(jù)(低位在前),DCLK=1,延時。

(5)DCLK=0,并檢測nSTATUS,若為“0”,則報錯,重返1。

(6)準備下一位數(shù)據(jù),并重新執(zhí)行(4)、(5),直到數(shù)據(jù)發(fā)送完為止。

(7)此時CONF_DONE應(yīng)變成“1”,表明FPGA已完成配置,如果數(shù)據(jù)發(fā)送完后,CONF_DONE為“0”,必須重新配置返回1。

(8)配置完成后,再送出299個周期(Cyclone要求的)的DCLK,以便FPGA完成初始化。

5 結(jié)束語

本文介紹了通過用CPLD 的MAX7000 系列配置控制器EPM7256和Flash實現(xiàn)Cyclone系列的EP1C6Q240C8 FPGA配置文件下載更新的方法。與傳統(tǒng)的JTAG或PROM 串行下載配置方法相比,此方法具有更新配置文件靈活方便、易于操作、更加有利于系統(tǒng)配置文件的升級等特點。與常用的串行配置方法相比,該配置方法更具有配置時間短,準確率高、易于實現(xiàn)等優(yōu)點。雖然該配置控制電路是為配置Altera公司cyclone系列的FPGA器件而設(shè)計的,但稍加修改也適用于其它系列的。FPGA器件,故其有一定的通用性,采用此方法特別適用于需要不斷更新的系統(tǒng)設(shè)計中,具有較為廣闊的應(yīng)用前景。