卷積碼是一種性能優(yōu)良的差錯控制編碼。本文闡述了卷積碼編解碼器的基本工作原理,在MAX+PLUS2軟件平臺上,給出了利用復雜可編程邏輯器件設計的(2,1,6)卷積碼編解碼器電路,并進行了編譯和波形仿真。

綜合后下載到復雜可編程邏輯器件EPM7128SLC84-15中,測試結果表明,達到了預期的設計要求。

數(shù)字通信系統(tǒng)進行數(shù)據(jù)傳輸時,由于噪聲干擾的影響,不可避免地會在接收端產(chǎn)生差錯。為了在已知信噪比的情況下達到一定的誤碼率指標,在合理設計基帶信號,選擇調制、解調方式,并采用均衡措施的基礎上,還應采用差錯控制編碼等信道編碼技術來降低誤碼率。分組碼和卷積碼是差錯控制編碼的兩種主要形式,在編碼器復雜程度相同的情況下,卷積碼的性能優(yōu)于分組碼,因此,在諸如GSM、IS95和CDMA2000等無線通信標準中,都應用了卷積碼。

CPLD是復雜可編程邏輯器件的簡稱,它是20世紀90年代初期出現(xiàn)的高密度可編程邏輯器件,采用E2CMOS工藝制作,一般由三種可編程電路組成,即可編程邏輯宏單元,可編程輸入/輸出單元和可編程內部連線。它可利用EDA技術中的MAX+PLUS2作為開發(fā)工具,將設計的電路圖或硬件描述語言編寫的程序綜合成網(wǎng)表文件寫入其中,制成ASIC芯片。CPLD的突出優(yōu)點是可反復編程,集成度非常高,數(shù)據(jù)速率快,同時具有較大的靈活性。

1、卷積碼編碼器

卷積碼(又稱連環(huán)碼),是由伊萊亞斯(P.Elis)提出的一種非分組碼。它把k比特信息段編成n比特的碼組,該碼組不僅同當前的k比特信息段有關,而且還同前面的(N-1)個信息段有關聯(lián)(N為大于1的整數(shù))。通常,把卷積碼記作(n,k,N),其中k為輸入碼元數(shù),n為輸出碼元數(shù),N為約束長度,表示編碼器的存儲器級數(shù)。卷積編碼屬于信道編碼,主要用來糾正碼元的隨機差錯,它是以犧牲效率來換取可靠性,利用增加監(jiān)督位,進行檢錯和糾錯。

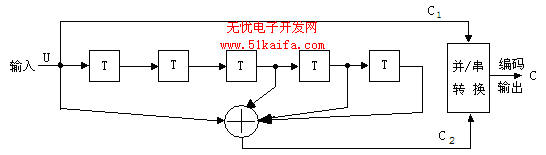

卷積碼編碼器是一個由k個輸入端、n個輸出端,且具有(N-1)節(jié)移位寄存器構成的有限狀態(tài)記憶系統(tǒng),通常稱為時序網(wǎng)絡。卷積碼的編碼方法有三種運算方式:離散卷積法、生成矩陣法和多項式乘積法。此外,卷積碼的編碼過程還可以用狀態(tài)圖、碼樹圖和網(wǎng)格圖來描述。本文設計的編碼器原理圖如圖1所示,它為(2,1,6)卷積碼編碼器(圖中T為移位寄存器)。

|

|

圖1 卷積碼編碼器原理圖 |

由圖1可知,該編碼器是一個(2,1,6)卷積編碼器,即k=1(一個輸入端)、n=2(兩個輸出端)、N=6(5級移位寄存器)。

若輸入信息序列為:U=(u0 u1 u2 …),則對應輸出為兩個碼字序列:

C1=(c0(1)c1(1)c2(1)…) C2=(c0(2)c1(2)c2(2)…)

其相應編碼方程可寫為:C1 = U * G(1) C2 = U * G(2)

式中“*”表示卷積運算,G(1)和G(2)表示編碼器的兩個沖激響應。編碼輸出可由輸入信息序列U和編碼器的兩個脈沖沖激響應的卷積得到,故稱卷積碼。由于編碼器有5級寄存器,所以沖激響應至多可持續(xù)到6位,圖1所示卷積碼編碼器的兩個沖激響應可寫成:

G(1)=(100000) G(2)=(100111)

若輸入信息序列為:U=(11010101),則:

C1=(11010101)*(100000)=(1101010100000)

C2=(11010101)*(100111)=(1100010001011)

經(jīng)過并串轉換,最后輸出的碼字為:C=(11110010001100100001000101)

2、卷積碼解碼器

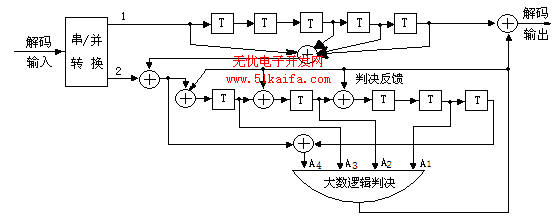

卷積碼的解碼可分為代數(shù)解碼和概率解碼兩類。大數(shù)邏輯解碼器是代數(shù)解碼最主要的解碼方法,它即可用于糾正隨機錯誤,又可用于糾正突發(fā)錯誤,但要求卷積碼是自正交碼或可正交碼,對于(2,1,6)卷積碼大數(shù)邏輯解碼器原理圖如圖2所示。

|

|

圖2 (2,1,6)卷積碼大數(shù)邏輯解碼器原理圖 |

圖2中,輸入的數(shù)字序列,經(jīng)串/并轉換為兩路,1路輸出信息碼元,2路輸出校驗碼元。解碼器把接收到的1路中的每一段信息元送入編碼器求出本地校驗元,與其后面收到的校驗元模2加。若兩者一致,則求出的伴隨式分量為0,否則為1。把加得的值送入伴隨式寄存器中寄存。當接收完碼段后開始對第0碼段糾錯,若此時大數(shù)邏輯門的輸出為1,則說明第0碼段的信息元有錯。這時正好第0子組的信息元移至解碼器的輸出端,從而糾正它們。同時,糾錯信號也反饋至伴隨式寄存器修正伴隨式,以消去此錯誤對伴隨式的影響。如果大數(shù)判決門沒有輸出,則說明第0子組的信息元沒有錯誤,這時從編碼器中直接把信息元輸出。

3、利用CPLD實現(xiàn)的卷積碼編解碼器

3.1 利用CPLD實現(xiàn)的(2,1,6)卷積碼編碼器

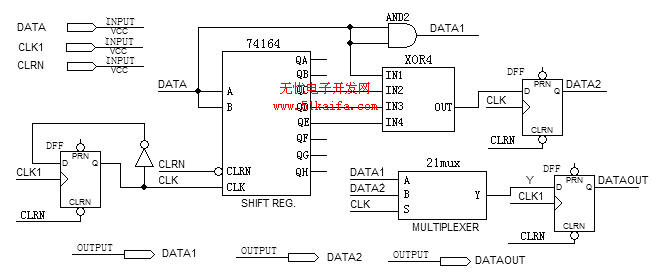

基于CPLD設計的(2,1,6)卷積碼編碼器電路如圖3所示。

|

|

圖3 基于CPLD設計的(2,1,6)卷積碼編碼器電路 |

圖3所示卷積編碼器的引腳關系為:引腳DATA表示數(shù)據(jù)輸入,引腳CLK1表示“并串轉換”輸入時鐘,引腳CLK表示數(shù)據(jù)時鐘輸入引腳(它可由CLK1二分頻得到),引腳DATA1表示卷積編

碼器輸出碼C1的數(shù)據(jù),引腳DATA2表示卷積編碼器輸出碼C2的數(shù)據(jù)。引腳DATAOUT表示卷積編碼器經(jīng)過并串轉換,最后輸出的碼C的數(shù)據(jù)。

5級移位寄存器從MAX+PLUS2器件庫中調用一個串入并出移位寄存器74164實現(xiàn);4級模2加從MAX+PLUS2器件庫中調用一個4級異或門“XOR4”組成;“21mux”實現(xiàn)2位并串轉換;編碼器的兩個輸出碼和并串轉換后的輸出碼之后各增加了一個D觸發(fā)器“DFF”,其作用是利用D觸發(fā)器的輸入端對毛刺信號不敏感的特點,去處CPLD器件輸出引腳上可能產(chǎn)生的毛刺。

3.2 利用CPLD設計(2,1,6)卷積碼解碼器

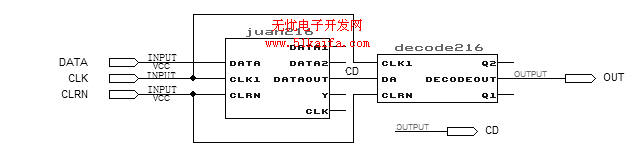

基于CPLD設計的(2,1,6)卷積碼大數(shù)邏輯解碼器如圖4所示。

|

|

圖4 基于CPLD設計的(2,1,6)卷積碼大數(shù)邏輯解碼器 |

(2,1,6)卷積碼大數(shù)邏輯解碼器由2位串/并轉換電路,監(jiān)督碼產(chǎn)生電路,校正子計算電路和大數(shù)邏輯電路組成。

2位串/并轉換“chuanbing12”是從MAX+PLUS2器件庫中調用4個D觸發(fā)器“DFF”,2個非門設計成一個二分頻電路和一個一輸入二輸出串/并轉換電路并進行元件包裝入庫而形成,其中時鐘CLK由CLK1二分頻得到。

監(jiān)督碼產(chǎn)生電路是從MAX+PLUS2器件庫中調用一個串入并出移位寄存器74164,一個4級異或門“XOR4”組成。

校正子計算電路是從MAX+PLUS2器件庫中調用5個D觸發(fā)器“DFF”,4個異或門“XOR”設計組成電路。

大數(shù)邏輯電路是從MAX+PLUS2器件庫中調用4個與非門“NAND3”,1個與非門“NAND4”和1個異或門“XOR”設計組成電路。

3.3 利用CPLD設計(2,1,6)卷積碼編解碼器

將設計的(2,1,6)卷積碼編碼器進行元件包裝入庫為“juan216”,將設計的(2,1,6)卷積碼解碼器進行元件包裝入庫為“decode216”,之后將它們連接在一起,可組成的(2,1,6)卷積碼編解碼器如圖5所示。

|

|

圖5 (2,1,6)卷積碼編解碼器 |

(2,1,6)卷積碼編解碼器的引腳關系為:引腳DATA表示數(shù)據(jù)輸入,引腳CLK表示輸入時鐘(其速率是數(shù)據(jù)速率的二倍),引腳CLRN表示清零端,引腳CD表示(2,1,6)卷積碼編碼器輸出,引腳OUT表示(2,1,6)卷積碼解碼器輸出。

4、實驗結果

利用MAX+PLUS2開發(fā)工具進行編譯和仿真,(2,1,6)卷積碼編解碼器仿真波形如圖5所示。

|

|

圖6 (2,1,6)卷積碼編解碼器仿真波形 |

其中“DATA”是數(shù)據(jù)輸入端,系統(tǒng)輸入的數(shù)據(jù)比特若為“11010101”,經(jīng)卷積碼編碼器后,延時約150ns后“CD”輸出的數(shù)據(jù)比特為“11110010001100100001000101”;再經(jīng)卷積碼解碼器,延時約1us后“OUT”恢復輸出數(shù)據(jù)比特為“11010101”。仿真結果表明:編碼器輸出數(shù)據(jù)與理論計算完全一致。然后將綜合后生成的網(wǎng)表文件通過ByteBlaste下載電纜,以在線配置的方式下載到CPLD器件EPM7128SLC84-15中,從而完成了器件的編程。上電后,在輸入端加入待編碼信息,用數(shù)字存儲示波器測試編碼器輸出,實測結果完全正確,達到了設計要求。

5 結論

本文闡述了卷積碼編解碼器的工作原理,利用CPLD器件,設計出了(2,1,6)卷積碼編解碼器。本文作者創(chuàng)新點是利用了EDA技術中的MAX+PLUS2作為開發(fā)工具,將設計的電路圖綜合成網(wǎng)表文件寫入其中,制成ASIC芯片,突出優(yōu)點是可反復編程,集成度非常高,數(shù)據(jù)速率快,自頂向下設計,查找和修改錯誤方便,同時先仿真,正確后再下載測試并應用,因而具有較大的靈活性;根據(jù)本文提出的設計思路,可方便的設計其它卷積碼編解碼器,有廣闊的應用前景。

[參 考 文 獻]

[1]謝平,陳建輝,胡記文.基于CPLD的模數(shù)轉換組合研究[J].微計算機信息,2005,26:153-155.

[2]龍光利.CDMA手機卷積碼編碼器的設計與FPGA的實現(xiàn)[J].陜西工學院學報,2005,21(2):1-3.

[3]王新梅,肖國強.糾錯碼——原理與方法.修訂版[M].西安:西安電子科技大學出版社,2001.

[4]趙曙光,郭萬有,楊頌華.可編程邏輯器件原理、開發(fā)與應用[M].西安:西安電子科技大學出版社,2001.

[5]樊昌信,張甫翊,徐炳祥等.通信原理.第五版[M].北京:國防工業(yè)出版社,2002.

[6]閻石.數(shù)字電子技術基礎[M].第四版.北京:高等教育出版社,1999.