摘 要: 介紹一種基于CPLD" title="CPLD">CPLD的多普勒聲納" title="多普勒聲納">多普勒聲納回波信號(hào)仿真卡的設(shè)計(jì)實(shí)現(xiàn),該板卡作為PXI測(cè)試系統(tǒng)的一個(gè)組成模塊,數(shù)據(jù)交換基于PXI總線" title="PXI總線">PXI總線,使用S5920" title="S5920">S5920實(shí)現(xiàn)總線控制,利用CPLD實(shí)現(xiàn)板卡的時(shí)序邏輯控制,外圍電路包括信號(hào)調(diào)理與匹配電路、DDS電路、A/D采集電路、高速FIFO" title="FIFO">FIFO存儲(chǔ)電路、D/A轉(zhuǎn)換電路等。重點(diǎn)介紹了CPLD內(nèi)部功能模塊的實(shí)現(xiàn)。該設(shè)計(jì)已成功應(yīng)用于多普勒聲納的PXI測(cè)試系統(tǒng)中。

關(guān)鍵詞: 多普勒聲納;PXI總線;S5920;CPLD;FIFO

水下航行器可利用聲波信號(hào)的多普勒效應(yīng)進(jìn)行導(dǎo)航,多普勒聲納按一定的角度向海底發(fā)射聲波,利用回波信號(hào)的多普勒頻移測(cè)得航行器相對(duì)于海底的速度,然后通過(guò)對(duì)地速的積分結(jié)合航向信息就可以獲得導(dǎo)航解[1]。在水下航行器的研制、生產(chǎn)、實(shí)驗(yàn)、驗(yàn)收等環(huán)節(jié)中,經(jīng)常需要對(duì)導(dǎo)航聲納的性能參數(shù)進(jìn)行測(cè)試,若進(jìn)行實(shí)物的水下航行實(shí)驗(yàn),不僅會(huì)花費(fèi)大量的人力、物力和財(cái)力,而且實(shí)時(shí)參數(shù)的獲取也有一定的困難。本文提出一種利用模塊化的PXI總線測(cè)試平臺(tái)對(duì)水下航行器導(dǎo)航系統(tǒng)進(jìn)行測(cè)試的解決方案,使得對(duì)導(dǎo)航系統(tǒng)的測(cè)試可以在陸上實(shí)驗(yàn)室完成。測(cè)試平臺(tái)大部分由成熟的通用測(cè)試模塊構(gòu)成,其中對(duì)回波信號(hào)多普勒效應(yīng)的模擬是整個(gè)系統(tǒng)設(shè)計(jì)的關(guān)鍵環(huán)節(jié),本文通過(guò)設(shè)計(jì)專門的多普勒聲納回波信號(hào)仿真卡實(shí)現(xiàn)[2]。

1 仿真卡的組成與工作原理

1.1 仿真卡組成

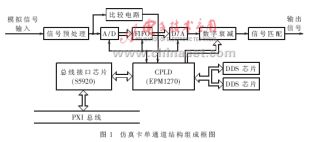

仿真卡主要由總線接口芯片、CPLD、門限比較電路、DDS(直接數(shù)字頻率合成)電路、A/D采集電路、FIFO存儲(chǔ)電路、D/A 轉(zhuǎn)換電路以及輸入輸出端的信號(hào)調(diào)理與匹配電路等組成。導(dǎo)航系統(tǒng)包括4個(gè)安裝在航行器底部的多普勒聲納,因此仿真卡有4個(gè)相對(duì)獨(dú)立的工作通道,分別模擬多普勒聲納4個(gè)不同方向的回波信號(hào),其中一個(gè)通道的結(jié)構(gòu)組成如圖1所示。

1.2 工作原理

總線接口芯片S5920實(shí)現(xiàn)仿真卡與PXI測(cè)試系統(tǒng)的橋接,可簡(jiǎn)化接口部分的設(shè)計(jì)。CPLD實(shí)現(xiàn)仿真卡的總體時(shí)序邏輯控制。對(duì)接換能器輸出的模擬信號(hào)在板卡上經(jīng)信號(hào)預(yù)處理電路后分為兩路,一路信號(hào)送A/D采集電路,另一路信號(hào)進(jìn)入門限比較電路。當(dāng)多普勒聲納發(fā)射信號(hào)時(shí),對(duì)接換能器對(duì)應(yīng)有模擬信號(hào)輸出,門限比較電路會(huì)產(chǎn)生一個(gè)觸發(fā)信號(hào)送CPLD,CPLD啟動(dòng)仿真卡的數(shù)據(jù)采集過(guò)程。數(shù)據(jù)采集與回波信號(hào)模擬的時(shí)序邏輯如圖2所示,t1為發(fā)射信號(hào)周期,T為發(fā)射脈沖寬度,采集數(shù)據(jù)同時(shí)存入4路FIFO存儲(chǔ)器,經(jīng)過(guò)t2時(shí)間的延遲后由CPLD控制讀取4路FIFO中的數(shù)據(jù)并進(jìn)行D/A轉(zhuǎn)換,然后經(jīng)數(shù)字衰減電路和信號(hào)匹配電路后由對(duì)接換能器發(fā)射出去。若聲速為c,則該回波信號(hào)模擬的是傳播距離為m=ct2/2的回波信號(hào),T′為回波信號(hào)的脈沖寬度。

DDS芯片產(chǎn)生A/D采集芯片、FIFO芯片以及D/A轉(zhuǎn)換芯片的工作時(shí)鐘,CPLD通過(guò)程控DDS產(chǎn)生不同的工作時(shí)鐘信號(hào),使得D/A轉(zhuǎn)換時(shí)鐘不同于A/D采集時(shí)鐘,從而實(shí)現(xiàn)采集數(shù)據(jù)在時(shí)間上的拉伸與壓縮,模擬回波信號(hào)的多普勒效應(yīng)。真實(shí)回波信號(hào)在信道中傳輸后會(huì)有不同程度的衰減,因此D/A轉(zhuǎn)換后的數(shù)據(jù)需經(jīng)數(shù)字衰減電路進(jìn)行程控衰減。信號(hào)預(yù)處理電路和信號(hào)匹配電路的核心都是一級(jí)射隨電路。板卡上共有5片DDS,產(chǎn)生5路時(shí)鐘信號(hào),DDS0時(shí)鐘作為A/D采集時(shí)A/D芯片和FIFO芯片的工作時(shí)鐘,另4路時(shí)鐘DDS1~DDS4作為D/A轉(zhuǎn)換時(shí)FIFO芯片和D/A芯片的工作時(shí)鐘,DDS芯片和數(shù)字衰減器需經(jīng)CPLD配置參數(shù)才能正常運(yùn)行。

2 主要功能模塊硬件設(shè)計(jì)

功能仿真卡硬件設(shè)計(jì)要滿足以下指標(biāo):

(1)板卡作為PXI測(cè)試系統(tǒng)的一個(gè)模塊,與PXI主機(jī)的數(shù)據(jù)交換基于PXI總線;

(2)系統(tǒng)運(yùn)行的邏輯控制和部分芯片的配置功能由CPLD[3]完成;

(3)板卡數(shù)據(jù)采集系統(tǒng)的時(shí)鐘由程控的DDS產(chǎn)生,數(shù)據(jù)采集頻率10MHz~40MHz;

(4)采集數(shù)據(jù)的存儲(chǔ)采用高速大容量的FIFO存儲(chǔ)器實(shí)現(xiàn),存儲(chǔ)深度為1MB;

(5)A/D采集和D/A轉(zhuǎn)換采用8bit芯片,工作頻率≥40MHz[4]。

PXI總線是在PCI局部總線的基礎(chǔ)上增加了用于多板同步的觸發(fā)總線和參考時(shí)鐘而成的,PXI是PCI總線的一種擴(kuò)展總線,因此完全兼容PCI總線的規(guī)范協(xié)議。利用成熟的PCI模塊,通過(guò)軟件兼容性設(shè)計(jì)與修改,就可以完成PXI系統(tǒng)的設(shè)計(jì)與開發(fā)。由于PCI總線協(xié)議的邏輯時(shí)序比較復(fù)雜,這里采用PCI總線接口芯片S5920來(lái)實(shí)現(xiàn)接口功能[5]。S5920內(nèi)部配置寄存器的定義信息存儲(chǔ)在外接的EEPROM芯片AT24C02中,系統(tǒng)上電時(shí)由操作系統(tǒng)的配置軟件讀取。

CPLD是整個(gè)仿真卡的主控模塊,根據(jù)S5920提供的控制信息,控制實(shí)現(xiàn)各部分電路的時(shí)序邏輯功能。CPLD采用Altera公司MAX II系列的EPM1270芯片。MAX II CPLD采用類似于FPGA的全新架構(gòu),與傳統(tǒng)的CPLD相比,可以提供給用戶更多的邏輯資源,更多的用戶I/O,同時(shí)具有更低的功耗。

DDS采用AD公司的AD9850芯片。AD9850內(nèi)部包含高性能的D/A轉(zhuǎn)換器和高速比較器,通過(guò)設(shè)置32bit的頻率控制字,可產(chǎn)生0~40MHz的穩(wěn)定方波信號(hào)。射隨電路采用低噪聲、高精度運(yùn)算放大器OP37。門限比較電路采用低偏置電壓的四路比較器LM339,參考電壓由外部基準(zhǔn)源ADR510提供。AD采集部分由寬頻帶電流反饋運(yùn)放OPA681和8bit精度A/D轉(zhuǎn)換芯片ADS831組成,ADS831采用內(nèi)置參考電壓,單極性輸入信號(hào),輸入電壓信號(hào)范圍為1.5V~3.5V。FIFO存儲(chǔ)器采用IDT公司512KB的IDT72V2113,為實(shí)現(xiàn)1MB的存儲(chǔ)深度,IDT72V2113設(shè)置成512K×9bit工作方式,并采用兩片進(jìn)行級(jí)聯(lián)。AD9709和高速運(yùn)放AD843構(gòu)成D/A轉(zhuǎn)換電路,AD9709是一種雙通道8位D/A轉(zhuǎn)換器,因此4個(gè)轉(zhuǎn)換通道只需要兩片AD9709。程控衰減電路采用AD7111N和OP37構(gòu)成的典型應(yīng)用電路,通過(guò)鎖存一個(gè)字節(jié)的配置數(shù)據(jù),AD7111N可以實(shí)現(xiàn)0~88.5dB的程控衰減,衰減步長(zhǎng)為0.375dB。

3 CPLD功能實(shí)現(xiàn)

CPLD模塊的設(shè)計(jì)是整個(gè)仿真卡的核心,其要實(shí)現(xiàn)的功能包括:(1)接口功能。能夠?qū)崿F(xiàn)CPLD與PCI橋芯片S5920的數(shù)據(jù)通信,并鎖存所預(yù)設(shè)的參數(shù);(2)根據(jù)主機(jī)設(shè)定的參數(shù),正確配置5片DDS和4片數(shù)字衰減器;(3)初始化各外圍芯片,運(yùn)行過(guò)程中控制其運(yùn)行狀態(tài),必要時(shí)可重新復(fù)位;(4)根據(jù)外部觸發(fā)信號(hào)啟動(dòng)A/D采集,并按照預(yù)設(shè)參數(shù)值適時(shí)啟動(dòng)D/A轉(zhuǎn)換過(guò)程。

CPLD的開發(fā)工具采用Altera公司提供的集成開發(fā)工具Quartus II 5.1[6]。設(shè)計(jì)方法采用VHDL和原理圖的混合設(shè)計(jì)。CPLD控制器的內(nèi)部功能實(shí)現(xiàn)較為復(fù)雜,模塊之間的邏輯聯(lián)系較多,下面僅以接口功能模塊、配置模塊和邏輯控制模塊三個(gè)主要部分來(lái)介紹CPLD的內(nèi)部功能實(shí)現(xiàn)。

3.1 接口功能模塊

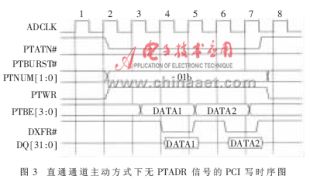

接口模塊的功能主要是使CPLD能夠正確接收主機(jī)的控制和數(shù)據(jù)信息,并對(duì)數(shù)據(jù)進(jìn)行鎖存。S5920將PCI總線信號(hào)轉(zhuǎn)換成相對(duì)簡(jiǎn)單的外加總線(ADD_ON_BUS)信號(hào),根據(jù)S5920的不同數(shù)據(jù)傳輸方式,外加總線信號(hào)也分為直通通道引腳和郵箱通道引腳兩大類。這里采用直通通道傳輸方式,圖3為直通通道主動(dòng)操作方式下不使用PTADR#信號(hào)的PCI寫時(shí)序圖。PTATN信號(hào)低電平有效表示一個(gè)PCI總線周期正在進(jìn)行;PTBURST信號(hào)無(wú)效表示未用猝發(fā)傳送方式,而是單周期方式;PTNUM是直通通道的通道號(hào);PTWR信號(hào)有效表示是進(jìn)行寫操作;PTBE是直通通道的字節(jié)允許標(biāo)志,指示32位雙字中的哪個(gè)字節(jié)有效;DXFR為主動(dòng)方式傳送完畢信號(hào),其為低電平時(shí)表示有數(shù)據(jù)正在傳送,因此接口模塊是在DXFR低電平的時(shí)鐘上跳沿時(shí)鎖存數(shù)據(jù)。

數(shù)據(jù)傳送采用16位總線方式,低8位是數(shù)據(jù),高8位是地址信息,接口模塊在接收到16位信息后直接對(duì)地址譯碼后將數(shù)據(jù)鎖存入存儲(chǔ)區(qū)中的相應(yīng)地址。這些數(shù)據(jù)信息包括系統(tǒng)的運(yùn)行參數(shù)、DDS與數(shù)字衰減器的配置數(shù)據(jù)以及主機(jī)控制板卡工作狀態(tài)的控制信息。同時(shí)接口模塊還要提供外加總線的時(shí)鐘信號(hào)ADCLK作為S5920的工作時(shí)鐘。

3.2 配置模塊

系統(tǒng)在啟動(dòng)或復(fù)位后,需要對(duì)DDS和數(shù)字衰減器進(jìn)行配置,配置數(shù)據(jù)由主機(jī)寫入接口模塊進(jìn)行鎖存。由于DDS與數(shù)字衰減器的配置過(guò)程類似,這里以相對(duì)復(fù)雜的DDS配置過(guò)程為例說(shuō)明相應(yīng)功能的CPLD實(shí)現(xiàn)。

AD9850的配置可采用并行或串行配置方式,這里采用并行方式,配置時(shí)序如圖4所示。40bit的配置數(shù)據(jù)分成5個(gè)字節(jié),第一個(gè)字節(jié)是相位調(diào)制和電源功能信息,后4個(gè)字節(jié)是頻率控制字。配置前先由RESET信號(hào)對(duì)芯片復(fù)位,5個(gè)字節(jié)的配置數(shù)據(jù)在W_CLK的上升沿寫入AD9850,F(xiàn)Q_UD是配置結(jié)束信號(hào),AD9850在FQ_UD的上跳沿刷新輸出頻率。

CPLD內(nèi)部的DDS配置模塊的頂層原理圖文件如圖5所示。主要包括一個(gè)配置邏輯產(chǎn)生模塊dds_cfg、6bit計(jì)數(shù)器lpm_counter0和一個(gè)T觸發(fā)器lpm_tff1。5片DDS共用一個(gè)dds_reset信號(hào),圖中6位計(jì)數(shù)器lpm_count0作為地址發(fā)生器,dds_cfg模塊根據(jù)不同的地址信息讀取配置數(shù)據(jù)并產(chǎn)生如圖5所示的配置邏輯信號(hào)。計(jì)數(shù)器使能的有效信號(hào)由預(yù)設(shè)參數(shù)結(jié)束后的啟動(dòng)信號(hào)begin產(chǎn)生,配置完成后的cnt_clken信號(hào)使計(jì)數(shù)器使能信號(hào)變低,使整個(gè)配置模塊停止工作,從而完成配置過(guò)程。

3.3 邏輯控制模塊

CPLD的控制功能主要由邏輯控制模塊實(shí)現(xiàn),控制模塊的主要功能示意圖如圖6。4片F(xiàn)IFO的讀空信號(hào)(FIFO_OR)取邏輯與后經(jīng)脈沖同步產(chǎn)生一個(gè)脈沖復(fù)位信號(hào),這里取與的目的是取最后讀空的FIFO讀空標(biāo)志,同時(shí)主機(jī)的控制信號(hào)經(jīng)或門也可以對(duì)系統(tǒng)進(jìn)行復(fù)位。這樣每個(gè)工作周期系統(tǒng)便自動(dòng)復(fù)位,而主機(jī)也可以隨時(shí)對(duì)仿真卡進(jìn)行復(fù)位。外部觸發(fā)信號(hào)與主機(jī)的控制信號(hào)取與后作為計(jì)數(shù)器的時(shí)鐘使能信號(hào)。比較器將計(jì)數(shù)器的計(jì)數(shù)值與上位機(jī)的預(yù)設(shè)參數(shù)相比較,當(dāng)計(jì)數(shù)到預(yù)設(shè)值后產(chǎn)生相應(yīng)的控制信號(hào)送時(shí)鐘控制模塊。時(shí)鐘控制模塊主要是根據(jù)計(jì)數(shù)比較結(jié)果、FIFO讀空信號(hào)以及外部觸發(fā)信號(hào)控制A/D、D/A和FIFO芯片的工作時(shí)鐘,以控制各外圍電路的工作,同時(shí)時(shí)鐘控制模塊還對(duì)DDS產(chǎn)生的時(shí)鐘信號(hào)進(jìn)行必要的整形或反相,以滿足外圍電路正常工作的時(shí)序要求。

4 CPLD內(nèi)部設(shè)計(jì)仿真與板卡調(diào)試

CPLD內(nèi)部設(shè)計(jì)的功能仿真和時(shí)序仿真都通過(guò)Quartus II集成的仿真工具進(jìn)行。由于時(shí)序仿真包含了布局布線后的延時(shí)信息,能夠真實(shí)地反映芯片的工作情況。時(shí)序仿真前,需要編輯完整的測(cè)試激勵(lì)文件,設(shè)置正確的時(shí)序約束參數(shù),如設(shè)置具有一定裕量的時(shí)鐘周期、時(shí)鐘建立時(shí)間、時(shí)鐘保持時(shí)間等,剪除非相關(guān)時(shí)鐘域中的時(shí)序路徑,并將內(nèi)部非時(shí)鐘路徑的T觸發(fā)器輸入端管腳設(shè)置為非時(shí)鐘等。最終時(shí)序仿真的結(jié)果完全能夠滿足設(shè)計(jì)的功能要求與時(shí)序要求。

由于在Windows XP系統(tǒng)中應(yīng)用程序無(wú)法直接對(duì)硬件端口進(jìn)行操作,因此需要編寫專用的驅(qū)動(dòng)程序。這里采用目前應(yīng)用廣泛的WinDriver開發(fā)工具,利用它的向?qū)Чぞ撸恍枰钊肓私獠僮飨到y(tǒng)的整個(gè)內(nèi)核體系結(jié)構(gòu),就可以開發(fā)出高質(zhì)量的驅(qū)動(dòng)程序,應(yīng)用程序采用Visual C++開發(fā)。將仿真卡在整個(gè)PXI測(cè)試系統(tǒng)中進(jìn)行調(diào)試,發(fā)現(xiàn)該板卡能夠完全滿足最初的設(shè)計(jì)要求,且運(yùn)行穩(wěn)定可靠。

基于CPLD多普勒聲納回波信號(hào)仿真卡的研制,滿足了設(shè)計(jì)指標(biāo)要求,特別是CPLD的應(yīng)用使得整個(gè)板卡具有結(jié)構(gòu)簡(jiǎn)單、成本低、可靠性高等優(yōu)點(diǎn)。該仿真卡現(xiàn)在已成功應(yīng)用于對(duì)某水下航行器多普勒導(dǎo)航聲納進(jìn)行陸上檢測(cè)的PXI測(cè)試系統(tǒng)中,并取得了良好的效果。

參考文獻(xiàn)

[1] 李俊,沈安文.基于多普勒速度聲納的水下航行器導(dǎo)航方法[J].華中科技大學(xué)學(xué)報(bào),2004,(1):73-75.

[2] 謝志剛,陳自力.PXI總線數(shù)字輸入/輸出模塊的設(shè)計(jì)與實(shí)現(xiàn)[J].電子技術(shù)應(yīng)用,2005,(2):67-69.

[3] MAX II Device Handbook Data Sheet.2004,4.

[4] 王立欣,劉雙寶.基于PCI總線的100MSps,256MBit數(shù)據(jù)采集系統(tǒng)[J].哈爾濱工業(yè)大學(xué)學(xué)報(bào),2005,(2):246-248.

[5] AMCC S5920 32-Bit PCI Bus Target Interface Data Sheet.1998,10.

[6] 王誠(chéng),吳繼華.Altera FPGA/CPLD設(shè)計(jì)(基礎(chǔ)篇、高級(jí)篇)[M].北京:人民郵電出版社,2005.