1 引言

數(shù)控機(jī)床的加T精度主要南位置檢測系統(tǒng)的精度決定,位置檢測系統(tǒng)一般包括傳感器(旋轉(zhuǎn)變壓器,光電編碼器,光柵)、四倍頻鑒相電路、計數(shù)電路等,系統(tǒng)通過這些檢測電機(jī)的位移和速度,發(fā)出反饋信號,從而構(gòu)成閉環(huán)或半閉環(huán)控制。形成差值控制電機(jī),進(jìn)而提高機(jī)床加工精度。數(shù)控機(jī)床位置檢測系統(tǒng)采用模塊化和開放式控制,可減少電路規(guī)模和提高數(shù)控機(jī)床的加工精度,形成高密度、高精度的數(shù)控機(jī)床。采用數(shù)字電路的傳統(tǒng)位置檢測系統(tǒng)面積龐大、精度不高、發(fā)應(yīng)速度慢,而采用CPLD器件代替數(shù)字電路正好彌補(bǔ)這些缺陷。

2 CPLD簡介和器件選型

利用可編程邏輯器件CPLD(Complex Programable Logic Device)設(shè)計硬件系統(tǒng)非常方便。工程師通過傳統(tǒng)的原理圖輸入法,或是硬件描述語言自由設(shè)計數(shù)字系統(tǒng)。通過軟件仿真驗證事先設(shè)計的正確性。在PCB完成后,還可利用CPLD在線修改能力,隨時修改設(shè)計而不必改動硬件電路。因此,使用CPLD可大大加快硬件電路設(shè)計進(jìn)程,減少PCB面積,提高系統(tǒng)可靠性。

根據(jù)所需邏輯門數(shù)量以及將與其連接的電路引腳數(shù),選用ALTERA公司的EPM570T144C5型CPLD,該器件采用TQFP144封裝,內(nèi)部有570個邏輯單元,相當(dāng)于440個宏單元,而此前常用的EPM7128只有128個宏單元。

EPM570T144C5內(nèi)部有2個I/O分區(qū),共116個通用I/O,引腳延時為8.8 ns,滿足位置檢測系統(tǒng)所需的90多個通用I/O和延時不超過10 ns的設(shè)計要求。

3 位置檢測系統(tǒng)組成

在介紹位置檢測系統(tǒng)前,先簡要介紹伺服電機(jī)控制系統(tǒng)(圖1)。CPLD先對伺服電機(jī)光電編碼器上發(fā)出的反饋信號進(jìn)行譯碼、四倍頻鑒相計數(shù),然后將計數(shù)值存入鎖存器,當(dāng)用于電機(jī)控制的DSP控制器對CPLD進(jìn)行讀操作時,CPLD將鎖存器里的計數(shù)值通過三態(tài)門輸出給DSP控制器,由其控制電機(jī)的位移和速度。

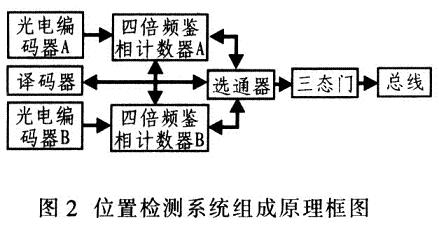

位置檢測系統(tǒng)采用CPLD器件實現(xiàn)硬件電路功能,用VHDL語言編程實現(xiàn)譯碼器、四倍頻鑒相計數(shù)器、選通器等模塊。圖2為位置檢測系統(tǒng)組成原理圖。圖2 中,光電編碼器A和四倍頻鑒相計數(shù)器A(光電編碼器B和四倍頻鑒相計數(shù)器B)構(gòu)成單軸計數(shù)電路,將兩個單軸計數(shù)電路配合譯碼器、選通器則構(gòu)成雙軸計數(shù)電路,就是用譯碼器控制選通器,以選通兩個計數(shù)器的計數(shù)結(jié)果并傳輸?shù)娇偩€.總線和選通器之間增加三態(tài)門進(jìn)行控制。這樣就實現(xiàn)雙軸位置檢測。

4 系統(tǒng)設(shè)計

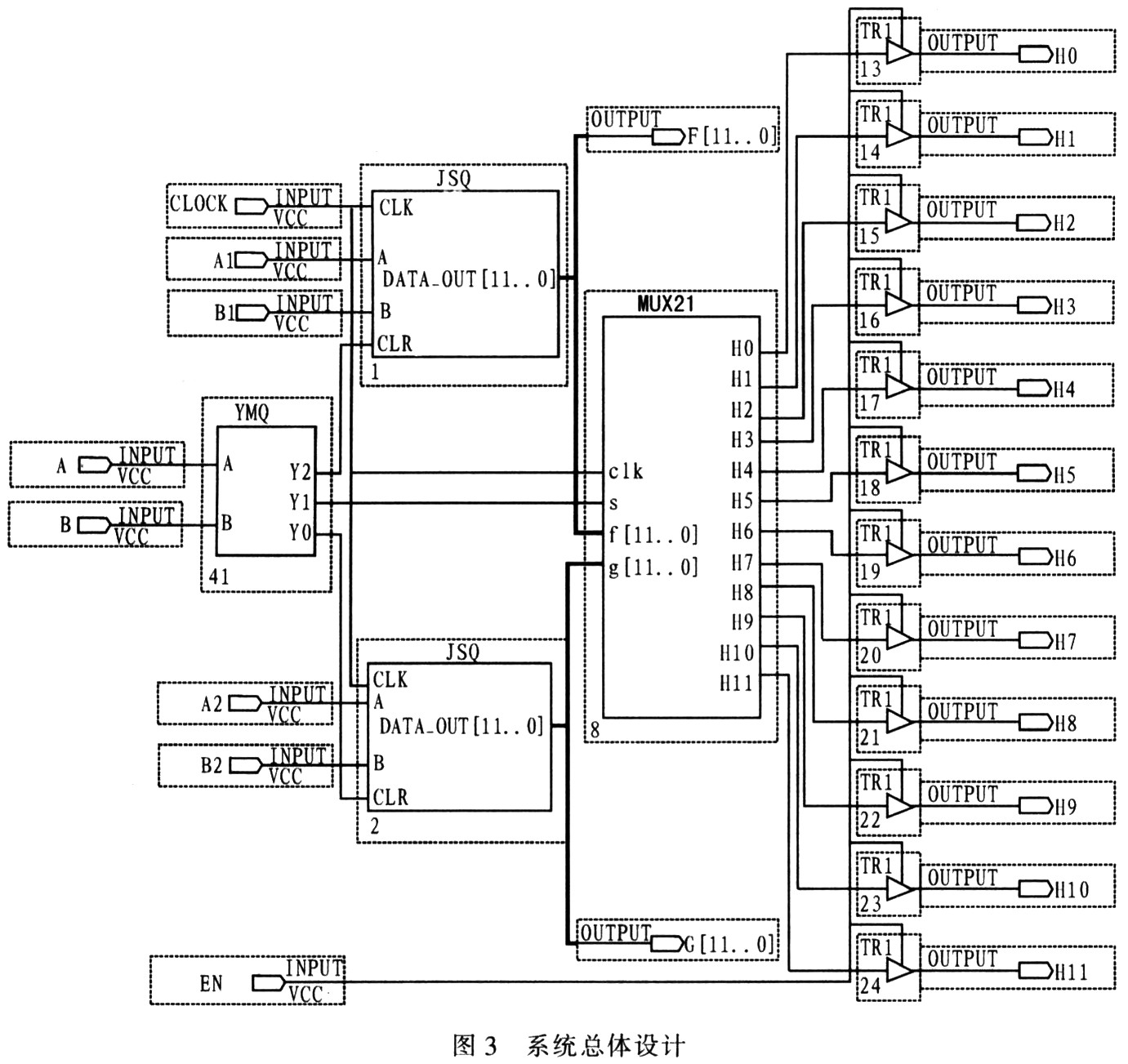

該系統(tǒng)設(shè)計的主要部分為伺服電機(jī)控制系統(tǒng)中的位置檢測系統(tǒng)。在Ouartus II開發(fā)環(huán)境下設(shè)計系統(tǒng),系統(tǒng)設(shè)計包括四倍頻鑒相計數(shù)器、二四譯碼器和選通器的VHDL程序設(shè)計,如圖3所示。通過圖2所示的原理框圖,將該系統(tǒng)設(shè)計的各個模塊組合起來形成頂層文件,構(gòu)成雙軸的檢測系統(tǒng)。圖3中YMO模塊為譯碼電路,用來選通哪軸輸出,Y0、Y2用來控制計數(shù)器的清零與計數(shù),Y1控制選通器選通,譯碼器真值表如表1所示。

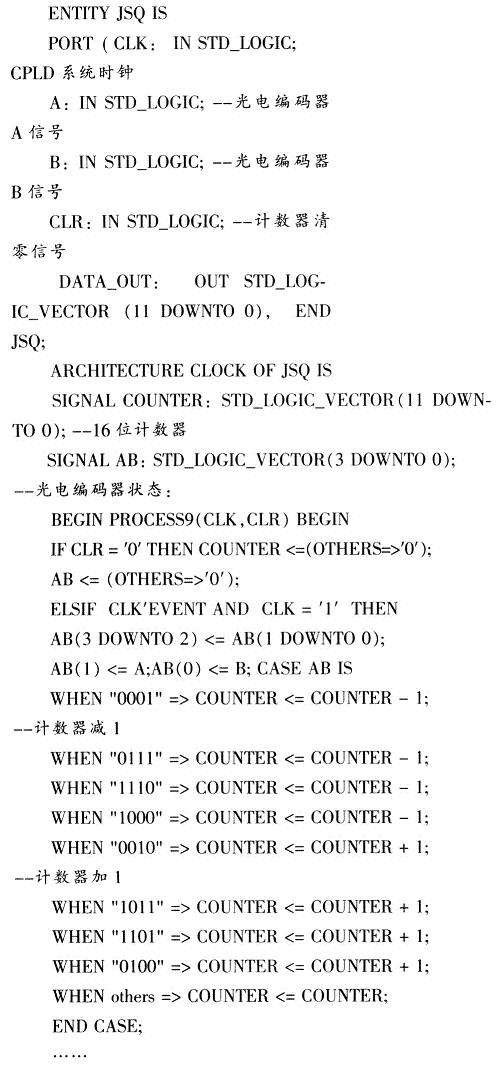

四倍頻鑒相計數(shù)器的VHDL程序代碼如下:

5 系統(tǒng)仿真

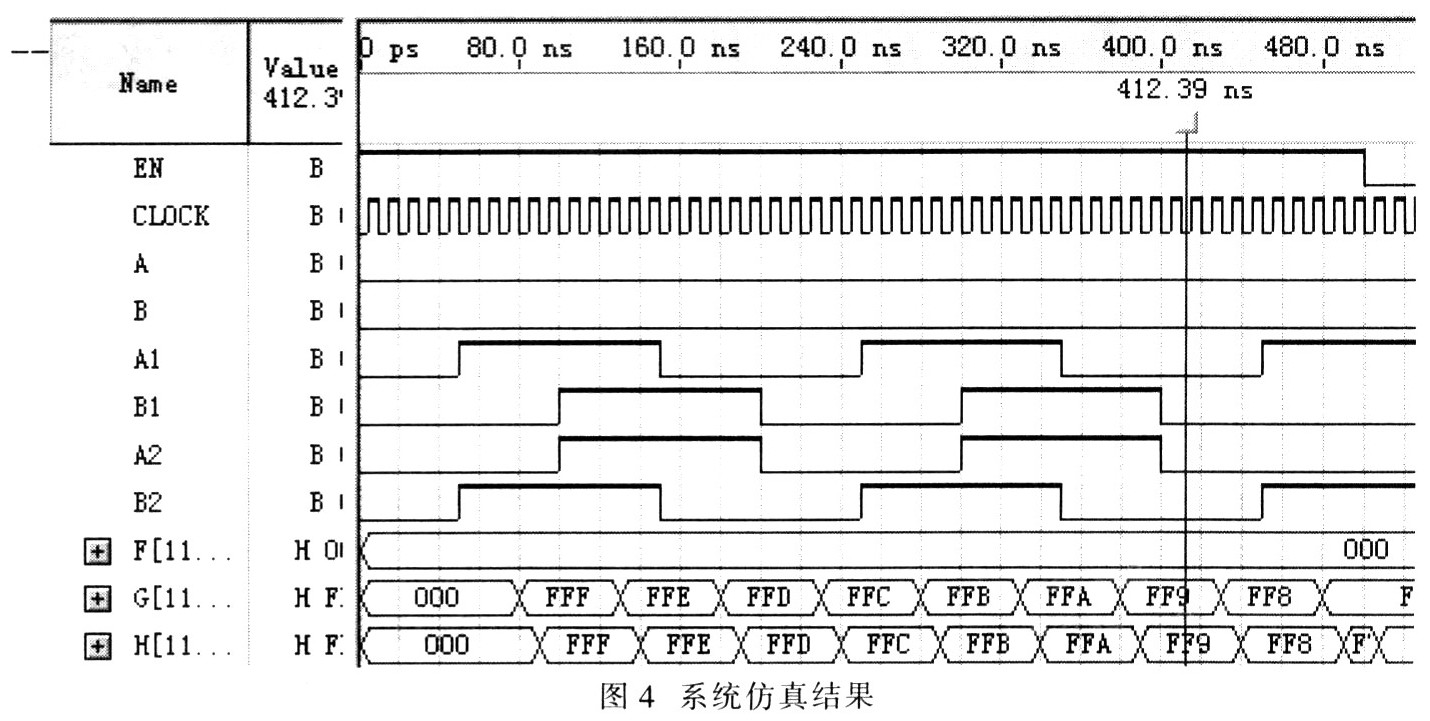

圖4為系統(tǒng)仿真結(jié)果。當(dāng)譯碼器控制信號AB=00時,可看出 A1超前B1,所以軸1正轉(zhuǎn);B2超前A2所以軸2反轉(zhuǎn)。

三態(tài)門使能信號EN=1時,數(shù)據(jù)選擇器選通G口所對應(yīng)的汁數(shù)器,即軸2,清零F口對應(yīng)計數(shù)器,即對軸1清零。并將計數(shù)結(jié)果傳輸?shù)娇偩€,輸出信號H從FFF 變化到FF8表明軸2反轉(zhuǎn),因此汁數(shù)器逆向計數(shù)。同時在AB譯碼器控制信號改變時和軸1,軸2正反轉(zhuǎn)的其他情況時,仿真結(jié)果均正確,滿足雙軸位置檢測系統(tǒng)設(shè)計。

6 結(jié)束語

在現(xiàn)代數(shù)控系統(tǒng)中,采用 CPLD實現(xiàn)位置檢測系統(tǒng)已成為主流。新一代CPLD產(chǎn)品MAX II EPM570以面積小、集成度高和 GPIO口多等特點(diǎn)使得電路板集成度和抗干擾性都得以提高,方便結(jié)合DSP控制伺服電機(jī)位臀。總之,CPLD器件的發(fā)展使得邏輯電子電路的設(shè)計更靈活、方便。它將推動數(shù)控機(jī)床甚至工業(yè)各領(lǐng)域的發(fā)展。