1.引言

為了提高傳輸速率,擴(kuò)大通信容量,減少信道數(shù)量,通常把多路信號復(fù)用成一路信號進(jìn)行傳輸。在多種復(fù)用方式中,時分復(fù)用是一種常用的方式。時分復(fù)用是多路信號按照時間間隔共享一路信道進(jìn)行傳輸。復(fù)接是把多路速率相對較低的數(shù)字信號通過某種協(xié)議復(fù)合成一路信號進(jìn)行傳輸;而分接正好相反,是把一路速率相比高的信號按照對應(yīng)的協(xié)議分割成發(fā)送端對應(yīng)的速率相對較低的信號。為了規(guī)范復(fù)接與分接協(xié)議,ITU(國際電信聯(lián)盟)根據(jù)傳輸速率的不同等級,將復(fù)接的數(shù)字信號為基群、二次群、三次群、四次群等,以我國實(shí)際應(yīng)用為例,速率分別:2.048MHz、8.4.48MHz、34.368MHz、139.264MHz。本文介紹基于FPGA實(shí)現(xiàn)二次群數(shù)字信號的分接部分的功能,包括幀頭捕獲、幀丟失告警、基群信號提取,去除插入碼、負(fù)碼速調(diào)整等二次群分接的關(guān)鍵技術(shù)。

2.二次群幀結(jié)構(gòu)介紹

二次群幀結(jié)構(gòu)如圖1所示,幀長為848bit,復(fù)幀包含的比特內(nèi)容如下:

(1)幀定位10bit,表示為F11F12~F13F23,碼型為1111010000;

(2) 公務(wù)2bit,其中1bit(11位)用來向?qū)Χ税l(fā)出告警指示;另外1bit(12位)留作國內(nèi)使用;

(3)支路信息820bit,第1組為200bit(13~212),第Ⅱ組為208bit(217~424),第Ⅲ組為208bit(429~636),第Ⅳ組為204bit(645~848);

(4) 碼速調(diào)整4bit,表示為V1,V2,V3,V4(641~644位),各基群1bit,共4bit;

(5)插入標(biāo)志12bit,以C表示,填充脈沖4bit。為了使接收端能知道是否有插入及插在何處,在復(fù)接端發(fā)出插入指令的同時需要發(fā)出插入標(biāo)志信號,以告知分接器有插入。目前常用的辦法是定位插入。在這里規(guī)定:第1基群第1位插入標(biāo)志C11在213位插入,第1基群第2位插入標(biāo)志C12在425位插入,第1基群第3位插入標(biāo)志C13在637位插入。由此可知:

C11C21C31C41是第1位插入標(biāo)志;

C12C22C32C42是第2位插入標(biāo)志;

C13C23C33C43是第3位插入標(biāo)志;

插入標(biāo)志信號是3位,采用3位碼來組成插入標(biāo)志信號,可提高標(biāo)志信號的可靠性。用"111"表示有插入,用"000"表示無插入。當(dāng)C11C12C13為"111"時,表示在641時隙的脈沖是插入脈沖;當(dāng)C11C12C13為"000"時,表示在641時隙的脈沖是信息碼。

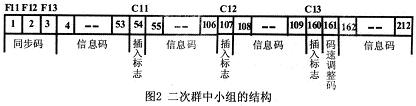

一幀分為4組,每組為212bit,這212bit的分配如圖2所示,4個基群相似,以第1基群為例。將212bit分為4組,每組53bit。第1組的1,2,3三個碼位,供插入復(fù)接器幀同步碼用,以F表示;然后是50bit的信息碼;Ⅱ,Ⅲ,Ⅳ組的第1位碼用作標(biāo)志信號,用C表示;第Ⅳ組的第2個碼位就是碼速調(diào)整的碼位,用V表示,需要插入時,就在這個位置上插入一個不帶信息的脈沖,不必插入時,這個碼位仍傳信息碼;Ⅱ、Ⅲ、Ⅳ組的其他位置都是信息碼。4個基群的第1~3個碼位復(fù)接在一起,共12位,其中前10位作為復(fù)接器的幀同步碼,第12位為告警指示,第12位作為備用。4個基群的插入標(biāo)志信號碼和碼速調(diào)整比特,復(fù)接后又分別連在一起。

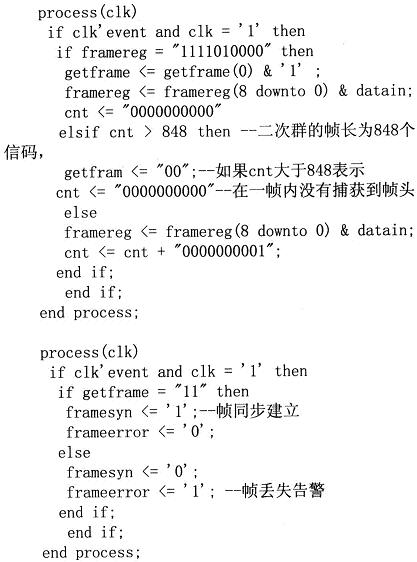

3.二次群幀頭捕獲及幀丟失告警

根據(jù)上面二次群幀結(jié)構(gòu)的分析,二次群的幀頭信碼為:”1111010000“10個bit,在FPGA中,定義一個10位的寄存器,二次群信碼從右向左進(jìn)入10位寄存器,如果10位寄存器的值連續(xù)兩次為:”1111010000"則表示幀頭捕獲成功,幀同步建立。同樣如何連續(xù)兩個二次群幀時間長度內(nèi)沒有捕獲到幀頭信碼,則表示幀丟失,產(chǎn)生幀丟失告警。VHDL語言代碼實(shí)現(xiàn)如下程序段:

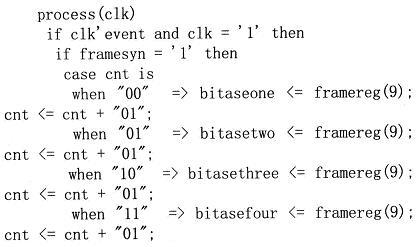

4.基群信號提取

一個二次群信號復(fù)接了四個基群信號,基群信號提取是在二次群幀同步的狀態(tài)下把二次群信號按一分四的規(guī)則進(jìn)行串并轉(zhuǎn)化。因?yàn)槎蔚膹?fù)接是按bit復(fù)接,所以二次群一幀中第一位為第一個群的第一位,二次群一幀中第二位為第二個群的第一位,以此類推。VHDL語言代碼實(shí)現(xiàn)如下程序段:

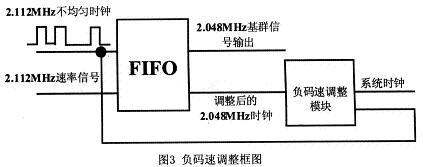

5.去除插入碼及負(fù)碼速調(diào)整

去除插入碼及負(fù)碼速調(diào)整是二次群的關(guān)鍵部分,首先要去除幀頭插入的F1、F2和F3;接著去除C1、C25DC3;最后根據(jù)C1、C2和C3值來判斷第161位V否為插入碼,如果C1C2C3為:"1 11",則V是插入碼應(yīng)去除,如果C1C2C3為:"000",則V是基群的信碼,不應(yīng)去除。把去除了插入碼的信號輸入到一個FIFO,用經(jīng)過負(fù)碼速調(diào)整過的2.048MHz時鐘讀出輸出基群信號如圖3所示。