0 引言

無論是何種通信新業(yè)務的推出和運營,都離不開強力有效且高可靠的傳輸系統(tǒng)。隨之而帶來的問題就是如何對系統(tǒng)的傳輸質(zhì)量進行測量和保證。

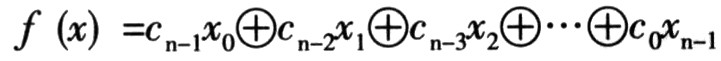

誤碼測試儀是一種能夠測量和保證傳輸質(zhì)量的智能化儀器,該儀器可通過檢測來反映數(shù)據(jù)傳輸設備及其信道工作的誤碼損傷性能質(zhì)量指標,并對其進行傳輸質(zhì)量分析的有效工具。在電信運營、工程驗收、科研、設備生產(chǎn)、教學實驗等各方面,誤碼儀都是必不可少的通信測量和線路維護的最佳輔助工具。目前在陜西省業(yè)務設備的接口應用中,百分之九十以上的接口是2M的接口,比如:交換網(wǎng)絡上應用、信令網(wǎng)上的應用、數(shù)據(jù)網(wǎng)上的應用、網(wǎng)管網(wǎng)上的應用等,都使用了2M的數(shù)據(jù)。針對傳統(tǒng)誤碼儀的不足,本文給出了基于Altera公司的cyclone系列FPGA芯片EP1C12-240PQFP的2M誤碼測試儀的設計方案。基于FP- GA的誤碼測試儀相對于傳統(tǒng)的誤碼測試儀的優(yōu)點在于其FPGA的內(nèi)部邏輯功能是通過向內(nèi)部靜態(tài)存儲器單元加載配置數(shù)據(jù)來實現(xiàn)的。其配置文件決定了邏輯單元的邏輯功能以及模塊間或與I/O間的連接,并最終決定了FPGA所實現(xiàn)的功能。FPGA的這種結構允許多次編程,并享有快速有效地對新設計進行優(yōu)化的靈活性,故現(xiàn)今的通信系統(tǒng)大量采用FPGA作為系統(tǒng)的核心控制器件。本文重點介紹了FPGA內(nèi)核中序列發(fā)生模塊和序列接收模塊中核心內(nèi)容的設計。其中FPGA 內(nèi)核中m序列發(fā)生器的設計思想采用移位寄存器理論,并根據(jù)本原多項式來獲得m序列移位寄存器的反饋邏輯式:

其中cn-1-i∈GF(2)是反饋系數(shù),xi∈GF(2)是每位寄存器的狀態(tài)。這樣,結合cyclone系列FPGA芯片EP1C12-240PQFP的結構特點,就很容易實現(xiàn)反饋移位寄存器的邏輯功能。

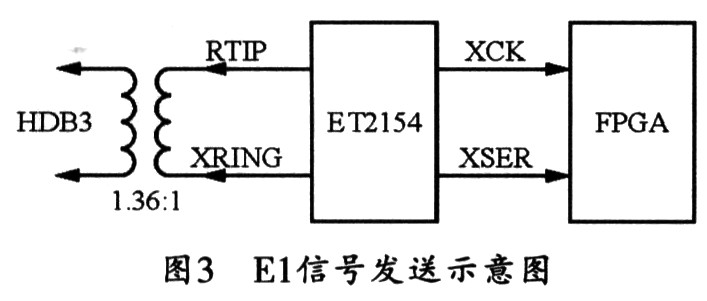

1 誤碼測試系統(tǒng)的總體方案

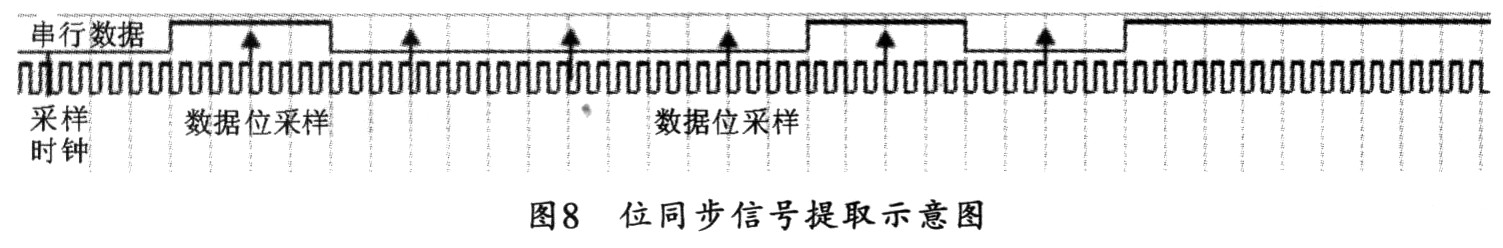

誤碼一般是由通信系統(tǒng)中接收端抽樣判決器的錯誤判斷造成的,而造成錯誤判斷的原因主要有兩個:一是碼間串擾,另一個是信道加性噪聲的影響。誤碼測試儀存在兩種設計方案,一種是誤碼儀的發(fā)射端模塊和接收模塊兩部分獨立,可用于單工的通信系統(tǒng)性能測試。但是由于該系統(tǒng)的測試序列需要動態(tài)生成,所以,其能夠測試的系統(tǒng)碼速只能和FPGA控制模塊所能達到的速度相同。另一種方案是將發(fā)射端模塊和接收模塊結合在一個系統(tǒng)內(nèi)部,這樣能測試具有回環(huán)的通信系統(tǒng),如雙工通信的收發(fā)設備等。本文設計屬于第二種方案,其誤碼測試系統(tǒng)框圖如圖1所示。圖中,發(fā)送端模塊產(chǎn)生的偽隨機序列作為通信系統(tǒng)的信源數(shù)據(jù)流流經(jīng)信道,接收端模塊則接收來自信道輸出的比特流,并將其與接收端模塊產(chǎn)生的與發(fā)送端模塊輸出類型相同的偽隨機序列進行比較,從而完成誤碼測試。誤碼儀由發(fā)送端的序列發(fā)生器 1模快、接收端的位同步信號提取模塊、幀同步碼檢測模塊、序列發(fā)生器2模塊、誤碼分析模塊及外設接口構成。其中位同步信號提取模塊的作用是獲得位定時同步脈沖。幀同步碼檢測模塊的作用是獲取幀同步信號,以使兩個序列能以同相位比較計算誤碼率。因為如果接收的測試序列與序列發(fā)生器2模塊產(chǎn)生的序列兩者相位不同,則誤碼的測試結果將毫無意義。

2 系統(tǒng)硬件設計

2.1 系統(tǒng)硬件組成

根據(jù)誤碼測試儀器的功能要求,在本系統(tǒng)的硬件總體架構中,將FPGA作為總控制器,并外擴E1接口模塊,以用于實現(xiàn)碼型和波形的轉(zhuǎn)換,同時將FPGA輸出的NRZ碼型轉(zhuǎn)換成適合于在E1信道中傳輸?shù)腍DB3碼型,并將來自E1信道的HDB3碼轉(zhuǎn)換為NRZ碼送入FPGA中;E2PROM存儲模塊則可將誤碼分析模塊的誤碼測試結果進行存儲,且掉電不丟失數(shù)據(jù),并可隨時讀取,以便于在無人值守的情況下進行誤碼測試;LCM顯示模塊是為了使用戶了解誤碼測試結果;RS232串口模塊則用于和PC機通訊,上傳誤碼檢測結果,以便于從PC機上看到一段時間內(nèi)誤碼率曲線圖及其它誤碼信息,使用戶了解通信系統(tǒng)的誤碼發(fā)生情況;此外,系統(tǒng)還外擴有鍵盤、電源管理模塊、時鐘電路、JTAG下載口和AS下載口。

2.2 E1接口電路的設計

E1的標準傳輸線路碼通常采用三階高密度雙極性碼(HDB3,high density bipolar),它是一種雙極性歸零碼,是廣泛用于PCM線路的傳輸碼型。本文中的E1接口選用非平衡的75 Ω物理接口(一收一發(fā))。E1接口芯片ET2154是一路E1PCM-30/ISDN-PRI收發(fā)器,它集成有時鐘數(shù)據(jù)恢復及發(fā)送E1脈沖成型的片內(nèi)線路接口單元(LIU)和E1幀處理器(Framer),其各項指標符合ITU-T的G.703、G.704、G.706、G.823建議等要求。 ET2154的線路接口功能主要包括三部分。第一是接收器,用于處理時鐘和數(shù)據(jù)恢復;第二是發(fā)送器,用于形成波形和驅(qū)動E1線路;第三是抖動抑制器。

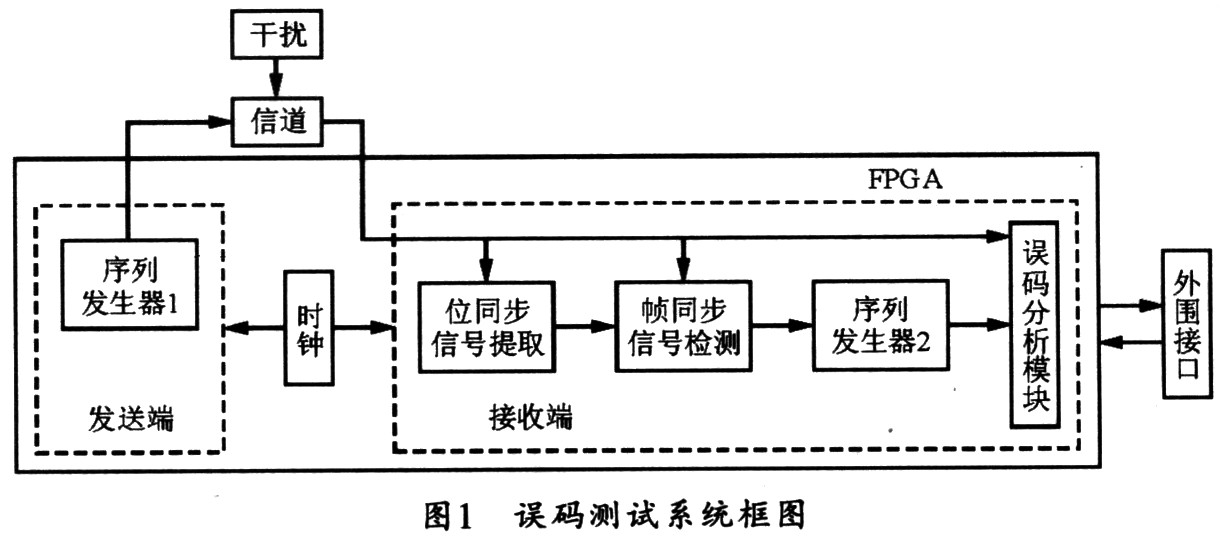

(1)E1線路接收接口

當HDB3碼流從E1線纜經(jīng)BNC接口進入,并通過一個1:2的變壓器耦合至RTIP租RRNG輸入管腳后,其接收模塊將允許用戶設置寄存器以匹配外部線路的阻抗。ET2154中的數(shù)據(jù)時鐘恢復模塊可從HDB3碼流中恢復時鐘和數(shù)據(jù)。從HDB3碼流中恢復出時鐘和數(shù)據(jù)可通過高倍采樣來實現(xiàn),首先由外部提供一個2.048 MHz的時鐘信號,然后由芯片內(nèi)部PLL將它16倍頻到32.768 MHz 。即先對每位HDB3碼進行16倍的采樣,然后由時鐘恢復系統(tǒng)利用16倍的采樣時鐘來恢復時鐘和數(shù)據(jù)。其E1信號接收示意圖如圖2所示。

正常情況下(RTIP,RRING有信號輸入),在RCK(接收方向恢復時鐘)管腳輸出恢復后的時鐘信號。而當ET2154被配置成輸出NRZ數(shù)據(jù)模式時,則在RSER管腳輸出恢復出的串行數(shù)據(jù)信號并送入FPGA。

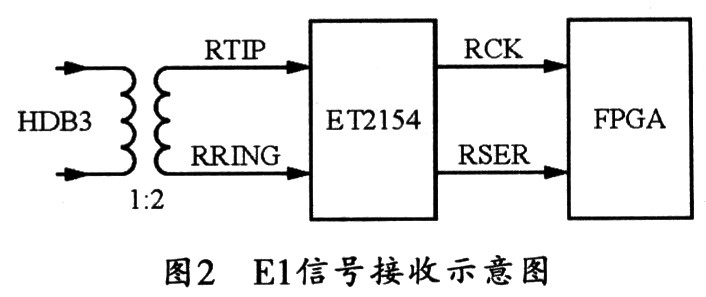

(2)E1線路發(fā)送接口

待傳輸?shù)拇袛?shù)據(jù)流一般由XSER (發(fā)送串行數(shù)據(jù)NRZ)管腳進入ET2154,并在XCK(發(fā)送方向輸入時鐘)管腳接收來自FPGA的2.048 MHz的時鐘信號。ET2154主要由內(nèi)部精密的數(shù)模轉(zhuǎn)換器(DAC)來產(chǎn)生要發(fā)送到E1線路上的波形,這種波形符合ITU G.703規(guī)范。系統(tǒng)中的發(fā)送器可將模擬波形從TYIP、TRING管腳通過1:1.36的升壓變壓器耦合到E1線路上。其E1信號發(fā)送示意圖如圖3所示。

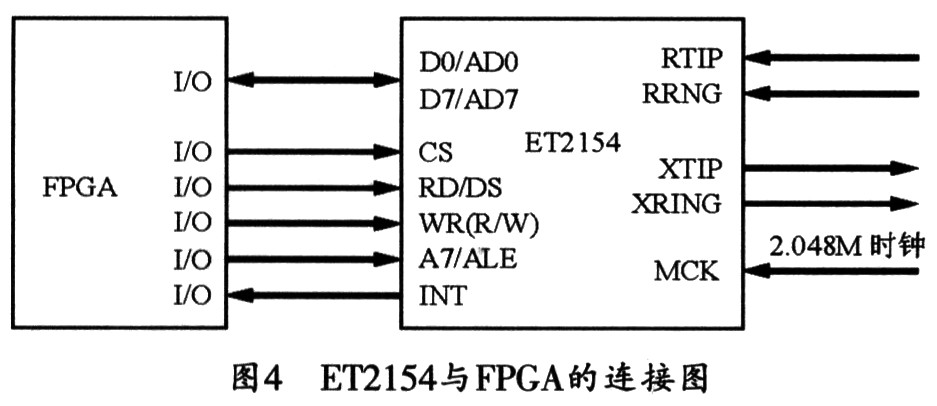

(3) E1線路控制接口

ET2154的工作方式和特性是通過對其外部管腳的控制來實現(xiàn)的。通常將這些控制管腳連接至FPGA的外部I/O口,由FPGA來進行控制。ET2154 與FPGA的連接電路如圖4所示。ET2154通過內(nèi)部寄存器的配置來設置其工作方式,F(xiàn)PGA則利用8位數(shù)據(jù)/地址復用線AD0~AD7來對 ET2154內(nèi)部的寄存器進行設置,從而實現(xiàn)所需要的功能。

3 系統(tǒng)軟件設計

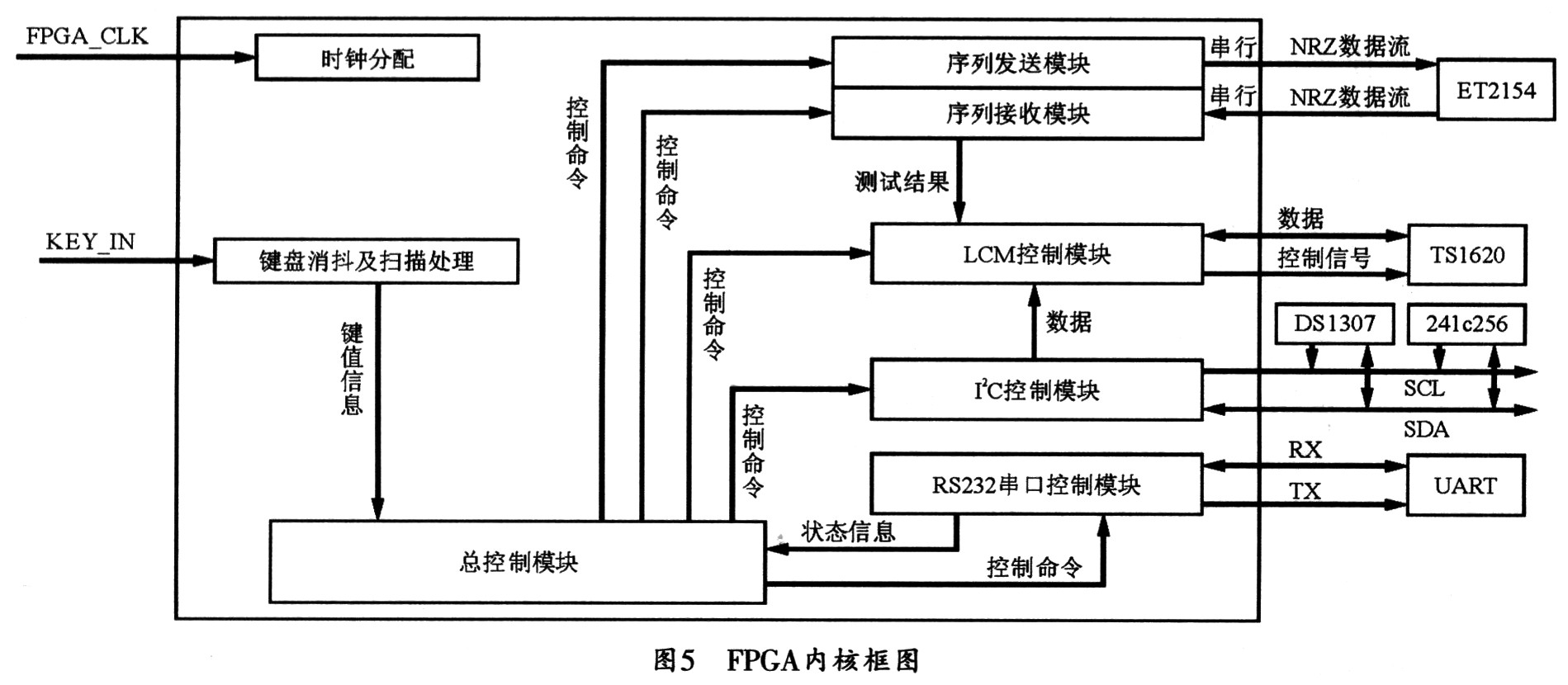

在對系統(tǒng)軟件進行設計時,可將誤碼測試系統(tǒng)的功能分為各個功能模塊,然后用VHDL語言編程實現(xiàn)FPGA芯片內(nèi)部各個功能模塊的硬件邏輯,最后整合完成設計。本誤碼測試系統(tǒng)的FP-GA內(nèi)核中的功能模塊有時鐘分配模塊、序列發(fā)送模塊、序列接收模塊、LCM控制模塊、I2C控制模塊、RC232串口控制模塊、鍵盤消抖及掃描處理模塊、總控制模塊等。FPGA內(nèi)核中各個模塊之間的相互關系如圖5所示。

3.1 鍵盤處理模塊

本系統(tǒng)中的鍵盤處理模塊包括按鍵的消抖和鍵盤的掃描處理。由于鍵盤模塊的設計直接和用戶的輸入控制相關,用戶的一切控制結果都和按鍵輸入相對應,所以可將總控制模塊和按鍵處理模塊放在一起考慮。

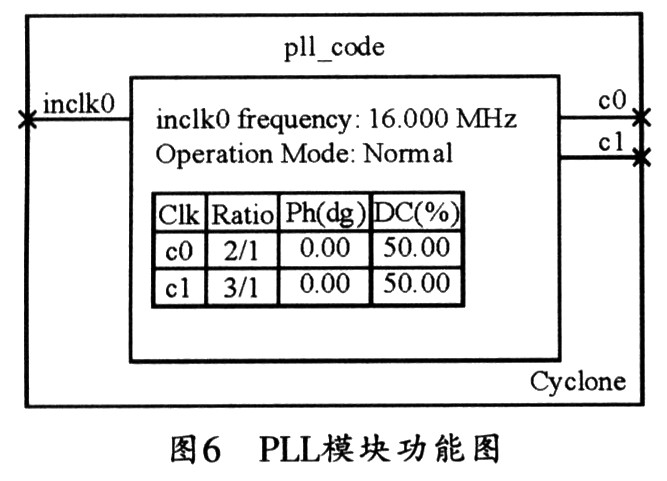

3.2 時鐘電路

時鐘是整個系統(tǒng)設計中重要的一環(huán)。序列發(fā)送、序列接收、對E2PROM模塊的讀與寫、串口通信的波特率以及LCD顯示等都離不開時鐘信號的控制,這就需要系統(tǒng)內(nèi)有一個基準的時鐘模塊來提供所需要的時鐘信號。時鐘模塊可由鎖相環(huán)和分頻器模塊構成。通過對QuartusⅡ中mega-function模塊 ALTPLL的定制可生成PLL,inclk0是外部有源晶振提供給FPGA的clk0引腳的16 MHz時鐘,可經(jīng)過PLL產(chǎn)生C0、C1兩個時鐘信號,其中C0是inclk0的2倍,為32 MHz,可作為序列接收模塊中對測試碼進行采樣的采樣時鐘。而C1是inclk0的3倍,為48 MHz,設計時可將C1信號送入分頻電路獲得2 MHz時鐘,作為序列發(fā)生器的時鐘;也可將C1信號經(jīng)分頻電路獲得1 MHz時鐘,作為I2C控制模塊的讀/寫及鍵盤模塊的時鐘信號;當C1信號送入UART控制模塊和LCM控制模塊后,可通過各自模塊內(nèi)部的分頻電路獲得所需要的時鐘。圖6所示的PLL模塊中方框內(nèi)表格中的各項內(nèi)容分別表示信號名稱、信號倍率、信號相位及占空比。

3.3 測試序列發(fā)送模塊的軟件設計

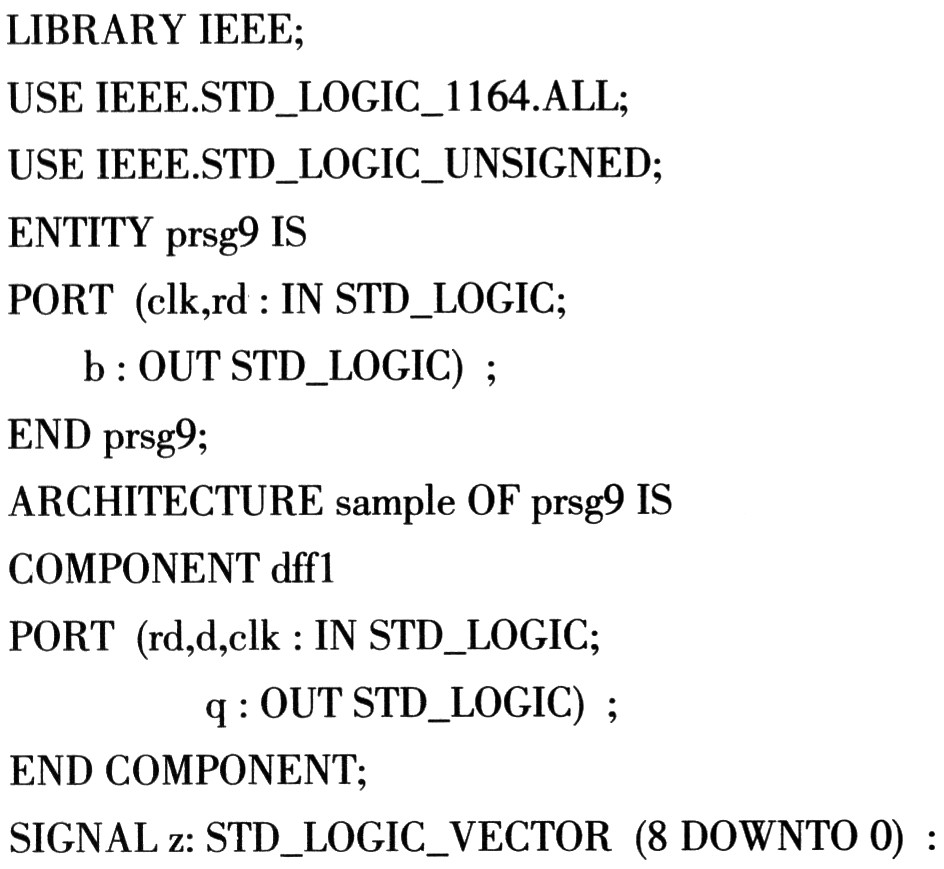

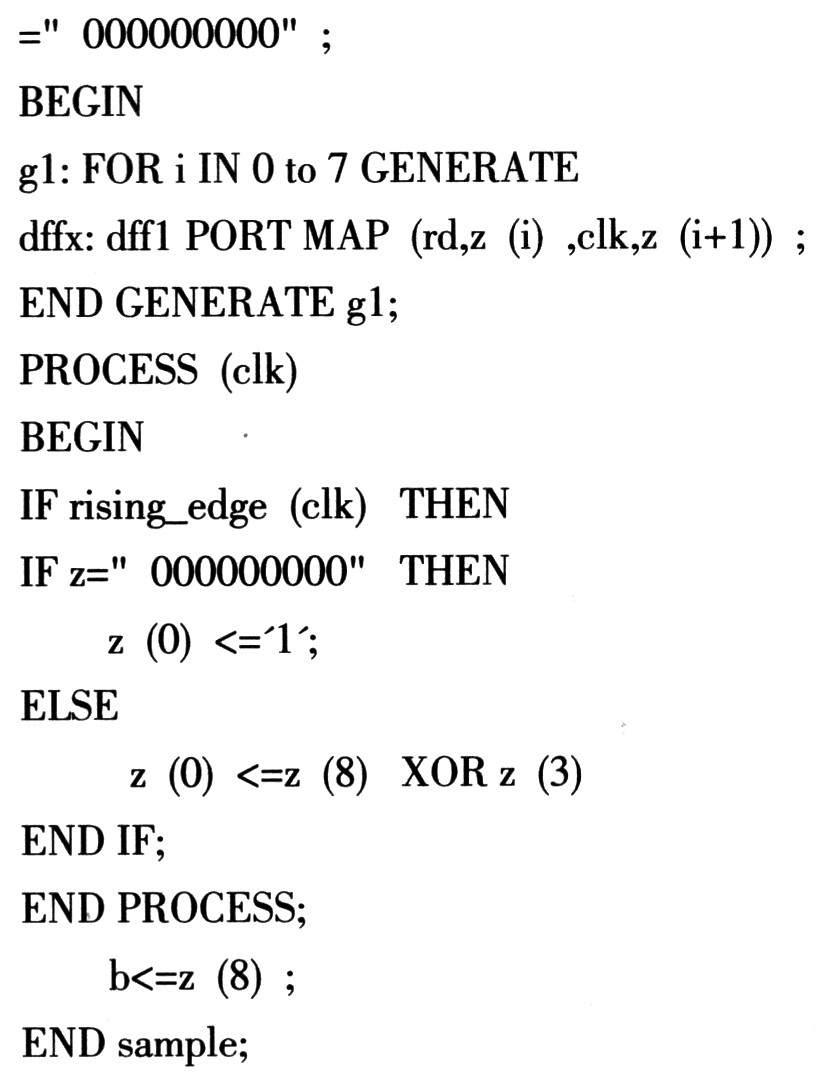

測試序列采用m序列時,ITU建議用于數(shù)據(jù)傳輸設備測量誤碼的m序列的周期是511,其特征多項式(本原多項式)建議采用f(x)=x9+x5+1,本文應用移位寄存器理論從本原多項式出發(fā)來產(chǎn)生m序列,本原多項式是f(x)=x9+x5+1的m序列的VHDL語言編程如下:

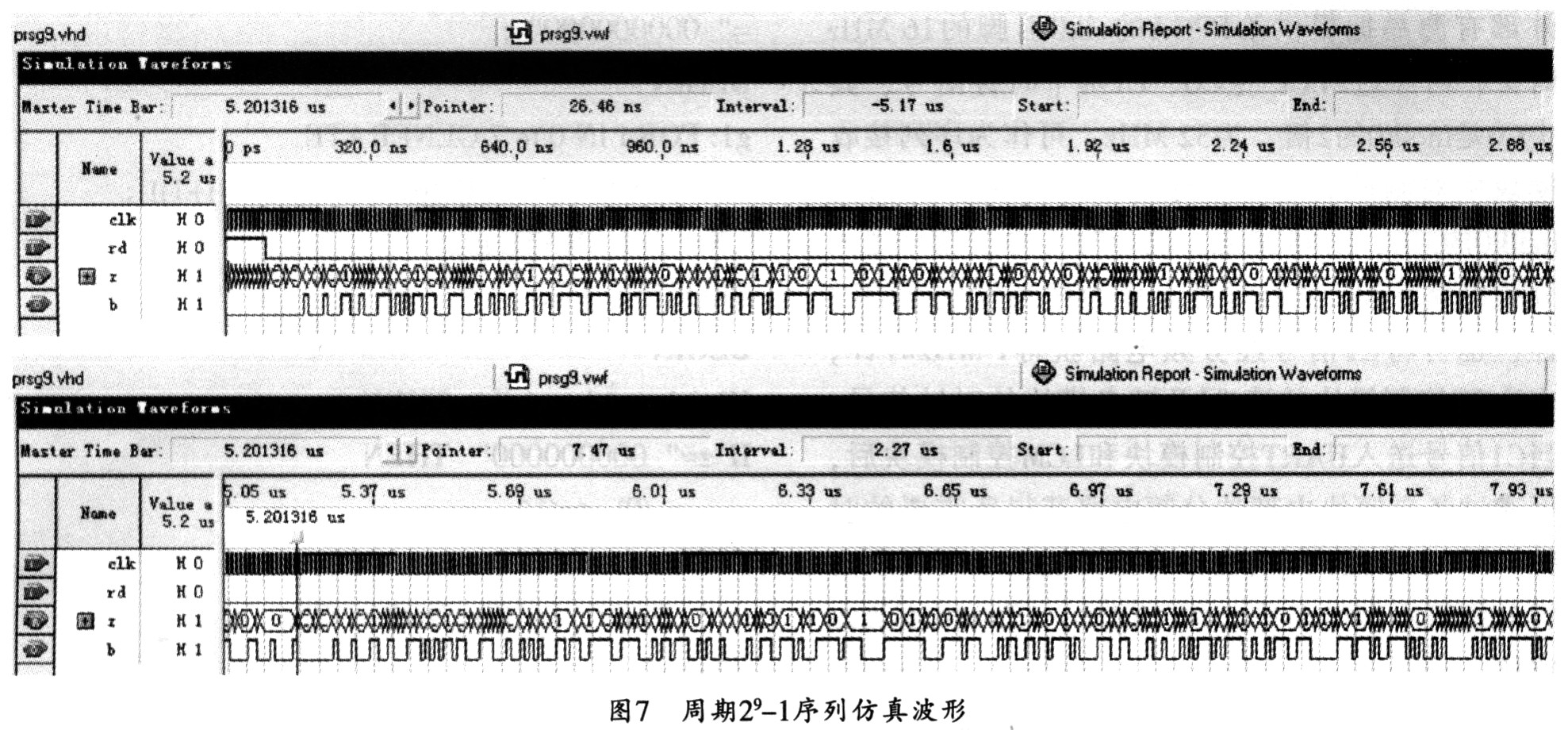

在Ahera的Quaaus II開發(fā)平臺下,本原多項式f(x)=x9+x5+1的m序列的仿真波形如圖7所示。

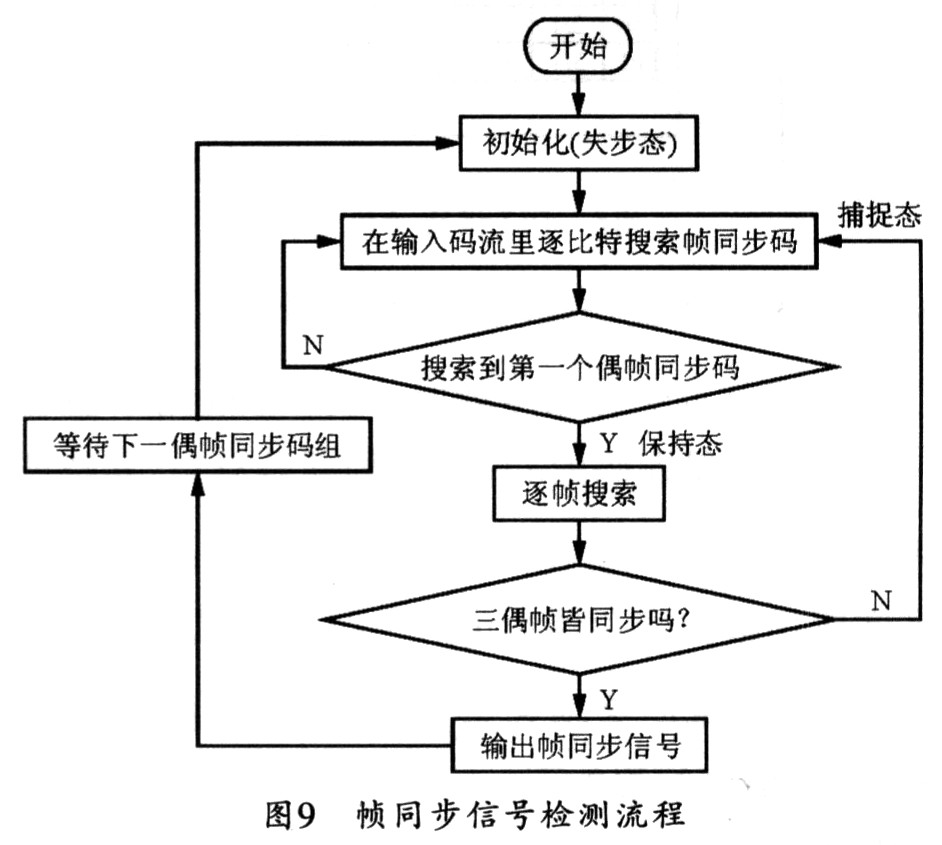

3.5 幀同步信號檢測

對幀同步電路的一項基本要求就是要迅速發(fā)現(xiàn)失步,以便及時恢復同步。若在發(fā)送端插入幀同步碼“0011011”,那么,在誤碼檢測時,由于E1串行數(shù)據(jù)流中也會出現(xiàn)“0011011”這樣的內(nèi)容,因而難以判斷哪些是幀同步碼,哪些是數(shù)據(jù)內(nèi)容,所以,在設計中,可采用計數(shù)器來進行幀同步碼的定位。

E1的幀周期為125μs,兩幀即為250 μs,這樣,若規(guī)定當捕捉到第一個同步序列后,只有在一段時間內(nèi),每間隔250μs,可連續(xù)三次(計數(shù)器計數(shù))捕捉到這個同步序列時,才認為找到了幀同步。與此類似,在一段時間內(nèi),如果連續(xù)三次都沒有捕捉到幀同步序列,那么,即可認為幀同步丟失。其幀同步信號檢測流程如圖9所示。

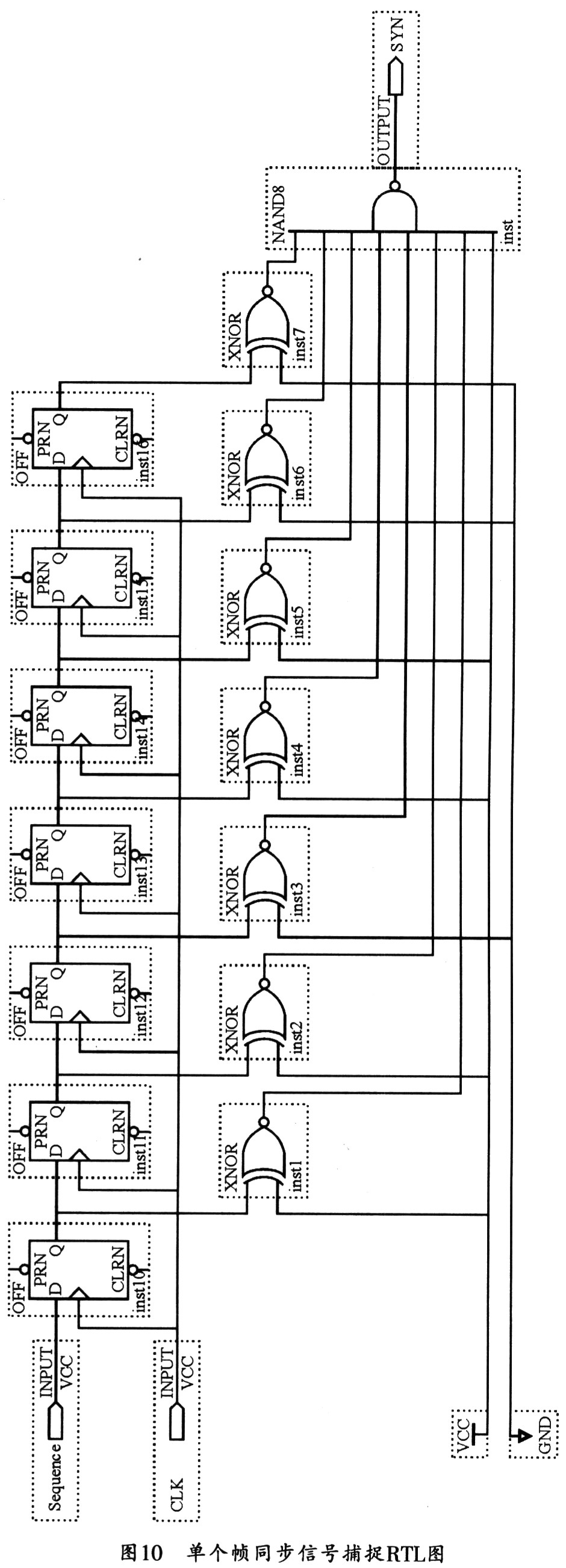

在單個幀同步序列捕捉的FPGA實現(xiàn)中,“0011011”序列的捕捉由輸入序列移位寄存器、相關運算陣列和相關求和網(wǎng)絡等部分組合完成。工作時,幀同步碼序列“0011O11”首先進入相關運算陣列,而輸入數(shù)據(jù)流則在時鐘驅(qū)動下被送入輸入序列移位寄存器中。在相關運算陣列對輸入序列和幀同步碼進行一次相關運算后,可將結果送入求和網(wǎng)絡。輸入序列移位寄存器每更新一位數(shù)據(jù),相關運算陣列就進行一次相關運算,而求和網(wǎng)絡則對每次的結果都進行求和計算。求和網(wǎng)絡輸出的相關值需要與一個檢測門限值作比較,以判斷是否出現(xiàn)同步碼。檢測同步碼“001 1011”的模塊如圖10所示,它由7個觸發(fā)器、7個異或非門和一個8輸入與非門構成。該電路可以檢測出sequence串行輸入的數(shù)據(jù)流中包含的特殊碼字“0011011”,其中利用地線和電源線可將相關運算陣列的一個輸入自右向左的連接成“0011011”,與同步碼字對應的另一個輸入端接輸入序列移位寄存器的輸出,7個對應位可進行異或非(同或)運算,對應位匹配時,結果為“1”。7個異或非門的運算結果進入求和網(wǎng)絡后,只有當7位對應位全都匹配時,捕捉信號SYN才有效(有效狀態(tài)為“0”),此時表明找到了一次同步序列碼。

4 結束語

本文所介紹的誤碼測試系統(tǒng)采用以大規(guī)模現(xiàn)場可編程邏輯器件FPGA及外圍接口芯片構成,文中詳細介紹了系統(tǒng)硬件架構中EI接口電路以及FPGA內(nèi)核中序列發(fā)生模塊和序列接收模塊中核心內(nèi)容的設計方法,并給出了部分模塊的仿真波形。整個誤碼測試系統(tǒng)儀器結構緊湊。實驗表明,該系統(tǒng)在線檢測的速度和穩(wěn)定度方面都有大的提高。