摘 要: 一種基于USB2.0接口芯片" title="接口芯片">接口芯片ISP1581與FPGA技術(shù)的通用數(shù)據(jù)采集" title="數(shù)據(jù)采集">數(shù)據(jù)采集平臺。系統(tǒng)采用TI公司的10位、20MSPS的TLC876高速A/D" title="A/D">A/D芯片,可以靈活地進行高速、低速采集的配置,構(gòu)建多種以PC機為界面的數(shù)據(jù)采集平臺。PC端采集軟件平臺采用了多線程程序設(shè)計技術(shù)。

關(guān)鍵詞: USB2.0 FPGA 數(shù)據(jù)采集 多線程

近年來筆記本電腦迅速普及和更新,其中大部分已經(jīng)不配置RS232接口,而USB接口已成為今后一段時間PC機與外設(shè)接口的主流。本采集系統(tǒng)的設(shè)計構(gòu)建了一個基于USB接口的多功能通用數(shù)據(jù)采集、傳輸平臺,將嵌入式系統(tǒng)的實時性、靈活性和PC機強大的數(shù)據(jù)存儲、處理、顯示功能結(jié)合起來。該采集系統(tǒng)在智能儀器儀表、測控系統(tǒng)、工控系統(tǒng)等領(lǐng)域有廣闊的應用前景。

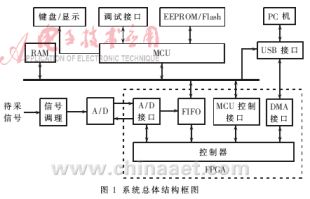

1 系統(tǒng)總體結(jié)構(gòu)設(shè)計

1.1 系統(tǒng)總體結(jié)構(gòu)

系統(tǒng)總體結(jié)構(gòu)框圖如圖1所示,系統(tǒng)包括:單片機與USB接口模塊、FPGA模塊、信號調(diào)理及A/D模塊。其中,單片機外圍電路相對簡單,整個系統(tǒng)主要通過PC機的程序界面控制操作;USB接口負責與PC機通信;FPGA模塊負責完成數(shù)據(jù)的采集與緩存。

1.2 單片機與USB接口模塊

本設(shè)計的目的是構(gòu)建以PC機為平臺的數(shù)據(jù)采集系統(tǒng)" title="數(shù)據(jù)采集系統(tǒng)">數(shù)據(jù)采集系統(tǒng),單片機的功能僅限于接收PC機的命令、控制FPGA工作。PC機作為整個系統(tǒng)的人機界面,控制整個數(shù)據(jù)采集系統(tǒng)進行采集、存儲和處理。由此單片機可以選擇低成本的8XC51系列。為了提高系統(tǒng)的靈活性,采用單片機與USB接口芯片分離的方案,選擇Philip公司的ISP1581 USB2.0接口芯片。該芯片與8XC51系列單片機的接口非常簡單,可以極大地降低系統(tǒng)成本。

1.3 FPGA模塊

采用FPGA進行采樣控制的最大特點是系統(tǒng)具有重構(gòu)性和通用性。設(shè)計中采用了Altera公司的低成本FPGA的Cyclone系列(實際試驗時,在更便宜的Acex1k器件上也可以實現(xiàn)),控制高速A/D芯片以20MSPS的速度采樣。FPGA模塊的設(shè)計具體包括FIFO、單片機接口、A/D控制接口、DMA控制模塊和主控制器等子模塊的設(shè)計。

1.4 PC機端軟件平臺

PC機采集程序使用VC++實現(xiàn),直接調(diào)用Philips公司提供的驅(qū)動程序進行數(shù)據(jù)讀寫,大大降低了開發(fā)難度與風險。本設(shè)計中,PC機端軟件設(shè)計包括應用程序的界面設(shè)計、多線程數(shù)據(jù)采集、存儲與處理模塊的設(shè)計,以及與USB底層驅(qū)動程序的通信動態(tài)鏈接庫的設(shè)計。

2 USB接口模塊設(shè)計

2.1 USB接口芯片

USB接口芯片ISP1581具有體積小、高速、與單片機的接口相對簡單等特點。除了控制端點外,ISP1581還有7個輸入(IN)端點和7個輸出(OUT)端點。每個端點可以靈活配置數(shù)據(jù)傳輸方式以及數(shù)據(jù)緩存區(qū)(FIFO)的大小,端點FIFO最大容量可以達到2KB。ISP1581芯片在配置枚舉時需要單片機固件" title="固件">固件的支持,一旦正確完成了配置和驅(qū)動加載,單片機對于ISP1581芯片就如同普通存儲器一樣可以進行讀寫操作,以發(fā)送或接收數(shù)據(jù)。

2.2 固件編程

USB通信完全由PC主機發(fā)起。在這種結(jié)構(gòu)下,固件總是一直在等待主機命令,再根據(jù)命令去執(zhí)行相應的程序。固件的基本思想是采用模塊化設(shè)計,分成 main.c等7個模塊。ISP1581固件結(jié)構(gòu)如圖2所示。圖中,main.c為主循環(huán),isr.c主要負責中斷處理,Chap9.c主要負責響應主機的請求。用戶的應用程序?qū)硪部梢园ㄔ趍ain.c循環(huán)中。

2.3 單片機端程序設(shè)計

單片機端程序主要包括初始化模塊,外圍Flash、EEPROM、RAM、液晶顯示器、按鍵等的讀寫控制模塊,USB接口芯片固件模塊,A/D采樣工作模式、速度以及采樣數(shù)據(jù)的讀寫的FPGA硬件控制模塊等。本設(shè)計的指導思想是:充分利用PC機和嵌入式系統(tǒng)的優(yōu)點,對MCU端的要求盡量簡化。具體軟件流程示意圖如圖3所示。

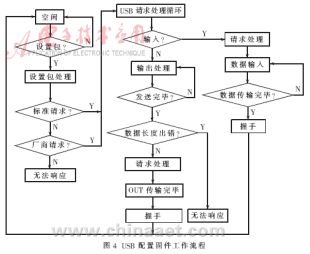

USB作為一個通信接口,首先必須完成配置,然后才能進行用戶數(shù)據(jù)的發(fā)送/接收,在循環(huán)中必須隨時檢查是否有主機的配置命令。配置枚舉過程是USB固件編程當中較為復雜的部分,其流程如圖4所示。USB設(shè)備接入到主機并被主機識別后,主機首先以默認的地址(00H)發(fā)送一個設(shè)置(SETUP)包,新接入的設(shè)備必須接收此包并響應請求。然后主機會發(fā)送輸入包讀取設(shè)備描述符,初步判斷設(shè)備的屬性后,再設(shè)置設(shè)備的地址,隨后再用這個地址讀取設(shè)備的各種描述符以識別并且配置設(shè)備。可見,在設(shè)備配置過程中,主機讀取的數(shù)據(jù)較多,設(shè)備一旦接收到一個SETUP包之后便會判斷主機的請求類型,然后進入請求處理循環(huán)等待主機的進一步命令,如果再次收到一個IN令牌便會向控制端點中寫入數(shù)據(jù),并且根據(jù)數(shù)據(jù)長度再次寫端點直到數(shù)據(jù)發(fā)送完畢。USB的標準請求包括讀取設(shè)備描述符、配置描述符、端點描述符、設(shè)置地址、配置設(shè)備等,廠商請求由用戶自行定義。

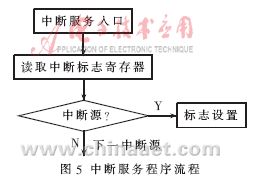

ISP1581接收到主機的數(shù)據(jù)后,將根據(jù)相應的情況設(shè)置片內(nèi)的中斷寄存器標志中斷源,然后向單片機申請中斷,中斷服務程序流程如圖5所示。單片機響應中斷后,首先讀取中斷標志寄存器并判斷中斷源,然后設(shè)置相應的標志。在用戶的發(fā)送/接收程序中,將根據(jù)相應的標志產(chǎn)生相應的動作。例如,主機發(fā)送一段數(shù)據(jù)給ISP1581,ISP1581接收、握手完畢后,設(shè)置中斷標志并申請中斷。在用戶的任務中發(fā)現(xiàn)有數(shù)據(jù)接收的標志,就可以讀出ISP1581中的數(shù)據(jù)。而ISP1581向主機發(fā)送數(shù)據(jù)時,首先是主機發(fā)送一個IN類型的令牌發(fā)起一次傳輸,如果此時ISP1581相應端點的FIFO非空,則立即發(fā)送數(shù)據(jù),然后向單片機申請中斷,響應中斷以后如果還有數(shù)據(jù)要發(fā)送,則應該向ISP1581的FIFO中寫入數(shù)據(jù),否則直接清空中斷標志即可。主機和數(shù)據(jù)采集器之間的握手配合要事先設(shè)計好。

根據(jù)輸入傳輸要求,在具體的設(shè)計中,除了主數(shù)據(jù)傳輸端點外,還配置了一個數(shù)據(jù)緩沖區(qū)為64字節(jié)的、工作于中斷傳輸方式的端點作為命令端口,負責與主機進行通信握手。如果主機想從設(shè)備讀取數(shù)據(jù),則首先發(fā)送一個讀取命令,單片機接收到該命令后,就向主數(shù)據(jù)端點的FIFO中寫入數(shù)據(jù),隨后主機發(fā)出讀數(shù)據(jù)令牌,正好有數(shù)據(jù)可以發(fā)送。通過命令端口還可以發(fā)送各種命令,控制數(shù)據(jù)采集器動作。

3 FPGA數(shù)據(jù)采集模塊設(shè)計

3.1 模塊劃分

FPGA模塊劃分為A/D接口、FIFO、單片機接口、DMA接口控制、主控制器等模塊,其中設(shè)置了一些可以單片機寫入的寄存器。A/D的采集速度,F(xiàn)IFO的空、滿、數(shù)據(jù)寫入、讀出速度都可以靈活配置。整個模塊以Verilog語言寫成,稍加修改可以同各種A/D芯片接口。整個設(shè)計在Altera公司的Cyclone系列的EP1C12中完成。在ACEX1K系列EC1K100器件上也可以實現(xiàn),工作時鐘頻率為50MHz。

為了提高系統(tǒng)的靈活性,在信號的調(diào)理、濾波模塊中使用了Lattice公司的ispPAC80可編程濾波器作為輸入濾波器,可以靈活地設(shè)定抗混疊濾波器的截止頻率,最大截至頻率可以達到750kHz,完全可以滿足一般中、高頻信號的濾波。FPGA作為A/D控制器可以同多種A/D芯片接口,本設(shè)計中使用了TI公司的10位高速A/D芯片TLC876。芯片工作于流水線方式,最高采樣速率為20MSPS。

3.2 與單片機及ISP1581的接口

FPGA在與單片機信號的接口過程中,使用了同步設(shè)計的方法。即首先對單片機的I/O信號進行采樣同步化,獲得各信號上升、下降沿的時刻,輸出同步脈沖,然后在這些時刻點處根據(jù)同步脈沖的出現(xiàn)與否來控制系統(tǒng)進行動作。這種設(shè)計的優(yōu)點是可以在設(shè)計中采用同步狀態(tài)機,以獲得較高的運行速度和穩(wěn)定的工作性能。這也是ALTERA、XILINX等公司的FPGA數(shù)字系統(tǒng)設(shè)計中所推薦使用的方法。

為了提高FPGA中的FIFO與ISP1581中的數(shù)據(jù)存儲器的數(shù)據(jù)交換速度,F(xiàn)PGA與ISP1581之間采用DMA方式進行數(shù)據(jù)交換。

ISP1581有兩種工作方式,由BUS_CONF、MODE0、MODE1三根引腳控制:

(1)如果上電時檢測到BUS_CONF引腳為低電平,則工作于分裂總線方式(Split Bus Mode)。ISP1581具有8-bit地址/數(shù)據(jù)復用總線和16-bit的DMA專用數(shù)據(jù)線。此時MODE1引腳如果為低電平,則可以將芯片的ALE/A0引腳與89X51的ALE腳直接相連,進行地址/數(shù)據(jù)總線復用;而如果MODE1為高電平,則ALE/A0腳要接其他的89X51引腳,由用戶編程將ALE/A0腳拉高/低進行地址/數(shù)據(jù)復用,而MODE0腳在這種方式下沒有使用或作為其他用途。

(2)如果上電時檢測到BUS_CONF引腳為高電平,則工作于通用處理器方式(Generic Processor Mode)。此時MODE1腳沒有使用(可接Vcc),MODE0引腳則可接低/高電平,這樣可以使芯片的讀/寫引腳分別符合Motorola/89X51微處理器的讀寫規(guī)范。所以讓ISP1581芯片工作于分裂總線方式可以方便地與8051系列單片機接口,其AD[7:0]作為數(shù)據(jù)/地址總線復用,RD、WE、ALE分別為讀、寫、地址鎖存線,DATA[15:0]作為DMA數(shù)據(jù)總線使用。

ISP1581芯片中與DMA相關(guān)的引腳有DREQ、DACK、DIOR、DIOW。DMA傳輸前必須設(shè)定工作模式、初始化DMA相關(guān)寄存器,然后對DMA命令寄存器寫入一個命令便可以啟動DMA傳輸。傳輸模式有主、從、IDE、ATA等方式。通用數(shù)據(jù)采集系統(tǒng)比較適合采用從模式,在這種模式下,單片機接收到主機發(fā)來的開始采集命令后,立即命令FPGA啟動采樣,然后命令I(lǐng)SP1581啟動DMA傳輸,ISP1581將DREQ引腳拉高,表示請求數(shù)據(jù),此時FPGA將數(shù)據(jù)準備好后,拉低DACK引腳,待準備好數(shù)據(jù)后,在DIOR線上產(chǎn)生讀脈沖,供ISP1581將數(shù)據(jù)讀入內(nèi)部FIFO。DMA也可以使用主模式,此時讀脈沖DIOR由ISP1581產(chǎn)生。DMA工作時序圖如圖6所示。

4 PC機多線程數(shù)據(jù)采集程序設(shè)計

USB的數(shù)據(jù)傳輸使用了虛擬管道的概念,可以同時接入127個設(shè)備。每個設(shè)備可以擁有若干個端點,每個端點可以跟主機組成一個連接,構(gòu)成一個通信的最小實體。在數(shù)據(jù)傳輸過程中,只要帶寬允許,主機可以同時跟幾個端點通信,因此要求在主機的應用程序中開啟多個線程進行通信。在本設(shè)計中,采用了命令端點和數(shù)據(jù)端點分開的方式。命令端點配置成中斷或批量傳輸方式,在主機應用程序中專門開啟一個線程同該端點進行通信,開啟另外一個線程進行采樣數(shù)據(jù)傳輸,而兩個傳輸之間互相不影響。用戶界面使用另外的線程,這樣在傳輸過程中,應用程序可以隨時響應用戶的命令。在具體的設(shè)計中,點擊數(shù)據(jù)采集開始命令即建立并且啟動一個采集線程。在這個無限循環(huán)的線程函數(shù)中設(shè)置了一個標志變量,如果該變量為真,則線程函數(shù)繼續(xù)運行;否則線程終止,停止采集。這樣用戶界面線程可以通過修改線程運行標志變量來控制線程的運行。采用多線程采集程序的一個問題是線程函數(shù)必須是一個全局函數(shù),不屬于任何一個類,這樣它就無法訪問類的私有成員或保護成員,解決這個問題的方法是:因為線程函數(shù)在創(chuàng)建時允許傳送一個指針參數(shù)給它,于是可以構(gòu)造一個結(jié)構(gòu)數(shù)據(jù)類型,數(shù)據(jù)成員中包含一個指向類的指針。在創(chuàng)建線程時將想要訪問的類的指針包含在一個按前述定義的結(jié)構(gòu)變量中,并將該結(jié)構(gòu)的指針作為參數(shù)傳給線程函數(shù)。這樣就可以在線程函數(shù)中定義一個類對象,并把前述的類指針賦給它,通過類指針就可以訪問該對象中的所有成員了。在本設(shè)計中采用多線程程序設(shè)計后,系統(tǒng)工作非常穩(wěn)定。

目前,國內(nèi)外的數(shù)據(jù)采集系統(tǒng)常用的接口方式有多種,如 RS232 串行口、并行口,ISA 總線、PCI總線等。這些總線接口雖各具優(yōu)點,但也都有其難以克服的缺點而被逐漸淘汰。USB接口具有連接方便、無需外接電源、即插即用、支持熱插拔、動態(tài)加載驅(qū)動程序等特有優(yōu)點,在主機和數(shù)據(jù)采集系統(tǒng)之間可以實現(xiàn)簡單、快捷、可靠的連接和通信。本設(shè)計應用ISP1581USB接口芯片與FPGA技術(shù),構(gòu)建了一個使用靈活的通用數(shù)據(jù)采集系統(tǒng)。該系統(tǒng)充分利用了PC機的大存儲量,強大的數(shù)據(jù)處理能力,高清晰的大屏幕顯示(相對于嵌入式系統(tǒng)而言),以及嵌入式系統(tǒng)的實時與靈活性。目前正在使用此平臺構(gòu)建一個在消聲室環(huán)境中針對機械振動噪聲的采集與分析系統(tǒng)。此系統(tǒng)在智能儀器以及工業(yè)自動化等眾多領(lǐng)域中必將有廣泛的應用前景。

參考文獻

[1] 蕭世文. USB2.0硬件設(shè)計[M].北京:清華大學出版社,2002.

[2] 周立功.PDIUSBD12USB固件編程與驅(qū)動開發(fā)[M].北京:北京航空航天大學出版社,2003.

[3] 張念淮. USB總線接口開發(fā)指南[M].北京:國防工業(yè)出版社,2001.

[4] Philips Semiconductors. ISP1581 programming guide[Z].2004.

[5] USB.org. Universal serial bus specification rev.2.0[Z].2006. http://www.usb.org/developers/docs/.

[6] 倪明輝. USB在FPGA控制的高速數(shù)據(jù)采集系統(tǒng)中的應用[J]. 計算機測量與控制,2006,14(2).