設計嵌入系統(tǒng)的主要挑戰(zhàn)來自于需要同時優(yōu)化眾多設計因素。這些需要優(yōu)化的設計因素包括單位成本、NRE(不可回收工程)成本、功率、尺寸、性能、靈活性、原型制造時間、產(chǎn)品上市時間、產(chǎn)品在市場生存時間、可維護性、可重配置能力、工程資源、開發(fā)和設計周期、工具、硬件/軟件劃分,以及其他許多因素。

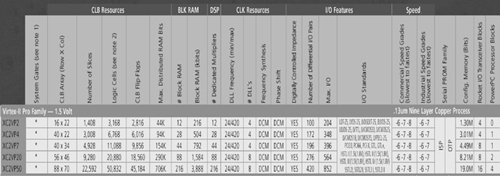

Virtex-II ProTM平臺FPGA產(chǎn)品基于高性能的Virtex-IITM結(jié)構(gòu),為嵌入式系統(tǒng)設計提供了一個極靈活的解決方案。利用Virtex-II ProTM器件,嵌入式系統(tǒng)設計人員可以在單片器件內(nèi)集成范圍廣泛的硬和軟IP核心,其中的硬件和固件具有可升級能力,從而可延長產(chǎn)品的在市場生存時間。 Virtex-II 結(jié)構(gòu)的可編程能力降低了系統(tǒng)開發(fā)時間并使單個平臺FPGA解決方案可適用于多種應用。Virtex-II ProTM FPGA使系統(tǒng)設計人員可在整個開發(fā)周期中對系統(tǒng)進行優(yōu)化,同時還為硬件和軟件設計任務折衷提供了無與倫比的協(xié)同設計靈活性。硬件/軟件系統(tǒng)劃分允許設計 人員可以控制以效率最高的方式實現(xiàn)所需要的功能。

Virtex-II ProTM平臺FPGA產(chǎn)品提供了一個可以滿足多種應用的處理、DSP和連接功能要求的平臺,這些應用包括光學網(wǎng)絡系統(tǒng)、千兆位路由器、無線蜂巢式基站、 調(diào)制解調(diào)器陣列、專業(yè)視頻廣播系統(tǒng)、測試和測量設備、生物醫(yī)療系統(tǒng)、工業(yè)控制器,以及其他許多應用。下面我們重點列出了Virtex-II ProTM平臺FPGA的主要特性和功能。

Rocket I/OTM 收發(fā)器

Virtex-II ProTM 器件提供了高達16個千兆位并串和串并收發(fā)器,可以支持不同的高速串行標準,如Gigabit Ethernet、 Fiber Channel、 Infiniband、 Serial ATA、 RapidIO、 3GIO、 Aurora、 和XAUI。其通道綁定功能可以結(jié)合多個通道提供高于3.125Gb/s的數(shù)據(jù)傳輸速率。Rocket I/OTM收發(fā)器支持物理媒體附加子層(串行化器、并串轉(zhuǎn)換器、時鐘和數(shù)據(jù)恢復、發(fā)送/接收緩沖器)和物理編碼子層(8B/10B編碼器/解碼器和彈性緩 沖器)。

PowerPCTM 405 處理器

Virtex-II ProTM 器件可提供多達4個高性能、低功耗、高速IBM PowerPCTM 405微處理器核心。在器件中集成PowerPC核心是利用IP-Immersion架構(gòu)完成的。IP-Immersion架構(gòu)允許硬核心擴散分布到平臺 FPGA結(jié)構(gòu)中的任意位置,同時還可保持與周圍邏輯陣列間的無與倫比的連接能力。利用處理器局部總線(PLB)和采用CoreConnect互連總線片上 總線架構(gòu)的外設總線,處理器可以控制和管理多種外設資源。運行在300+MHz時鐘下,能夠提供420+ Dhrystone MIPS性能的PowerPCTM 405微處理器核心提供了眾多下一代嵌入式系統(tǒng)所需要的處理能力。

18位×18位乘法器

Virtex-II ProTM 器件提供多達216個嵌入式18位×18位二進制補碼乘法器。這些嵌入式乘法器為實現(xiàn)18位× 18位帶符號乘法提供了一個快速高效的方法。一個乘法器模塊與一個SelectRAM存儲器塊相關聯(lián)。乘法器模塊針對利用塊SelectRAM一個端口的數(shù)據(jù)進行了優(yōu)化。利用這些乘法器,讀取/相乘/累加操作和DSP濾波器結(jié)構(gòu)變得異常快速和高效率。SelectRAM存儲器和乘法器資源都連接到四個交換矩陣以實現(xiàn)與通用布線資源的連接。

全局時鐘

高頻率設計需要低畸變的高級時鐘分配。在多數(shù)大密度設計中通常需要大量全局時鐘。所有的Virtex-II ProTM器件都包含16個全局時鐘緩沖器,支持16個全局時鐘區(qū)域。這些時鐘域支持進行更高水平的邏輯集成,并免除了進行復雜的時鐘樹分析的需要。16 個時鐘緩沖器還是“無毛刺”同步2:1復用器。這些復用器可以在任意時間在兩個異步(或同步)時鐘間進行切換。

數(shù)字時鐘管理器(DCM)

Virtex-II ProTM器件提供多達8個數(shù)字時鐘管理器(DCM)。每一個DCM都支持零延遲時鐘緩沖、精確相位移動和頻率合成控制。

DCM還支持對其輸出時鐘進行90°、180°和270°的相移。異常靈活的頻率合成可提供輸入時鐘頻率分數(shù)倍數(shù)或整數(shù)倍數(shù)的時鐘輸出頻率。

片上存儲器(OCM)控制器

OCM控制器在FPGA中的塊RAM和嵌入式PowerPCTM405處理器核心執(zhí)行單元間提供一個專用的接口。PowerPCTM核心上的OCM信號旨在提供對固定大小的指令和數(shù)據(jù)存儲器空間的超快速訪問。

OCM接口具有與緩存同樣的訪問時間。由于緩存為來自其它存儲器資源的緩沖代碼而保留,因此OCM減小了緩存的更新頻率。雙口塊RAM可做為OCM在處理器核心和FPGA結(jié)構(gòu)間實現(xiàn)一個高效率的共享式高速緩存存儲器接口。

Block SelectRAM (BRAM) 資源

除了分布式 Select RAM存儲器(可級聯(lián)16位×1位)以外,Virtex-II ProTM器件還包含了大量18kbit的塊狀SelectRAM(BRAM)。BRAM存儲器是真正雙口(True Dual-Port)RAM,在器件內(nèi)提供了大量快速分散的存儲器塊。BRAM存儲器的總量隨著Virtex-II Pro器件的規(guī)模而增長(高達3.8Mbit)。18Kb每塊的BRAM塊是可級聯(lián)的,從而可支持更深和更寬的存儲器設計,同時通過專門的布線資源使得時 序代價極小。

單端 SelectI/O 資源

對更復雜系統(tǒng)的需求、時鐘速率的提高和對 更小芯片到芯片間延遲的要求推動了更高性能I/O的發(fā)展。Virtex-II ProTM FPGA系列包括了高度可配置的高性能的可支持范圍廣泛的I/O標準的單端SelectI/O模塊。Virtex-II ProTM SelectI/O模塊支持下列單端I/O標準:

GTL+、HSTL (I, II, III, 和 IV)、 SSTL3 (I, 和 II)、 SSTL2 (I 和 II) 、 LVTTL、 LVCMOS(15, 18, 25, 和 33)、PCI33_3、 PCI66_3、 PCIX 和 GTL。

數(shù)字控制阻抗匹配(DCI)

DCI為發(fā)射器和接收器提供了片上端接。這樣 就不再需要電路板上大量的外部端接電阻,降低了電路板的布線困難和器件數(shù)量,同時由于消除了端頭反射(發(fā)生在端接電阻離傳輸線的端點太遠時),還改善了信 號完整性。利用DCI,端接電阻離輸出驅(qū)動器或輸入緩沖器盡可能近。因此,完全避免了端頭反射。DCI動態(tài)地調(diào)整I/O阻抗,使其等于外部參考電阻。

軟智力產(chǎn)權(quán)(IP)核心

軟IP核心為設計增加了功能和靈活性。由于其靈活 性特點,還可利用軟IP核心對產(chǎn)品進行較小的升級或?qū)υ谠O計的生命周期中段進行升級,從而延長產(chǎn)品生命周期。許多軟核心都可用于Virtex-II ProTM器件。由于具有多達450萬FPGA門,設計人員可在一塊Virtex-II ProTM FPGA器件中集成多種不同的核心。

Gigabit Ethernet MAC、10/100 Ethernet MAC、多種不同的存儲器控制器、ATM Utopia Level 2、總線仲裁器、 I2C、 UART、和SPI等就是Xilinx為Virtex-II ProTM 設計提供的IP核心的一些例子。Xilinx公司的System Generator 工具可利用CoreConnect互連總結(jié)架構(gòu)自動集成PowerPCTM和選擇并定制的軟外設。

更大的集成度和更小的尺寸

大多數(shù)印刷電路板都布滿了眾多不同的器件,如存儲器、邏輯器件、微處理器、端接匹配電阻,以及多種其他元器件。Virtex-II ProTM FPGA集成有嵌入式微處理器核心多通道Rocket I/OTM收發(fā)器,再配合豐富的軟IP核心,從而在單個芯片中即集成了上面提到的多種器件。因此,這大大提高了靈活性、性能,并降低了材料清單成本。

可綜合的軟IP核心可以為設計帶來多種功能,并提高設計的靈活性。軟IP解決了許多上市時間問題,還簡化了設計驗證。圖1示意出了一個典型千兆位以太網(wǎng) 路由器的框圖。其中Memery Controller、FPGA、PLD以及Port Controller MAC模塊可以利用Xilinx或其聯(lián)盟IP合作伙伴所提供的軟IP核心代替的數(shù)字器件。

Virtex-II ProTM的可編程特性使嵌入式系統(tǒng)設計人員可在整個開發(fā)周期中對系統(tǒng)進行優(yōu)化,并為硬件和軟件設計折衷提供了無與倫比的協(xié)同設計靈活性。軟件 /硬件劃分可提供效率最高的解決方案。以軟件方式完成硬件任務成本較低但速度慢。用硬件來完成軟件任務速度快但成本高且效率也不高。Virtex-II平 臺FPGA器件可以在軟件和硬件實施間實現(xiàn)實用的平衡,同時還可提供基于設計規(guī)范和要求的最佳解決方案。

當今的許多通信標準和協(xié)議還不成熟, 并仍處于持續(xù)的演化進行中。在很多情況下ASIC和ASSP解決方案并不適用,因為它們不能隨著標準的演化而改變。FPGA是這種情況下的理想選擇,因為 他們有可配置的結(jié)構(gòu),可以容易地實現(xiàn)、重新配置和升級(甚至可通過因特網(wǎng))新的標準和協(xié)議。通信系統(tǒng)(或任何具有多種協(xié)議的系統(tǒng))中存儲的不同協(xié)議也要求 內(nèi)置協(xié)議變換功能。Virtex-II ProTM FPGA可以非常好地完成此類重要任務。

更少的電路板器件也意味著需要更小的電路板空間,因此,系統(tǒng)成本中又可節(jié)約每層每平方英寸達0.22美元的成本。對于一塊26層的電路板,這意味著每平方英寸平均5.88美元的成本。圖2示意出圖1中可實現(xiàn)成本/器件節(jié)約的地方。

總結(jié)

Virtex-II ProTM FPGA可在高性能FPGA結(jié)構(gòu)中實現(xiàn)軟IP核心,具有嵌入式硬微處理器核心、嵌入式Rocket I/O收發(fā)器、豐富的硬件和軟件功能,并有優(yōu)化的嵌入式設計工具鏈支持。這些都使得Virtex-II ProTM FPGA可以最有效的方式解決與嵌入式系統(tǒng)設計相關的幾乎所有挑戰(zhàn)。Virtex-II ProTM FPGA可滿足產(chǎn)品上市時間、在市場生存時間、性能、成本、系統(tǒng)劃分、靈活性、可重配置能力、工程資源和更短的設計周期等所有方面的要求。