引言

通用串行總線(USB)具有快速、雙向、大批量傳輸、廉價(jià)以及可實(shí)現(xiàn)熱插拔等優(yōu)點(diǎn),Cypress公司的FX2系列芯片之一CY7C68013是最早符合USB2.0標(biāo)準(zhǔn)的微控制器,集成了符合USB2.0的收發(fā)器、串行接口引擎(SIE)、增強(qiáng)型8051內(nèi)核以及可編程的外圍接口,實(shí)現(xiàn)基于USB2.0的接口數(shù)據(jù)通信,CY7C68013可配置成3種不同的接口模式;Ports(端口模式)、GPIF Master(可編程接口模式)和Slave FIFO(主從模式),其中,后兩種模式利用其內(nèi)部集成的可以獨(dú)立于微處理器而自動(dòng)處理USB事務(wù)的硬件(USB核),數(shù)據(jù)的傳輸通過(guò)執(zhí)行USB本身的協(xié)議來(lái)完成,微處理器可不參與數(shù)據(jù)傳輸,從而使數(shù)據(jù)的傳輸速率大大地提高,同時(shí)也簡(jiǎn)化了固件代碼的編寫(xiě)。后兩種方式由于克服了微處理器這個(gè)帶寬"瓶頸",因而廣泛應(yīng)用于大批量的數(shù)據(jù)傳輸,如圖像、視頻等信號(hào)的采集。

而對(duì)前一種Ports(端口模式),文獻(xiàn)中介紹較少,作為一種最基本的數(shù)據(jù)傳輸方式,其數(shù)據(jù)傳輸主要由固件程序完成,需要CPU的參與,因此數(shù)據(jù)傳輸速率比較低,適用于傳輸速率要求不高的場(chǎng)合,而且由于FX2內(nèi)部集成有8051內(nèi)核,對(duì)一個(gè)剛從單片機(jī)的開(kāi)發(fā)過(guò)渡到USB開(kāi)發(fā)的工程人員來(lái)說(shuō),也不失是一種有效的數(shù)據(jù)傳輸方式,現(xiàn)以一個(gè)工程開(kāi)發(fā)的實(shí)例來(lái)詳細(xì)說(shuō)明一下在Ports模式下如何實(shí)現(xiàn)數(shù)據(jù)一雙向傳輸。

1 設(shè)計(jì)要求

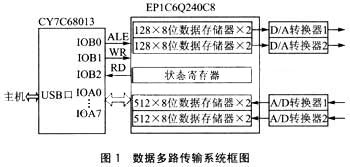

主機(jī)通過(guò)USB接口以4KB/s的速率分別向兩個(gè)通道發(fā)送數(shù)據(jù)序列,并由外設(shè)的D/A轉(zhuǎn)換器完成數(shù)據(jù)的轉(zhuǎn)換,同時(shí),由外部的兩個(gè)A/D轉(zhuǎn)換器以400KB/s的采樣率完成數(shù)據(jù)的采集,采集后的數(shù)字信號(hào)也經(jīng)USB接口傳送至主機(jī)存儲(chǔ),其中,USB接口芯片采用Cypress公司的CY7C68013,FPGA采用Altera公司的EP1C6Q240C8,圖1為其數(shù)據(jù)的多路傳輸系統(tǒng)框圖。

|

2 USB 數(shù)據(jù)多路傳輸硬件

2.1 EZ-USB FX2 CY7C68013

EZ-USB FX2 CY7C68013支持USB2.0數(shù)據(jù)傳輸,其內(nèi)部結(jié)構(gòu)及功能在其他文獻(xiàn)已有詳細(xì)的介紹,現(xiàn)針對(duì)此芯片在本電路的作用進(jìn)行簡(jiǎn)要的說(shuō)明,在設(shè)計(jì)中主要利用CY7C68013的Ports接口模式完成多路數(shù)據(jù)的傳輸,USB和FPGA之間數(shù)據(jù)和狀態(tài)的傳輸由CY7C68013的IOA接口完成,IOB接口中的IOB0-IOB2口線作為USB和FPGA之間的控制線。CY7C68013內(nèi)部的EP2端口設(shè)置為512字節(jié)雙緩沖、OUT、塊傳輸,作為主機(jī)向外設(shè)發(fā)送數(shù)據(jù)的緩沖區(qū);EP6端口設(shè)置為512字節(jié)雙緩沖,IN、塊傳輸,作為外設(shè)向數(shù)據(jù)傳送數(shù)據(jù)的緩沖區(qū)。

2.2 FPGA芯片EP1C6Q240C8

FPGA采用Altera公司的Cyclone 芯片EP1C6Q240C8。在這里FPGA的作用有3個(gè):其一,給兩路D/A轉(zhuǎn)通道各分配兩個(gè)128×8位的RAM區(qū),作為從主機(jī)向外設(shè)發(fā)送數(shù)據(jù)的緩存。其二、給兩路A/D轉(zhuǎn)換通道各分配兩個(gè)512×8位的RAM區(qū),作為從外設(shè)向主機(jī)傳送數(shù)據(jù)的緩存,由于兩路數(shù)據(jù)的傳輸和采集共用一個(gè)8位數(shù)據(jù)總線,因此,數(shù)據(jù)總線要針對(duì)不同的接收和發(fā)送來(lái)回切換,因而每個(gè)通道的兩路分別采用兩個(gè)RAM塊,起到雙緩沖作為,以防傳輸時(shí)數(shù)據(jù)"溢出"的。其三,由于數(shù)據(jù)總線要針對(duì)不同通道來(lái)回切換,控制切換的過(guò)程由狀態(tài)寄存器來(lái)完成,因此,要在FPGA內(nèi)部設(shè)置一個(gè)狀態(tài)寄存器,所設(shè)置的狀態(tài)寄存器僅包含兩位,分別標(biāo)識(shí)兩個(gè)通道的數(shù)據(jù)RAM的"滿"或"空"的狀態(tài),以確定當(dāng)前應(yīng)該為哪一個(gè)通道發(fā)送或接收數(shù)據(jù)。

3 通信協(xié)議的制定

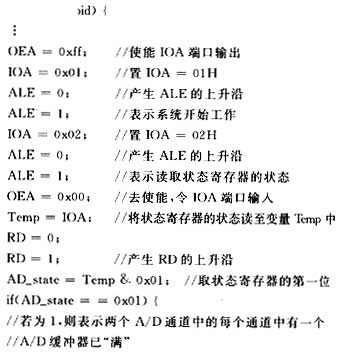

采用CY7C68013的Ports模式實(shí)現(xiàn)數(shù)據(jù)通信,與FIFO和GPIF模式不同,后兩種模式在數(shù)據(jù)傳輸方面主要由USB核完成,所需的控制信號(hào)由CY7C68013自身來(lái)提供。而對(duì)于Ports模式,控制信號(hào)沒(méi)有專(zhuān)用的口線,那么就必須用其他通用的I/O接口來(lái)完成,在此,采用IOB0-IOB2作為USB和FPGA之間的控制線,由于自定義的3條線是通用口線,沒(méi)有實(shí)際的意義,因此在USB和FPGA之間首先要制定兩者的通信協(xié)議,即給這3條口線賦以實(shí)際的功能。

ALE(IOB0):例如ALE的上升沿,通過(guò)IOA端口向FPGA傳送控制指令,例如,當(dāng)IOA=01H時(shí),表示系統(tǒng)開(kāi)始工作,A/D和D/A轉(zhuǎn)換器開(kāi)始啟動(dòng)。當(dāng)IOA=88H時(shí),表示轉(zhuǎn)換結(jié)束,F(xiàn)PGA將不再接收或發(fā)送數(shù)據(jù),當(dāng)IOA=02H時(shí),表示CY7C68013將讀取FPGA內(nèi)狀態(tài)寄存器的內(nèi)容,由讀取兩狀態(tài)標(biāo)志位的0或1,來(lái)判斷兩個(gè)通道內(nèi)的4個(gè)數(shù)據(jù)緩沖器的"滿"或"空"狀態(tài),若D/A通道的任一個(gè)數(shù)據(jù)緩沖區(qū)為"空",則由FPGA向狀態(tài)寄存器的第一個(gè)狀態(tài)標(biāo)志位內(nèi)填1;否則填0;同理,若A/D通道的任一個(gè)數(shù)據(jù)緩沖區(qū)為"滿",則由FPGA向狀態(tài)寄存器的第二個(gè)狀態(tài)標(biāo)志位內(nèi)填1;否則填0;當(dāng)IOA=03H時(shí),表示主機(jī)將通過(guò)USB向D/A通道發(fā)送轉(zhuǎn)換數(shù)據(jù),每次發(fā)送256個(gè)字節(jié),前128字節(jié)為D/A轉(zhuǎn)換的1通道,后128字節(jié)為2通道,當(dāng)IOA=04H時(shí),表示主機(jī)將要接收由A/D通道傳送來(lái)的數(shù)據(jù)。

RD(IOB1):利用RD的上升沿通過(guò)IOA端口讀取D/A轉(zhuǎn)換器轉(zhuǎn)換來(lái)的數(shù)據(jù)。

WR(IOB2):利用WR的上升沿通過(guò)IOA端口向A/D轉(zhuǎn)換器發(fā)送由主機(jī)傳送來(lái)的數(shù)據(jù)。

4 軟件的實(shí)現(xiàn)

USB與FPGA在Ports模式下數(shù)據(jù)的傳輸,由于是由CY7C68013內(nèi)部的CPU核來(lái)實(shí)現(xiàn)的,因此,對(duì)固件程序的編寫(xiě)顯得比較重要,總的來(lái)說(shuō),固件程序的編寫(xiě)有兩種方式:一是由于CY7C68013的內(nèi)部集成有增強(qiáng)型8051內(nèi)核,對(duì)熟悉8051匯編語(yǔ)言的用戶來(lái)說(shuō),可以直接利用會(huì)匯編語(yǔ)言編寫(xiě)高效的固件代碼;二是Cypress公司EZ-USB FX2系列配套有現(xiàn)成的固件程序框架函數(shù),用戶需要時(shí),只需添加相應(yīng)的用戶程序即可。當(dāng)然,用戶程序中的數(shù)據(jù)通信的實(shí)現(xiàn)也就是如何完成通信協(xié)議的過(guò)程。

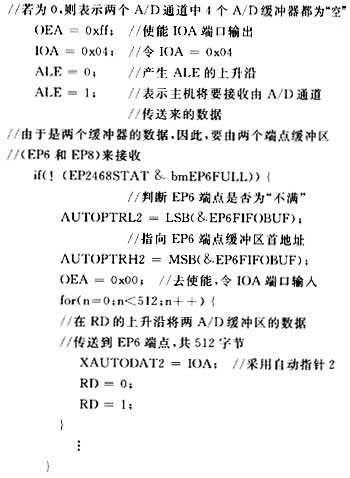

在此,采用后者來(lái)完成CY7C68013和FPGA的數(shù)據(jù)通信,實(shí)現(xiàn)數(shù)據(jù)通信功能的部分軟件代碼如下(以下代碼均可寫(xiě)在框架函數(shù)void TD_Poll(void)內(nèi)):

5 總結(jié)

CY7C68013和FPGA的數(shù)據(jù)通信中,采用基本的Ports接口模式,利用自動(dòng)指針?lè)椒ǎㄟ^(guò)數(shù)字示波器的觀察,完成1KB的傳送,大約需要750μs。與另外兩種模式相比,雖然數(shù)據(jù)傳輸?shù)乃俣容^低,但作為一種數(shù)據(jù)傳輸模式,尤其對(duì)剛從單片機(jī)開(kāi)發(fā)過(guò)渡到USB開(kāi)發(fā)的工程人員來(lái)說(shuō),也不失為一種有效的開(kāi)發(fā)方式。