FFT(快速傅里葉變換)作為數(shù)字信號(hào)處理的核心算法具有重要的研究?jī)r(jià)值,可應(yīng)用于傅里葉變換所能涉及的任何領(lǐng)域,如圖像處理、音頻編碼、頻譜分析、雷達(dá)信號(hào)脈沖壓縮等數(shù)字信號(hào)處理領(lǐng)域。FFT的鮮明特征之一是計(jì)算離散傅里葉變換(DFT)的高效算法,把計(jì)算N點(diǎn)DFT的乘法運(yùn)算量從N2次降低到N/2*log2N次。而采用FPGA實(shí)現(xiàn)FFT的緣由在于:FPGA具有并行處理、流水線處理、易編程、片上資源豐富等方面特點(diǎn),用于實(shí)現(xiàn)高速、大點(diǎn)數(shù)的FFT優(yōu)勢(shì)明顯。

本設(shè)計(jì)使用的軟件編程環(huán)境是Xilinx公司的Vivado 2018.3,筆者將從FFT IP核的創(chuàng)建,模塊文件的編寫(xiě),波形仿真等方面來(lái)具體講解FFT在Xilinx FPGA上的實(shí)現(xiàn)。

1.FFT IP核的創(chuàng)建

(1)在Vivado軟件主界面,打開(kāi)IP Catalog,在搜索框內(nèi)輸入FFT,然后找到Digital Signal Processing->Transforms->FFTs目錄下的Fast Fourier Transform,雙擊進(jìn)入配置界面。

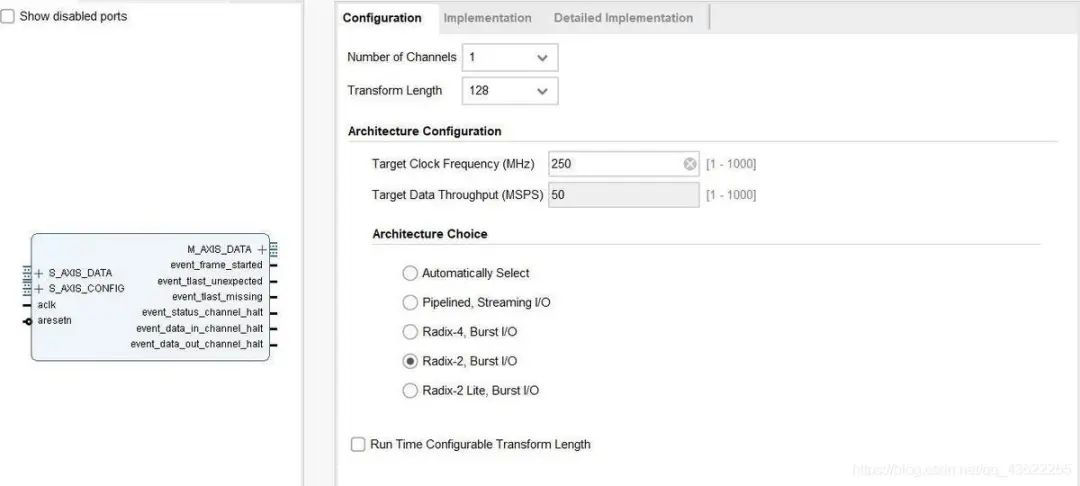

(2)進(jìn)入到配置界面,左邊是IP核的接口圖、實(shí)現(xiàn)的一些細(xì)節(jié)信息和FFT的延遲,右邊是Configuration、Implementation和Detailed Implementation三個(gè)標(biāo)簽卡。

Vivado的FFT IP核支持多通道輸入(Number of Channels)和實(shí)時(shí)更改FFT的點(diǎn)數(shù)(Run Time Configurable Transform Length)。Configuration標(biāo)簽下可設(shè)置FFT的點(diǎn)數(shù)(Transform Length)和工作時(shí)鐘(Target Clock Frequency),以及選擇一種FFT結(jié)構(gòu)。FFT的結(jié)構(gòu)包括流水線Streaming、基4 Burst、基2 Burst和輕量級(jí)基2 Burst,它們的計(jì)算速度和消耗的資源依次減少,可根據(jù)工程實(shí)際進(jìn)行選擇。

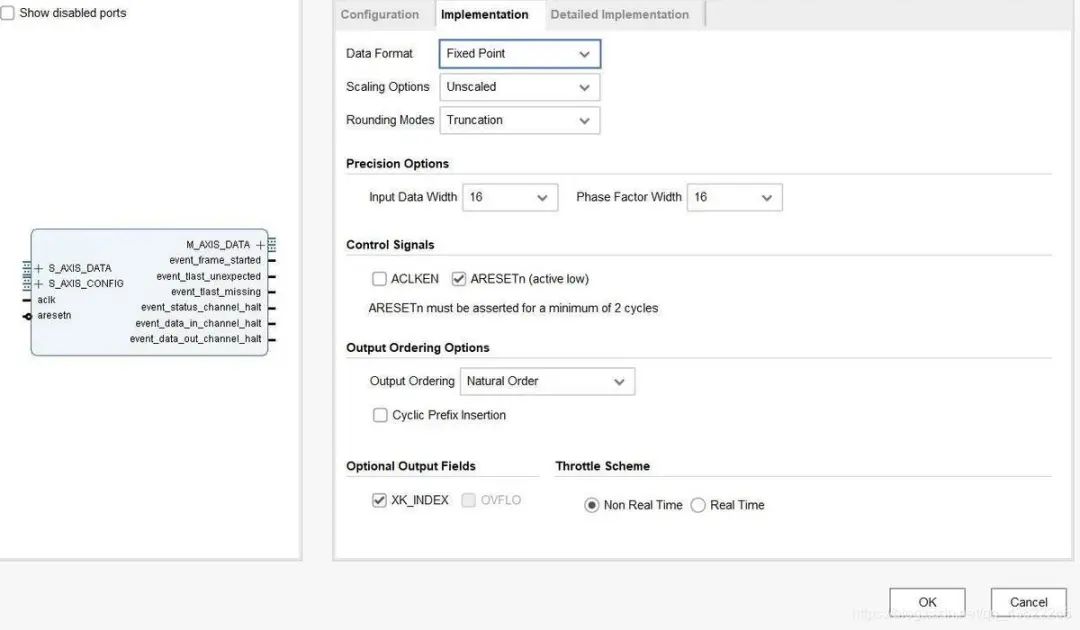

Implementation標(biāo)簽卡下可設(shè)置FFT的數(shù)據(jù)格式為定點(diǎn)Fixed Point或浮點(diǎn)Float Point;輸出截位方式選擇:不截位(Unscaled),截位(Scaled),塊浮點(diǎn)(Block Floating Point);設(shè)置輸入數(shù)據(jù)的位寬和相位因子位寬。還有一些可選的附加信號(hào),如時(shí)鐘使能(ACLKEN),復(fù)位信號(hào)(ARESETn,低有效)等。“Output Ordering”用以選擇FFT計(jì)算結(jié)果以自然順序(Nature Order)或位倒序(Bit/Digit Reversed Order)輸出。

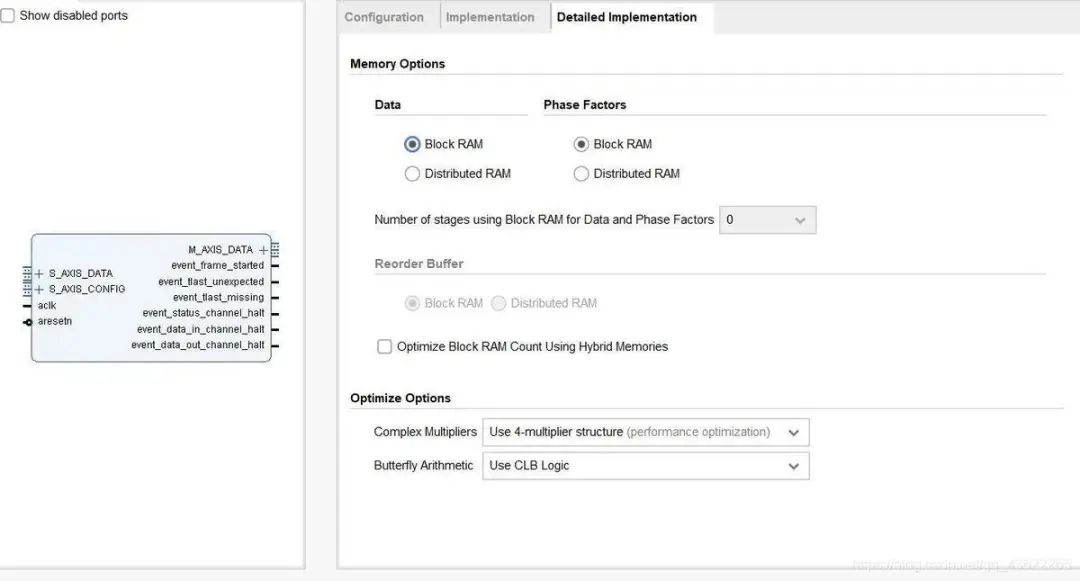

Detailed Implementation里可設(shè)置優(yōu)化方式、存儲(chǔ)的類型。存儲(chǔ)類型分為兩種:Block RAM(塊RAM)和Distributed RAM(分布式RAM);優(yōu)化方式可選擇資源最優(yōu)或者速度最優(yōu)。

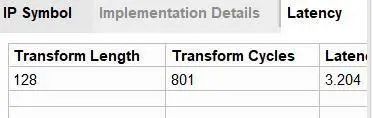

(3)配置完成后,可在Latency下看到計(jì)算fft所需的時(shí)間,可以以此衡量設(shè)計(jì)是否滿足實(shí)時(shí)處理的要求。如不滿足,可選擇性能更好的FFT結(jié)構(gòu)或選擇可以提高運(yùn)算速度的優(yōu)化選項(xiàng)

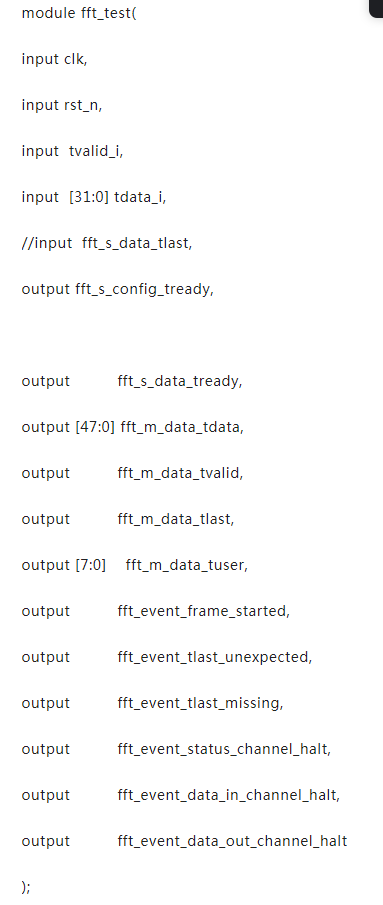

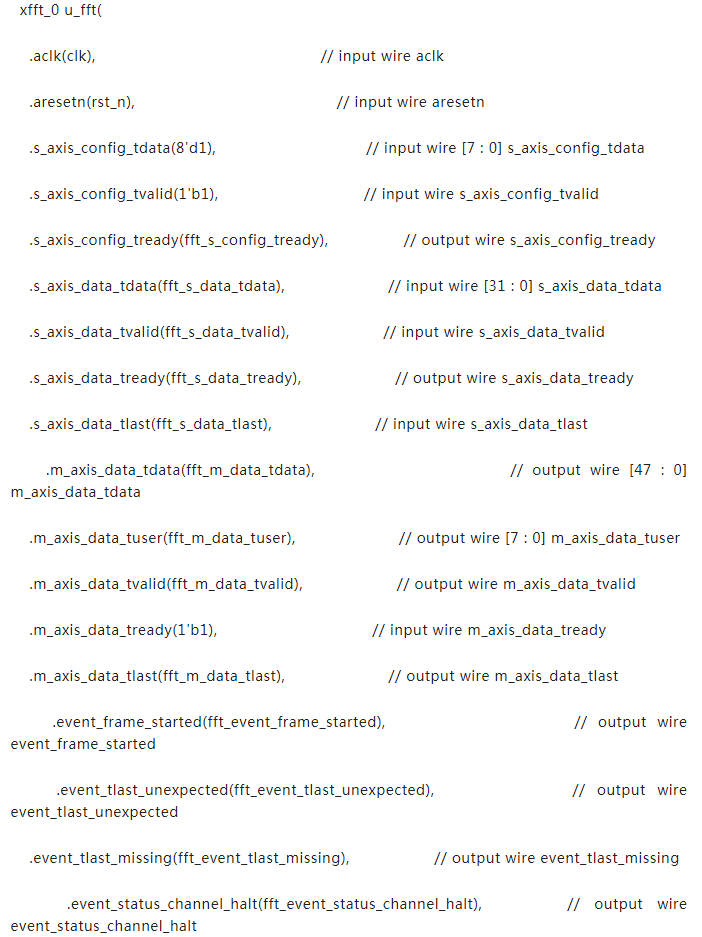

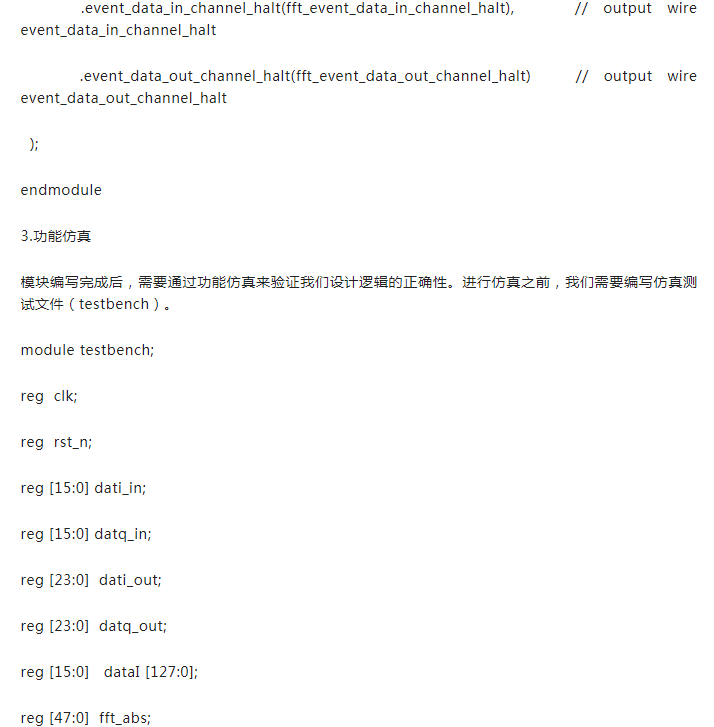

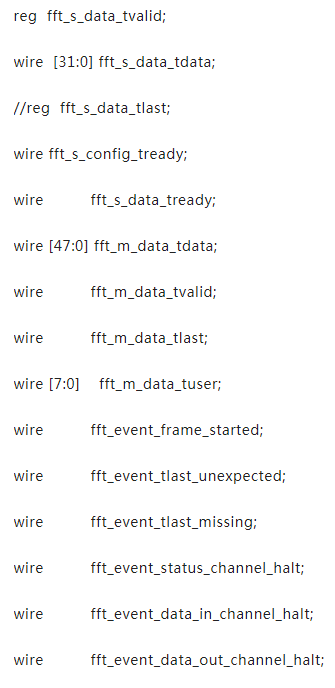

2.模塊文件的編寫(xiě)

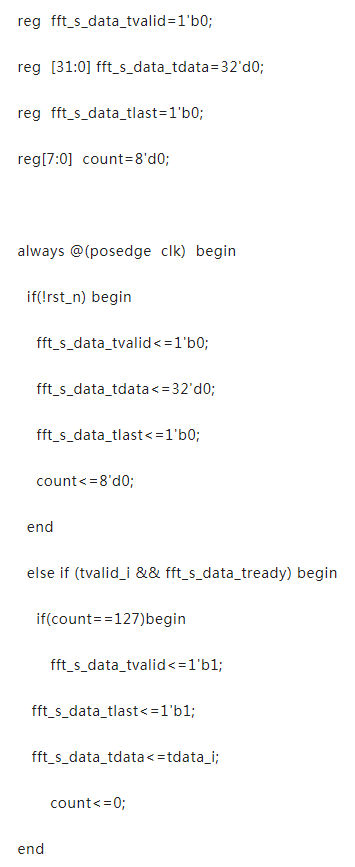

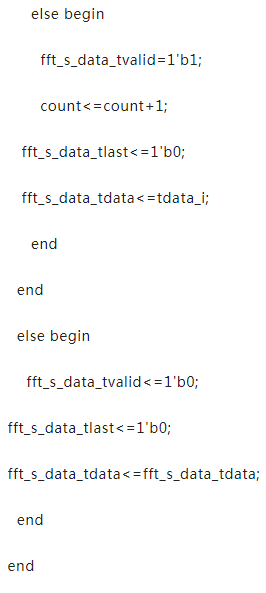

IP核工作必須要滿足一定的時(shí)序要求,所以需要將數(shù)據(jù)按照一定時(shí)序送入IP核。IP核交互是用AXI-Stream接口,關(guān)于AXI-Stream接口的時(shí)序可自行查一些相關(guān)資料,這里不做詳細(xì)介紹。簡(jiǎn)言之,AXI-Stream接口分為主機(jī)(master)和從機(jī)(slave),主機(jī)為發(fā)起端,從機(jī)為響應(yīng)端,只有ready信號(hào)和valid信號(hào)同時(shí)為高時(shí)數(shù)據(jù)才能被有效寫(xiě)入或讀出。舉個(gè)例子,主機(jī)檢測(cè)從機(jī)發(fā)出的ready信號(hào),當(dāng)為高時(shí)將valid信號(hào)拉高即可從從機(jī)讀出或向從機(jī)寫(xiě)入數(shù)據(jù)。

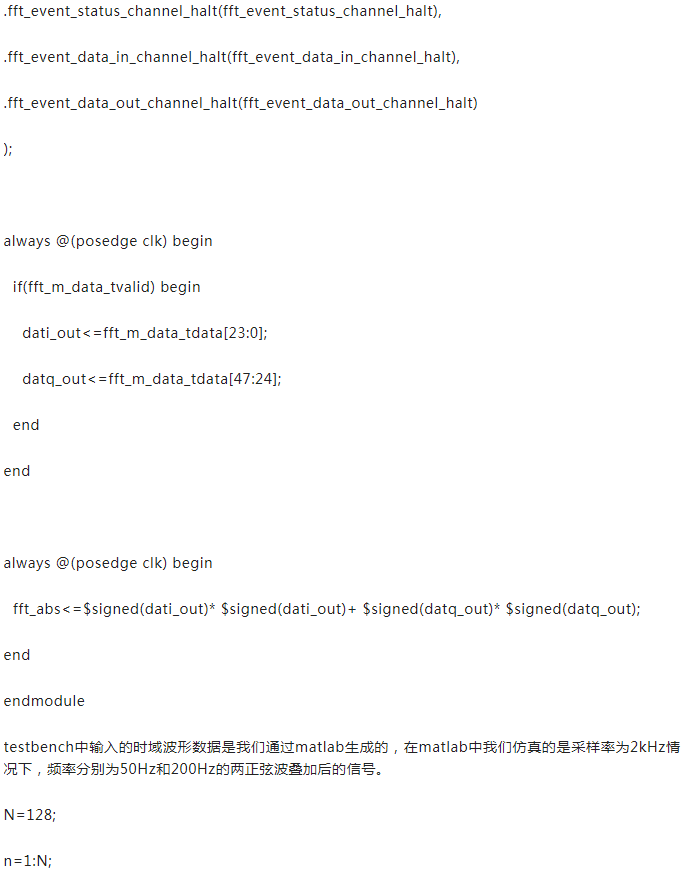

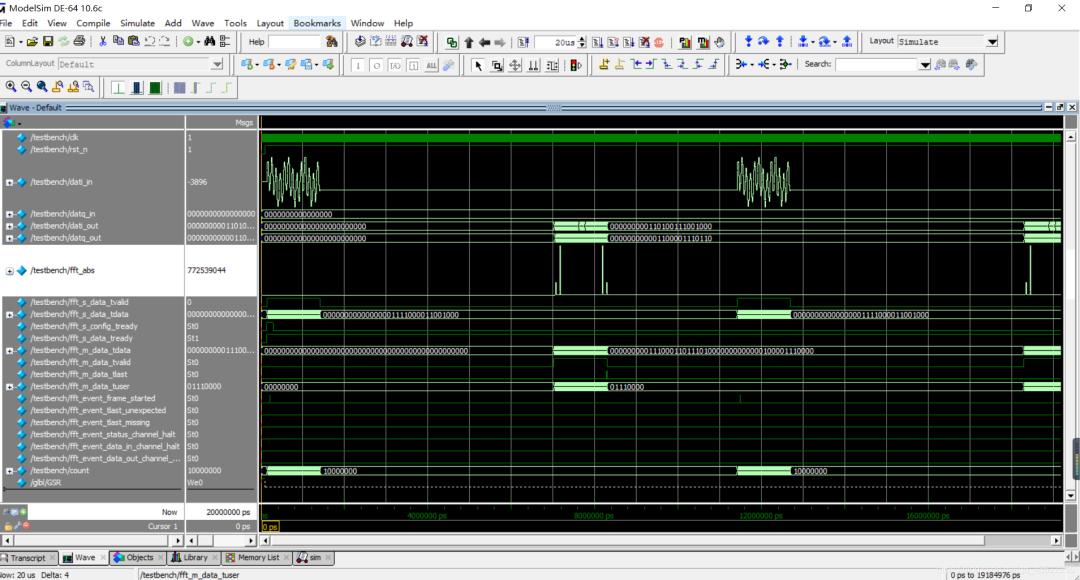

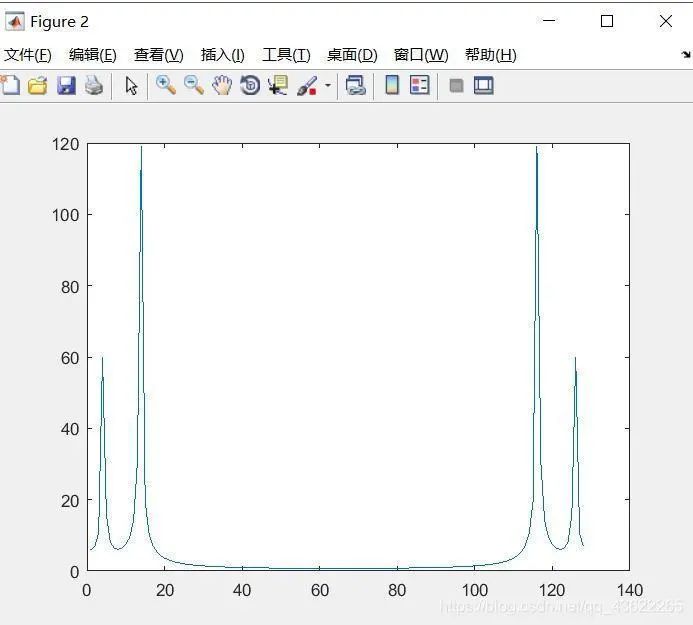

利用modelsim進(jìn)行功能仿真時(shí)我們將仿真時(shí)長(zhǎng)設(shè)置為20us。為了直觀驗(yàn)證fft是否正確,可將輸入的時(shí)域數(shù)據(jù)的實(shí)部和做完fft后信號(hào)功率值的數(shù)據(jù)格式均設(shè)置為anolog(模擬),如下圖,可以看到fft后的功率譜為兩根獨(dú)立的譜線,分別代表50Hz和200Hz兩個(gè)頻率點(diǎn),和matlab仿真結(jié)果一致。

對(duì)于該IP核更復(fù)雜的應(yīng)用,大家可以閱讀Xilinx官方提供的文檔,根據(jù)自己的實(shí)際需要進(jìn)行設(shè)計(jì)。

更多信息可以來(lái)這里獲取==>>電子技術(shù)應(yīng)用-AET<<