臺積電今天線上舉辦2021年度技術研討會,公布了未來新工藝進展,6nm、5nm、4nm、3nm、2nm都有新消息傳來。

2nm目前是各大半導體巨頭角逐的制高點,IBM甚至已經在實驗室內搞定,率先公布了2nm芯片,而除了臺積電、三星兩大代工巨頭,歐洲、日本也在野心勃勃地規(guī)劃。

不同于之前世代在相同的基礎架構上不斷演進,臺積電的2nm工藝將是真正全新設計的,號稱史上最大的飛躍,最大特點就是會首次引入納米片(nanosheet)晶體管,取代現在的FinFET結構。

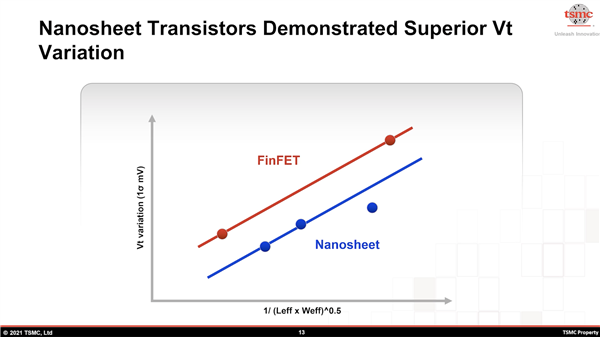

臺積電表示,納米片晶體管可以更好地控制閾值電壓(Vt)——在半導體領域,Vt是電路運行所需的最低電壓,它的任何輕微波動,都會顯著影響芯片的設計、性能,自然是越小越好。

臺積電宣稱,根據試驗,納米片晶體管可將Vt波動降低至少15%。

目前,臺積電的2nm工藝剛剛進入正式研發(fā)階段,此前消息是2023年試產、2024年量產。

本站內容除特別聲明的原創(chuàng)文章之外,轉載內容只為傳遞更多信息,并不代表本網站贊同其觀點。轉載的所有的文章、圖片、音/視頻文件等資料的版權歸版權所有權人所有。本站采用的非本站原創(chuàng)文章及圖片等內容無法一一聯(lián)系確認版權者。如涉及作品內容、版權和其它問題,請及時通過電子郵件或電話通知我們,以便迅速采取適當措施,避免給雙方造成不必要的經濟損失。聯(lián)系電話:010-82306118;郵箱:[email protected]。