1 硬件需求介紹

圖 1 卡拉 ok 硬件系統(tǒng)

1)麥克風(fēng)(microphone)

2)音頻 ADC --PCM1080 或其他音頻 ADC

3)FPGA -- 卡拉 ok 系統(tǒng)

4)音頻 DAC--PCM5102A

5)音響

6)顯示屏

2 音頻 ADC DAC 介紹

1) 音頻 adc--pcm1080

PCM1808 單端,模擬輸入 24 位,96kHz 立體聲 ADC。

性能:

– THD + N:–93 dB(典型值)

– SNR:99 dB(典型值)

–動態(tài)范圍:99 dB(典型值)

過采樣抽取濾波器:

–過采樣頻率:×64

–通帶紋波:±0.05 dB

–阻帶衰減:–65 dB

–片上高通濾波器:0.91 Hz(48 kHz)

PCM 音頻接口:

–主模式或從模式可選

–數(shù)據(jù)格式:24 位 I2S,24 位左對齊

采樣率:8 kHz–96 kHz

圖 2 PCM1080 框圖

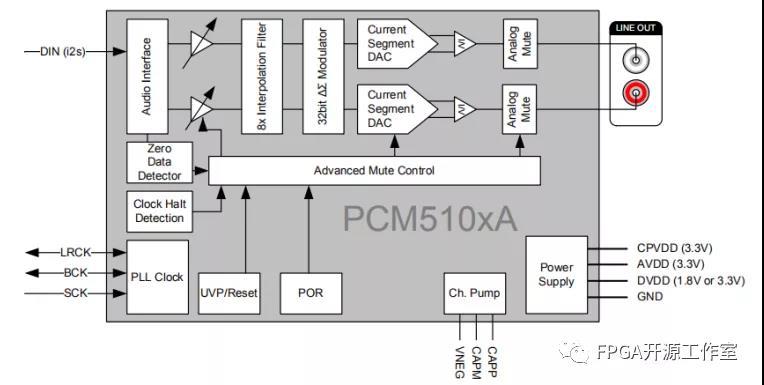

2)音頻 dac--PCM5102a:

PCM510xA 2.1 VRMS,112/106/100 dB 音頻立體聲 DAC 具有 PLL 和 32 位 384 kHz PCM 接口。

PCM510xA 的動態(tài)范圍、SNR 以及 THD 的表現(xiàn):

圖 3 PCM5102A 框圖

3 FPGA 硬件系統(tǒng)介紹

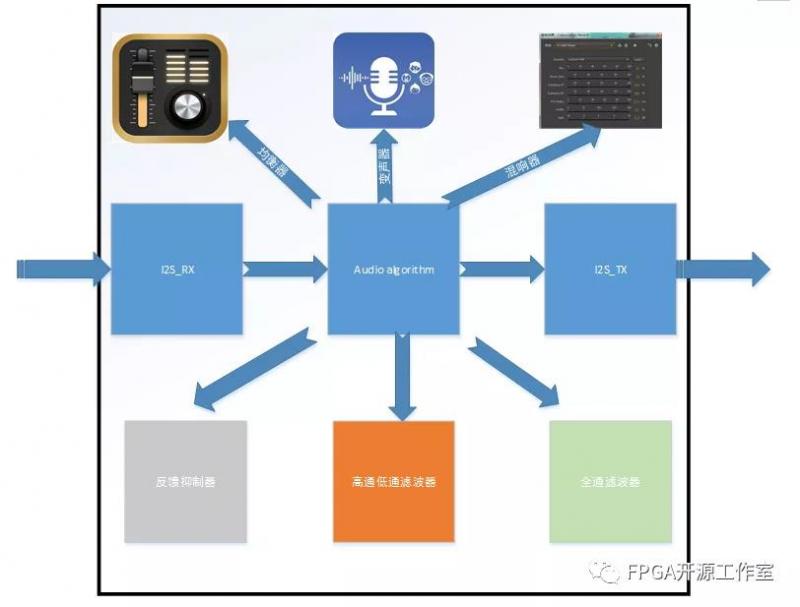

圖 4 fpga 內(nèi)部音頻算法系統(tǒng)

音頻模擬信號經(jīng)過音頻 adc 采集后轉(zhuǎn)化為數(shù)字信號通過 I2S 送入 FPGA,F(xiàn)PGA 內(nèi)部可做均衡器算法,反饋抑制算法,高低通濾波器混響回聲以及變聲的音頻處理算法。

4 i2s 的接收與發(fā)送

1)i2s 概述

I2S(Inter—IC Sound)總線, 又稱 集成電路內(nèi)置音頻總線,是飛利浦公司為數(shù)字音頻設(shè)備之間的音頻數(shù)據(jù)傳輸而制定的一種總線標(biāo)準(zhǔn),該總線專門用于音頻設(shè)備之間的數(shù)據(jù)傳輸,廣泛應(yīng)用于各種多媒體系統(tǒng)。I2S 采用了沿獨立的導(dǎo)線傳輸時鐘與數(shù)據(jù)信號的設(shè)計,通過將數(shù)據(jù)和時鐘信號分離,避免了因時差誘發(fā)的失真,為用戶節(jié)省了購買抵抗音頻抖動的專業(yè)設(shè)備的費用。

在飛利浦公司的 I2S 標(biāo)準(zhǔn)中,I2S 主要有三個信號。

1. 位時鐘 BICK(也叫串行時鐘 SCLK),即對應(yīng)數(shù)字音頻的每一位數(shù)據(jù),BCLK 都有 1 個脈沖。BCLK 的頻率=2×采樣頻率×采樣位數(shù)。

2. 幀時鐘 LRCK,(也稱 WS),用于切換左右聲道的數(shù)據(jù)。LRCK 為“1”表示正在傳輸?shù)氖怯衣暤赖臄?shù)據(jù),為“0”則表示正在傳輸?shù)氖亲舐暤赖臄?shù)據(jù)。LRCK 的頻率等于采樣頻率。

3. 串行數(shù)據(jù) SDATA,就是用二進(jìn)制補碼表示的音頻數(shù)據(jù)。

有時為了使系統(tǒng)間能夠更好地同步,還需要另外傳輸一個信號 MCLK,稱為主時鐘,也叫系統(tǒng)時鐘(Sys Clock),是采樣頻率的 256 倍或 384 倍。隨著技術(shù)的發(fā)展,在統(tǒng)一的 I2S 接口下,出現(xiàn)了多種不同的數(shù)據(jù)格式。根據(jù) SDATA 數(shù)據(jù)相對于 LRCK 和 SCLK 的位置不同,分為左對齊(較少使用)、I2S 格式(即飛利浦規(guī)定的格式)和右對齊(也叫日本格式、普通格式)。

以下是 I2S Sample rate 44.1Khz 和 48Khz 部分系列。

2) 模式

左對齊模式:SDATA 的 MSB 在 BCLK 的第一個上升獲得根據(jù) LRCK 的傳輸。

I2S 模式:SDATA 的 MSB 在 BCLK 的第二個上升獲得根據(jù) LRCK 的傳輸。

右對齊模式。