張浩1,王永斌1,付天輝1,張娜2

(1.海軍工程大學(xué) 電子工程學(xué)院,湖北 武漢 430033;2.海軍通信總站,北京 102100)

摘要:首先簡要介紹了射頻數(shù)字化短波發(fā)射機(jī)的基本原理以及AD9957芯片的主要功能,然后提出了一種利用AD9957芯片QDUC模式實(shí)現(xiàn)射頻數(shù)字化短波發(fā)射機(jī)內(nèi)部數(shù)字上變頻模塊和數(shù)/模轉(zhuǎn)換模塊的方案,對(duì)該模式下基帶數(shù)據(jù)產(chǎn)生、時(shí)鐘配置和串口編程的方法進(jìn)行詳細(xì)闡述,最后給出了AD9957在短波發(fā)射機(jī)中應(yīng)用方案的仿真結(jié)果和硬件實(shí)測結(jié)果。

關(guān)鍵詞:AD9957;QDUC模式;射頻數(shù)字化

中圖分類號(hào):TN914.1文獻(xiàn)標(biāo)識(shí)碼:ADOI: 10.19358/j.issn.1674-7720.2017.02.009

引用格式:張浩,王永斌,付天輝,等.基于AD9957實(shí)現(xiàn)射頻數(shù)字化短波發(fā)射機(jī)[J].微型機(jī)與應(yīng)用,2017,36(2):25-27.

0引言

數(shù)字化短波發(fā)射機(jī)的設(shè)計(jì)思路是盡可能讓數(shù)/模轉(zhuǎn)換器(Digital to Analog Converter,DAC)靠近天線,盡可能用數(shù)字信號(hào)處理代替?zhèn)鹘y(tǒng)模擬信號(hào)處理。隨著DSP、FPGA等硬件水平的提高,射頻數(shù)字化短波發(fā)射機(jī)已成為現(xiàn)實(shí)。本文將介紹一種能完成正交上變頻和數(shù)/模轉(zhuǎn)換的專用芯片——AD9957,并對(duì)AD9957在射頻數(shù)字化短波發(fā)射機(jī)中的應(yīng)用進(jìn)行分析研究。

1射頻數(shù)字化短波發(fā)射機(jī)原理

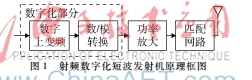

早期短波發(fā)射機(jī)都是模擬系統(tǒng),音頻輸入信號(hào)經(jīng)過SSB調(diào)制、多次混頻、濾波和放大,音頻信號(hào)才能搬移到射頻頻段。在射頻數(shù)字化短波發(fā)射機(jī)中,大部分模擬電路被數(shù)字電路代替,基帶信號(hào)直接由數(shù)字上變頻模塊轉(zhuǎn)發(fā)至短波發(fā)射頻段;DAC完成數(shù)字信號(hào)向模擬信號(hào)的轉(zhuǎn)變;模擬信號(hào)經(jīng)過功率放大器和匹配網(wǎng)絡(luò),最后由天線發(fā)射[1],如圖1所示。

2AD9957概述

AD9957芯片是ADI公司生產(chǎn)的通用數(shù)字正交上變頻器,它集成了一個(gè)高速、直接數(shù)字頻率合成器(Direct Digital Synthesizer ,DDS)、一個(gè)高性能、高速的14 位DAC、時(shí)鐘乘法器電路、數(shù)字濾波器和其他DSP功能[2]。AD9957有三種工作模式:正交數(shù)字上變頻(Quadrature Digital Up Converter,QDUC)模式、DAC內(nèi)插模式和單音模式。利用AD9957的QDUC模式,可實(shí)現(xiàn)射頻數(shù)字化短波發(fā)射機(jī)內(nèi)數(shù)字上變頻和數(shù)/模轉(zhuǎn)換部分。

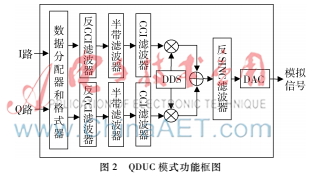

在QDUC模式中,輸入正交的兩路信號(hào):I(t)和Q(t),數(shù)據(jù)分配器和格式器對(duì)I和Q進(jìn)行解交錯(cuò)處理,以便每個(gè)樣本沿著內(nèi)部數(shù)據(jù)通路以并行方式傳輸。半帶濾波器和級(jí)聯(lián)梳狀積分(Cascad Comb Intergrator,CCI)濾波器對(duì)基帶信號(hào)進(jìn)行內(nèi)插濾波,分別使輸入信號(hào)的采樣率提高4倍和2~63倍。提高基帶信號(hào)采樣率的作用是能夠與DDS 內(nèi)核產(chǎn)生的正交(正弦和余弦)本振信號(hào)相乘并相加,從而產(chǎn)生正交上變頻數(shù)據(jù)流。反CCI濾波器和反SINC濾波器分別對(duì)CCI濾波器和DAC產(chǎn)生的通帶幅度衰減進(jìn)行補(bǔ)償。QDUC模式的功能框圖[3]如圖2所示。

3QDUC模式

3.1I/Q數(shù)據(jù)產(chǎn)生

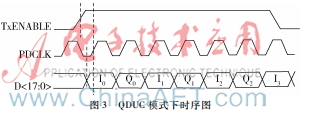

I/Q數(shù)據(jù)分別為基帶數(shù)據(jù)的同相分量和正交分量,采用18位二進(jìn)制補(bǔ)碼或偏移二進(jìn)制表示每個(gè)采樣點(diǎn)的大小。基帶數(shù)據(jù)的容量由數(shù)據(jù)時(shí)長和采樣速率共同決定。例如,發(fā)送1 s的基帶數(shù)據(jù),采樣速率為5 MHz,則需要1×5×18=90 Mbit數(shù)據(jù)容量。如果基帶數(shù)據(jù)為矩形脈沖序列,在輸入芯片數(shù)據(jù)端口前必須經(jīng)過脈沖整形。QDUC模式下數(shù)據(jù)讀取時(shí)序圖如圖3所示,TxENABLE是選通用戶數(shù)據(jù)的信號(hào),當(dāng)信號(hào)為真時(shí)允許將數(shù)據(jù)鎖存到器件中。PDCLK為并行數(shù)據(jù)時(shí)鐘,該信號(hào)頻率等于基帶數(shù)據(jù)的采樣速率。通常情況下,采用PDCLK上升沿鎖存數(shù)據(jù)至數(shù)據(jù)端口。在QDUC模式下,AD9957的并行端口上交替出現(xiàn)I和Q數(shù)據(jù)字,每個(gè)PDCLK有效沿捕捉一個(gè)18 位I或Q字。因此,PDCLK時(shí)鐘速率為:

其中,fSYSCLK是DAC的采樣速率;R是CCI濾波器的插值因子。半帶濾波器插值因子為定值4,CCI濾波器插值因子為R,則I或Q數(shù)據(jù)各自的速率為fSYSCLK/4R, 所以PDCLK時(shí)鐘速率為fSYSCLK/2R。

3.2時(shí)鐘配置

通過芯片上REF_CLK/REF_CLK輸入引腳,有兩種方式為AD9957提供參考時(shí)鐘輸入,分別是直接驅(qū)動(dòng)和晶振驅(qū)動(dòng)。

直接驅(qū)動(dòng)允許直接輸入頻率在60 MHz~1 GHz之間的信號(hào)作為芯片的系統(tǒng)時(shí)鐘。也可以輸入低頻信號(hào),由芯片內(nèi)部的鎖相環(huán)(PLL)倍頻為400 MHz~1 GHz。晶體驅(qū)動(dòng)是由晶振產(chǎn)生參考時(shí)鐘,然后倍頻至相應(yīng)的系統(tǒng)時(shí)鐘頻段。

AD9957采用了一種數(shù)模混合鎖相環(huán),即電荷泵鎖相環(huán)CPPLL(Charge Pump PhaseLock Loop),其基本結(jié)構(gòu)如圖4所示,主要由鑒頻鑒相器PFD(PhaseFrequence Detector)、電荷泵CP(Charge Pump)、低通濾波器LPF(LowPass Filter)、分頻器(Divider)和壓控振蕩器VCO(Voltage Control Oscillator)組成[4]。

LPF采用三階環(huán)路濾波器[5],如圖5所示。

圖5三階無源環(huán)路濾波器

其中R2為1 kΩ,C3為1.1 pF,其余參數(shù)根據(jù)設(shè)計(jì)需要在芯片外圍焊接,計(jì)算公式如下:

其中,KD為電荷泵電流值; KV為VCO增益; N為反饋分配系數(shù);φ為相位余量; fOL為開環(huán)帶寬。

在硬件測試中,取KD=287 μA,KV=500 MHz/V,N=20,fOL=1.2 MHz,φ=45°。計(jì)算得出,R1為1 211 Ω,C1為300 pF,C2為46 pF。

3.3串口編程

AD9957串行 I/O端口兼容了包括 Motorola 6905/11 SPI 和 Intel 8051 SSR 協(xié)議在內(nèi)的大多數(shù)同步傳輸格式[2]。

串行通信周期可分為兩個(gè)階段。第一個(gè)是指令階段,將要訪問的寄存器地址字節(jié)寫入 AD9957,并定義第二階段進(jìn)行寫入或者讀取。第二階段為寫入周期或者讀取周期,分別指從串行端口控制器向串行端口緩沖器傳輸數(shù)據(jù)和從有效寄存器讀取數(shù)據(jù)。寫入周期結(jié)束后,編程數(shù)據(jù)駐留在串行端口緩沖器中,處于無效狀態(tài)。I/O_UPDATE 將串行端口緩沖器中的數(shù)據(jù)傳輸?shù)接行Ъ拇嫫鳌?duì)于讀取周期,不需要I/O_UPDATE,數(shù)據(jù)在時(shí)鐘下降沿輸出。

此外,AD9957支持 MSB 優(yōu)先或 LSB 優(yōu)先傳輸格式。串行接口端口可以配置為單腳輸入/輸出(SDIO)或者雙腳分別輸入和輸出(SDIP和SDO);I/O復(fù)位(I/O_RESET)信號(hào)和低電平有效片選(CS)信號(hào)控制串口通信是否進(jìn)行,提高了設(shè)計(jì)系統(tǒng)靈活性。

4結(jié)論

采用碼率為2 kb/s的自定義序列(1011010)作為基帶數(shù)據(jù),采用Systemview軟件搭建QDUC模式功能電路,并進(jìn)行仿真驗(yàn)證。仿真過程中,脈沖整形采用的升余弦濾波器滾降系數(shù)為0.5,200倍內(nèi)插濾波,輸出載頻25 MHz,仿真結(jié)果如圖6所示。

硬件測試結(jié)果如圖7所示,實(shí)際測試結(jié)果和仿真結(jié)果基本一致。

綜上所述,AD9957應(yīng)用于短波發(fā)射機(jī),實(shí)現(xiàn)射頻數(shù)字化,具備實(shí)際可行性。

參考文獻(xiàn)

[1] 王金龍.短波數(shù)字通信研究與實(shí)踐[M].北京:科學(xué)出版社,2012.

[2] AD9957 Data Sheet[Z].Analog Devices,Inc.2006.

[3] 劉國棟.基于AD9957的數(shù)字正交調(diào)制器設(shè)計(jì)[J]. 無線電工程,2009,39(12):59-60.

[4] 李榮榮. 鎖相環(huán)中PFD和CP的設(shè)計(jì)[D]. 南京:東南大學(xué),2014.

[5] 劉奡.寬帶環(huán)路濾波器的設(shè)計(jì)[D]. 南京:東南大學(xué),2006.