梁炳春1,孫韶媛1,李春陽1,趙海濤2

(1.東華大學(xué) 信息科學(xué)與技術(shù)學(xué)院,上海 201620;

2.華東理工大學(xué) 信息科學(xué)與工程學(xué)院,上海 200237)

摘 要: 應(yīng)用于宇航領(lǐng)域的新型元器件必須經(jīng)過嚴(yán)格的性能功能的驗(yàn)證,傳統(tǒng)的驗(yàn)證平臺(tái)是針對(duì)特定的待驗(yàn)證器件設(shè)計(jì)的,不同的器件需要設(shè)計(jì)不同的驗(yàn)證平臺(tái),使得驗(yàn)證工作周期長、成本高、可移植性差。本文介紹基于FPGA控制器設(shè)計(jì)出的新型元器件通用驗(yàn)證方法,硬件由通用驗(yàn)證平臺(tái)和功能應(yīng)用子板兩部分組成。軟件包含有上位機(jī)調(diào)試工具、命令解析模塊、通信模塊、數(shù)據(jù)智能處理模塊等。解決了新型元器件驗(yàn)證周期長、成本高、難以實(shí)時(shí)控制和智能數(shù)據(jù)分析等缺點(diǎn)。用此方法已成功對(duì)芯片JS71238進(jìn)行了性能功能的驗(yàn)證,取得了理想的驗(yàn)證效果。

關(guān)鍵詞: FPGA;新型元器件;自動(dòng)驗(yàn)證方法;通用性

0 引言

目前,我國宇航事業(yè)進(jìn)入快速發(fā)展階段,新型航天器和新一代運(yùn)載火箭對(duì)配套元器件的性能、功能、可靠性和適應(yīng)性提出了更高的要求,因此新型元器件性能的驗(yàn)證工作對(duì)確保航天事業(yè)順利快速發(fā)展起著至關(guān)重要的作用。目前,對(duì)宇航元器件的應(yīng)用驗(yàn)證的研究大多是基于系統(tǒng)工程方法上的理論研究,主要是對(duì)新型元器件驗(yàn)證的工程路線、技術(shù)體系、方法工具等提出了理論上的框架,并且大多數(shù)的實(shí)施方案是面向特定的被測元器件設(shè)計(jì)出一套專用的驗(yàn)證設(shè)備,這樣就造成了驗(yàn)證工作成本高、周期長、可移植性差[1]的問題。針對(duì)這些不足,基于國內(nèi)外對(duì)宇航元器件應(yīng)用驗(yàn)證的研究及工程實(shí)踐,本文設(shè)計(jì)出一種通用性強(qiáng)、應(yīng)用范圍廣、自動(dòng)化程度高、功能齊全的元器件應(yīng)用驗(yàn)證平臺(tái)和方法,使宇航元器件的驗(yàn)證工作變得極為智能、便捷、高效、準(zhǔn)確,為我國航天工程的快速發(fā)展提供了先進(jìn)的技術(shù)方法。

1 通用應(yīng)用驗(yàn)證平臺(tái)分析

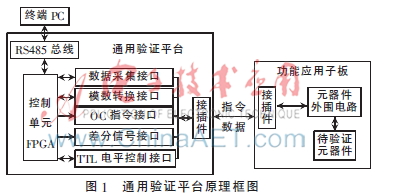

為了實(shí)現(xiàn)對(duì)不同元器件的性能功能的驗(yàn)證,設(shè)計(jì)出如圖1所示的自動(dòng)驗(yàn)證系統(tǒng),驗(yàn)證系統(tǒng)由通用驗(yàn)證平臺(tái)、功能應(yīng)用平臺(tái)和配套的測試向量等組成,控制母板的核心是一塊Xilinx的V5FX100T FPGA芯片[2],控制著驗(yàn)證平臺(tái)中的各項(xiàng)功能模塊,并負(fù)責(zé)驗(yàn)證裝置與通信終端的顯示鏈接[3]。驗(yàn)證子板為各類待驗(yàn)證器件及外圍電路,只需設(shè)計(jì)待驗(yàn)證芯片的外圍應(yīng)用電路即可搭載在該平臺(tái)上進(jìn)行驗(yàn)證工作。

控制母板是整個(gè)驗(yàn)證平臺(tái)中的核心模塊,負(fù)責(zé)數(shù)據(jù)傳輸、A/D采集、對(duì)元器件的指令操作、指令采集譯碼和測試環(huán)境的控制等重要功能[4]。母板通過RS485總線與監(jiān)控計(jì)算機(jī)連接,監(jiān)控計(jì)算機(jī)通過RS485發(fā)送指令,控制母板通過通信接口發(fā)送檢測的數(shù)據(jù)。OC指令發(fā)送用于控制驗(yàn)證子板的被驗(yàn)證元器件和外圍電路器件。D/A輸出用于對(duì)某些特定要求的電壓源輸入的精確控制。A/D采集被驗(yàn)證元器件的電壓值、溫度量和電流檢測電阻的電壓值。通過FPGA對(duì)采集到的信息數(shù)據(jù)進(jìn)行緩存和封裝,對(duì)接收到的指令進(jìn)行譯碼,發(fā)送控制信號(hào)和地址數(shù)據(jù)[5]。

2 基于通用驗(yàn)證平臺(tái)的JSR71238芯片應(yīng)用驗(yàn)證

2.1 驗(yàn)證目標(biāo)

JSR71238為16路RS422收發(fā)器芯片,包括16位驅(qū)動(dòng)器和16位接收器。驅(qū)動(dòng)器接收CMOS數(shù)字信號(hào),轉(zhuǎn)換成RS422電平信號(hào)輸出。接收器接收RS422兼容的差分輸入信號(hào),轉(zhuǎn)化成CMOS輸出信號(hào)。其功能性能驗(yàn)證主要從驅(qū)動(dòng)功能驗(yàn)證、自閉環(huán)驗(yàn)證、接收功能驗(yàn)證及器件功耗驗(yàn)證四個(gè)方面展開。

2.2 驗(yàn)證過程分析

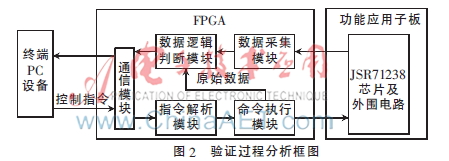

依據(jù)通用驗(yàn)證平臺(tái)提供的接口定義,在功能子板上構(gòu)建所需要的應(yīng)用電路,對(duì)測試向量進(jìn)行修改達(dá)到驗(yàn)證不同元器件的目的。驗(yàn)證過程框圖如圖2所示[6]。

通用驗(yàn)證平臺(tái)上FPGA包括通信模塊、指令解析模塊、命令執(zhí)行模塊、數(shù)據(jù)采集模塊和數(shù)據(jù)處理模塊,主要功能是接收來自終端PC設(shè)備的指令并發(fā)送指令控制子板,采集由子板反饋回來的數(shù)據(jù)進(jìn)行處理后發(fā)送給終端PC設(shè)備;終端PC設(shè)備通過上位機(jī)軟件向FPGA發(fā)送控制指令和數(shù)據(jù),監(jiān)控FPGA的狀態(tài),接收來自FPGA的數(shù)據(jù),并對(duì)數(shù)據(jù)進(jìn)行分析、診斷,圖形化顯示出測試的結(jié)果。子板通過軟排線與通用驗(yàn)證平臺(tái)相連。

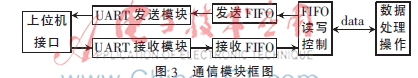

通信模塊用于上位機(jī)和FPGA的通信,是信號(hào)傳輸?shù)奈ㄒ煌ǖ馈T贔PGA中實(shí)現(xiàn)UART的功能很方便、靈活,因此采用UART來完成數(shù)據(jù)的傳輸[7]。在數(shù)據(jù)接收時(shí),接收模塊將輸入的串行數(shù)據(jù)轉(zhuǎn)換為并行數(shù)據(jù),將接收到的數(shù)據(jù)暫時(shí)存儲(chǔ)到接收FIFO中,由數(shù)據(jù)處理操作讀取數(shù)據(jù)進(jìn)行處理,執(zhí)行后再寫入到發(fā)送FIFO中,發(fā)送模塊再把數(shù)據(jù)發(fā)送到上位機(jī)軟件。可傳送數(shù)據(jù)位、數(shù)據(jù)幀和數(shù)據(jù)包等格式。通信模塊總體框圖如圖3所示[8]。

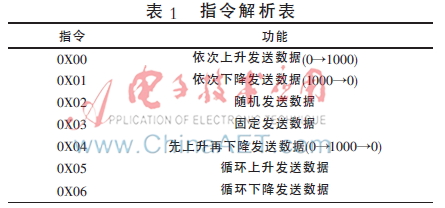

指令解析模塊主要負(fù)責(zé)指令的譯碼操作,對(duì)來自上位機(jī)的指令按照規(guī)定好的協(xié)議進(jìn)行翻譯,譯為子板可以執(zhí)行的指令[9]。指令譯碼表如表1所示。

命令執(zhí)行模塊把解析出的數(shù)據(jù)傳送給子板的接收器接口,同時(shí)把由上位機(jī)設(shè)定的原始數(shù)據(jù)發(fā)送給數(shù)據(jù)邏輯判斷模塊,作為參考數(shù)據(jù),對(duì)子板上的元器件對(duì)應(yīng)功能進(jìn)行判定。數(shù)據(jù)采集模塊以一定的頻率采集由子板上的元器件發(fā)送出的數(shù)據(jù),送給數(shù)據(jù)邏輯判斷模塊來進(jìn)行分析、比較。

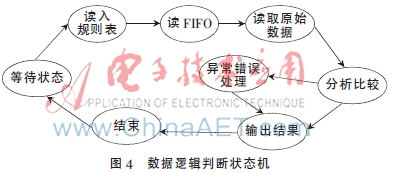

數(shù)據(jù)的邏輯判斷模塊按照一定的算法對(duì)采集回來的數(shù)據(jù)與原始數(shù)據(jù)進(jìn)行比較,根據(jù)比較的結(jié)果分析出待驗(yàn)證芯片的功能性能[10],運(yùn)算的狀態(tài)機(jī)如圖4所示。

3 實(shí)驗(yàn)結(jié)果

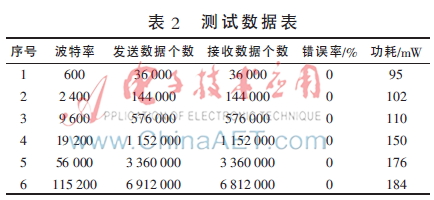

測試JSR71238在不同的波特率下的通信性能,在 1 min的時(shí)間內(nèi)連續(xù)發(fā)送數(shù)據(jù),觀察并分析數(shù)據(jù)的錯(cuò)誤率和消耗的功率,具體數(shù)據(jù)如表2所示。

通過對(duì)JSR71238芯片自閉環(huán)驗(yàn)證,其驅(qū)動(dòng)功能和接收功能均達(dá)到技術(shù)指標(biāo),其功耗也在元器件允許范圍內(nèi),在自動(dòng)驗(yàn)證平臺(tái)上完成了新型元器件的驗(yàn)證工作。

4 結(jié)論

該驗(yàn)證方法具有通用性和智能性,可以對(duì)不同的驗(yàn)證目標(biāo)提供不同類型的信號(hào)接口,可以對(duì)數(shù)據(jù)進(jìn)行自動(dòng)比對(duì)、診斷和修正,分析結(jié)果以圖形化的界面顯示出來,更直觀清晰,可以搭載不同的驗(yàn)證元器件子板,具有通用性。以上都是在不改變驗(yàn)證平臺(tái)硬件條件的情況下實(shí)現(xiàn)的,若要驗(yàn)證不同的元器件只需要設(shè)計(jì)對(duì)應(yīng)的子板外圍電路和配套的測試向量,即可完成元器件驗(yàn)證工作。驗(yàn)證不同的元器件,以上的平臺(tái)可重復(fù)利用,依靠上位機(jī)的測試軟件設(shè)置即可完成測試,無需再花費(fèi)時(shí)間和成本設(shè)計(jì)出新的驗(yàn)證板,極大地提高了驗(yàn)證效率,節(jié)約了驗(yàn)證成本,加速了項(xiàng)目的研制過程。

參考文獻(xiàn)

[1] 黃麗.百萬門級(jí)專用集成電路的FPGA驗(yàn)證[D].西安:西安電子科技大學(xué),2007.

[2] Xilinx.Virtex-5 FPGA User Guide[R]. 2009.

[3] 何賓.Xilinx FPGA設(shè)計(jì)權(quán)威指南[M].北京:清華大學(xué)出版社,2012.

[4] 張凱虹.一種FPGA驗(yàn)證與測試的方法介紹[J].計(jì)算機(jī)與數(shù)學(xué)工程,2010(9):70-72.

[5] 李洪濤,朱曉華,顧陳.Verilog HDL與FPGA開發(fā)設(shè)計(jì)及應(yīng)用[M].北京:國防工業(yè)出版社,2013.

[6] COFER R C, BENJAMIN B, HARDING F. FPGA快速系統(tǒng)原型設(shè)計(jì)權(quán)威指南[M].吳厚航,姚琪,楊碧波,譯.北京:機(jī)械工業(yè)出版社,2014.

[7] 孫航.Xilinx可編程邏輯器件的高級(jí)應(yīng)用與設(shè)計(jì)技巧[M].北京:電子工業(yè)出版社,2004.

[8] 馮子陵,俞建新.RS485總線通信協(xié)議的設(shè)計(jì)與實(shí)現(xiàn)[J].計(jì)算機(jī)工程,2012(20):215-218.

[9] 廉玉平,韓燕.大規(guī)模數(shù)字集成電路中的驗(yàn)證技術(shù)及其應(yīng)用[D].杭州:浙江大學(xué),2010.

[10] 梁駿.芯片設(shè)計(jì)的驗(yàn)證技術(shù)和驗(yàn)證流程研究[D].杭州:浙江大學(xué),2004.