摘 要: 實現(xiàn)了一種基于FPGA與LabVIEW平臺的任意波形發(fā)生器。通過FPGA搭建硬件平臺,與LabVIEW上位機軟件實現(xiàn)串口通信,實時調整FPGA內部波形數(shù)據,可實現(xiàn)正弦波、方波、鋸齒波、三角波、高斯白噪聲、疊加正弦波、自定義公式等常規(guī)波形,同時也可以手動繪制任意波形,充分發(fā)揮了軟件的靈活性。通過參數(shù)的設定,可方便地設計各種復雜波形。本設計在EP4CE15F17C8芯片上實現(xiàn),與LabVIEW上位機軟件協(xié)同工作,經測試系統(tǒng)具有良好的穩(wěn)定性、靈活性。

關鍵詞: DDS;FPGA;LabVIEW

0 引言

直接數(shù)字頻率合成[1](Direct Digital Frequency Synthesis)是一種先進的波形合成技術,目前市面上有不少的DDS專用芯片,但由于大部分設計固化在芯片中,在某些場合此類專用芯片具有一定的局限性[2-3]。為了提高DDS設計的靈活性,本文設計了一種基于FPGA與LabVIEW平臺的DDS任意信號發(fā)生器。由于FPGA的可編程特性以及軟件平臺的人機交互,使得設計的靈活性得到了大幅度提高。

同時由于FPGA具有豐富的寄存器、LUT資源,因此設計所需的數(shù)字邏輯可在FPGA內部實現(xiàn),從而使得設計盡量集成到單芯片上,減小了路徑的延時,提高了系統(tǒng)的工作頻率,增大了信號發(fā)生器的分辨率[4-5]。

1 DDS設計原理

本文DDS設計方案如圖1所示。信號發(fā)生器采用相位累加的方法,通過頻率控制字K的累加實現(xiàn)相位A的控制,由于波形相位與幅值的一一對應關系,通過查表的方式可以準確輸出對應波形幅值,從而產生初步的波形信號。由于數(shù)字波形信號為一脈沖序列,需通過DA進行模數(shù)轉換以及LPF的平滑,方可得到理想的輸出波形信號。其波形變化流程如圖2所示。

由波形輸出特點可知,輸出波形的頻率fo與相位累加器的累加地址輸出數(shù)M(M=2N)、頻率累加字K以及輸入頻率fc存在特定關系。通過分析可知,M與fo成反比,K與fo成正比,fc與fo成正比。故可以推知輸出波形的頻率fo的計算公式如下:

由式(1)可知,fo的輸出范圍若需擴大,需增大fc、增大K或者減小N,而一般fc為定值,且N需要足夠大來保證最小分辨率,因此在這里需要做一個平衡,本設計選擇N為32,時鐘頻率fc為100 MHz,因此本設計的最小頻率分辨率為0.023 2 MHz。但在實際設計中,這里N采用32 bit位寬,會給設計的存儲空間帶來非常大的考驗,需要存儲的數(shù)據量多達4 GB,因此為了在保證最小分辨率的同時,減小系統(tǒng)的數(shù)據存儲量,本文采取的方式是僅取用32 bit位寬的高10位進行尋址,這樣使得內部存儲資源能夠得到大幅度的縮減,但與此同時造成的相位截斷帶來了頻譜上的雜散分量。為了消除相位截斷帶來的頻譜雜散分量的影響,本設計在相位累加器后加入了一個偽隨機序列生成器,采用偽隨機序列生成器來打破相位截斷的周期性,這樣便可以最大程度地提高輸出波形的質量。

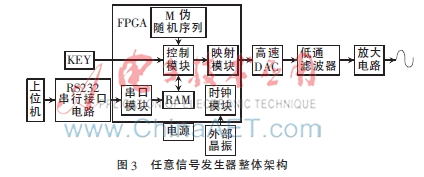

2 任意信號發(fā)生器整體架構

DDS硬件構架如圖3所示。硬件部分由FPGA及其外圍電路組成,主要實現(xiàn)單一波形的輸出,同時提供與上位機的通信接口;其處理核心采用ALTERA CYCLONE IV系列FPGA作為硬件平臺[6-7],主要實現(xiàn)功能為:接收上位機串口波形數(shù)據并實時將數(shù)據更新到雙口RAM。DDS控制模塊實時采集按鍵值,以調節(jié)頻率控制字K,頻率控制字K通過DDS控制模塊進行累加,并在雙口RAM中尋址得到波形幅值,并將該波形幅度值輸出到波形幅度映射模塊,此模塊可選擇對波形信號進行進一步的放大、縮小等操作。輸出到外部的波形數(shù)據流經高速DA數(shù)模轉換,將數(shù)字信號轉換為模擬信號,此模擬信號為一階梯信號,需通過低通濾波器對信號進行平滑,最后通過放大模塊,對信號幅度進行還原即可得到理想的輸出波形信號。

2.1 FPGA邏輯設計

FPGA硬件設計部分主要包括系統(tǒng)復位模塊、串口接收模塊、RAM接口模塊、按鍵控制模塊、M偽隨機序列發(fā)生模塊、RAM存儲模塊、幅度控制模塊。其整體FPGA設計RTL級視圖如圖4所示。

系統(tǒng)復位模塊采用異步復位同步釋放的方法,將外部異步時鐘同步到系統(tǒng)中,用于PLL鎖相環(huán)的復位操作,同時將外部復位信號與PLL輸出穩(wěn)定鎖定信號進行與運算,輸出結果再次進行異步復位同步釋放操作,使得輸出信號可以穩(wěn)定地對系統(tǒng)全局進行復位,從而很好地保證了系統(tǒng)的穩(wěn)定性。

串口接收模塊主要由波特率發(fā)生器模塊和串口接收器模塊兩部分組成。本設計波特率預置為9 600 Baud,系統(tǒng)時鐘為100 MHz。串口接收模塊負責接收上位機的串口數(shù)據流,并將串行數(shù)據流轉換為并行數(shù)據。

RAM接口模塊主要完成將串口接收模塊接收的1 024 B數(shù)據寫入到雙口RAM中。寫入完畢后,將寫信號置0釋放,便于后續(xù)讀操作。寫入地址與讀寫地址均采用內部累加器自動累加尋址。同時設定寫操作優(yōu)先級高于讀操作。

按鍵檢測模塊主要完成外部按鍵信號的檢測,從而改變輸出波形的頻率、相位以及幅度。為了增大頻率分辨率,減小數(shù)據存儲容量,將32位的相位累加器截取其高10位進行尋址,給輸出波形帶來了雜散分量,即相位截斷誤差。而相位截斷誤差主要是由于輸出波形為一周期性的階梯波,因此可通過一個M偽隨機序列來打破這種周期性,抑制相位截斷所帶來的誤差。本設計將抖動注入在相位累加器之后。

M偽隨機序列發(fā)生模塊的生成式為:1+x+x4+x5+x12,通過一個線性反饋移位寄存器可以方便地實現(xiàn)該偽隨機序列。如圖5所示,該M偽隨機序列發(fā)生模塊在全局時鐘的控制下即可產生出0、1的M偽隨機序列,通過數(shù)據線dataout將隨機序列值傳遞到按鍵控制模塊的相位累加器,以達到抑制相位截斷帶來的誤差。

RAM存儲模塊由8×1 024 bit的雙口RAM組成,可完整存儲一個周期的波形數(shù)據,波形幅度為127。

2.2 LabVIEW上位機設計

本設計使用LabVIEW 8.6開發(fā)了一個任意波形發(fā)生器的上位機軟件,在該軟件操作界面上可以選擇輸出波形的種類和參數(shù),也可以手動繪制任意波形,其軟件界面如圖6所示。

任意信號發(fā)生器軟件界面由LabVIEW的前面板和后面板構成,在前面板中主要由一些組件構成,如按鍵組件、文本輸入組件、顯示組件等。前面板的顯示部分在手動繪制模式下為波形繪制區(qū)域,繪制過程中該組件右下角可提示鼠標所在坐標以及指示燈提示。在正弦波、方波、鋸齒波、三角波、高斯白噪聲、疊加正弦波、自定義公式等常規(guī)波形模式下,該顯示組件僅發(fā)揮顯示功能。面板下方有一些文本輸入組件,這些組件可以用來調節(jié)波形的頻率、幅度、相位以及占空比等波形相關參數(shù),方便靈活地設計各種波形信號,這里波形頻率與最終輸出頻率有關,所以默認設計為1。前面板右下方為串口通信組件,可以設定COM口、波特率、終止位數(shù)、數(shù)據位數(shù)、流控制、奇偶校驗以及發(fā)送間隔時長等相關參數(shù)。同時在設計中也對軟件的采樣點數(shù)進行了設置,由于本設計采用1 024 B存儲空間,故這里默認設置為1 024,實際使用中也可根據實際情況進行設置。

在設計前面板的同時,也需要對其后面板進行設計,前面板僅作為一個友好的用戶操作平臺,其操作的所有對象的數(shù)據需要在后面板上對其進行分析處理,將處理后的結果再返回到前面板顯示,因此后面板的設計尤為重要。

由前面板的設計可知,本設計的DDS任意信號發(fā)生器可以實現(xiàn)正弦波、方波、鋸齒波、三角波、高斯白噪聲、疊加正弦波、自定義公式以及任意波形繪制。在后面板設計中這些常規(guī)波形LabVIEW都提供了專門的圖形化模塊,可以直接調用產生相應的波形。這里為了能夠將這些波形以及手動繪制波形完全兼容地顯示到XY圖組件上,采用公式波形組件創(chuàng)建了一個線性遞增的采樣計數(shù),便于統(tǒng)一管理所有的波形數(shù)據。

在手動繪制波形部分,主要通過事件結構完成鼠標繪制圖形的功能,并通過各個模塊的屬性節(jié)點來傳遞各個模塊屬性值,使得圖形化編程更加易于控制。在鼠標的位置計算上通過顯示模塊XY圖的屬性節(jié)點傳遞,得到XY圖組件坐標位置的左上方坐標點,以及XY圖組件的實際長度及寬度。得到了這些數(shù)據,便可以將XY圖組件坐標原點方便地調節(jié)到XY圖組件的左側居中位置,形成一個抽象上的X軸。而Y軸則根據波形幅值的范圍,以X軸為分界點一分為二,即形成一個抽象的坐標系。這樣便可以方便地將XY圖組件中的波形數(shù)據轉換為實際的波形數(shù)據,便于串口通信組件的發(fā)送;同時也利于在手動繪制模式時,鼠標實際位置的計算。通過鼠標經過的路徑實時地將坐標顯示出來,即可完成鼠標波形繪制的功能。手動設計原理如圖7所示。

在串口通信部分采用LabVIEW集成的串口通信模塊。根據其設計流程,依次將VISA組件中的VISA串口配置模塊、VISA串口啟動模塊、VISA串口寫模塊以及VISA串口關閉模塊加入到后面板,聯(lián)通各模塊并將輸入數(shù)據按照輸入格式進行數(shù)據類型轉換,使通信暢通,即實現(xiàn)波形數(shù)據在上位機與FPGA之間的通信。

3 仿真與測試

為驗證優(yōu)化設計,在FPGA仿真階段對本設計進行了功能仿真。仿真軟件采用Mentor公司的Modlesim,通過書寫測試激勵文件,結合Quartus II的設計網表文件,共同載入Modelsim仿真環(huán)境進行仿真,得到了圖8所示的仿真時序圖,從仿真結果可以看出,經FPGA處理輸出的波形信號質量高,符合設計要求。經測試,本DDS任意信號發(fā)生器的常規(guī)波形頻率范圍為0.03 Hz~ 40 MHz,任意波形頻率范圍為0.03 Hz~20 MHz,其頻率分辨率為0.03 Hz,幅值分辨率為8 bit,幅度范圍為 -3 V~+3 V,相較于參考文獻[1],在波形輸出頻率上提升了10%,在頻率分辨率上提升了40%。由于相位雜散的影響,在鋸齒波的最高頻率處出現(xiàn)了小幅度的間隔,在方波的高低電平處存在一定的紋波,但波動控制在極小幅度范圍之內,能夠滿足一般工業(yè)應用。在幅值量化上,由于采用有限位寬的數(shù)字信號進行模擬量的量化,因此不可避免地會產生極小的量化誤差,但通過低通濾波器的處理,能夠理想地還原出原始信號,符合預期的設計目標。

設計采用RIGOL的DS1002C雙通道示波器測試儀器進行了板級測試,其具有良好的波形存儲功能,采樣率高達25 GS/s,帶寬為100 MHz。其效果如圖9、圖10所示。

4 結論

本文通過在FPGA平臺上實現(xiàn)DDS任意信號發(fā)生器的硬件平臺,采用LabVIEW設計上位機軟件與FPGA硬件平臺進行通信,實時更新波形數(shù)據,拓展了DDS任意信號發(fā)生器的波形種類,增強了其靈活性。

本設計實現(xiàn)了采用相位截斷的方法提高設計的頻率分辨率,同時又通過M偽隨機序列注入抖動,消除相位截斷誤差,提高了信號發(fā)生器的性能。經仿真驗證,證實了本設計的可行性與穩(wěn)定性。

參考文獻

[1] 萬志江.基于FPGA的DDS IP核的研究與設計[J].微電子學與計算機,2013(8):98-102.

[2] 劉偉,鐘子發(fā),葉春逢.基于FPGA+DDS的信號源設計與實現(xiàn)[J].微型機與應用,2010,29(9):18-20,24.

[3] 梁赫西,陳佑紅,鄭朝霞.基于FPGA的可配置FFT_IFFT處理器的設計與實現(xiàn)[J].電子技術應用,2012,38(3):57-59.

[4] 哈立原.基于FPGA的直接數(shù)字式頻率合成器設計[J].內蒙古大學學報,2013,44(4):409-413.

[5] LARSON D C. High speed direct digital synthesis techniques and application[J]. IEEE, 1998: 209-212.

[6] Altera Corporation. Cyclone II device handbook[EB/OL]. www.altera.com. 2005.

[7] Analog Devices. AD9740 10-Bit, 210 MSPS TxDAC D/A Converter[EB/OL].(2005-01-03).[2014-09-01]. www.analog.com.