文獻(xiàn)標(biāo)識碼: A

DOI:10.16157/j.issn.0258-7998.2015.11.014

中文引用格式: 劉博,劉欣,樊曉華,等. 一種超低靜態(tài)功耗LDO的設(shè)計[J].電子技術(shù)應(yīng)用,2015,41(11):51-53,57.

英文引用格式: Liu Bo,Liu Xin,F(xiàn)an Xiaohua,et al. An ultra-low quiescent current LDO[J].Application of Electronic Technique,2015,41(11):51-53,57.

0 引言

近年來,各種便攜式電子產(chǎn)品的普及以及功能的日益增加,對電源管理IC提出了更高的要求,如高集成度、高效率以及低成本等。在整個電源管理IC領(lǐng)域中,LDO以其電路結(jié)構(gòu)簡單、占用芯片面積小、輸出電壓相對穩(wěn)定等優(yōu)點(diǎn),牢牢占據(jù)著電源管理IC市場很大的份額。隨著電子產(chǎn)品功能的日益復(fù)雜與多樣化,消費(fèi)市場對其續(xù)航要求也在日益增高,這就要求電源具有更高的電流效率,其定義如下式所示[1]:

其中ILoad為負(fù)載電流,Iq為靜態(tài)電流。電流效率說明了LDO電路的存在對電源工作時間有一定程度的降低。由上式可知,當(dāng)負(fù)載電流很大時,電流效率主要由負(fù)載電流決定。然而,對于很多應(yīng)用來說,電路通常工作在一個低負(fù)載電流的情況下,這時靜態(tài)電流的大小直接決定了電源的工作時間。

為解決上述問題,本文設(shè)計了一種超低靜態(tài)功耗的LDO電路,其典型靜態(tài)工作電流為500 nA,這樣極大地提高了在低負(fù)載情況下整個電路的電流效率,延長了電源壽命。此外,本文還采用了一種新穎的補(bǔ)償方式,在不增加靜態(tài)電流的情況下保證LDO的穩(wěn)定性。

1 LDO電路的基本原理與設(shè)計

圖1是本文設(shè)計的LDO的基本結(jié)構(gòu)框圖,主要包括帶隙基準(zhǔn)電路(Bandgap)、誤差放大器(EA)、調(diào)整管(Pass Transistor)以及反饋電阻(R1、R2)。其中帶隙基準(zhǔn)電路為誤差放大器提供低溫漂、高精準(zhǔn)的參考電壓Vref,誤差放大器將輸出反饋電壓與參考電壓進(jìn)行比較,并放大其差值來控制調(diào)整管的導(dǎo)通狀態(tài),從而得到穩(wěn)定的輸出電壓。輸出電壓值由下式所示:

2 誤差放大器的設(shè)計

圖2給出了誤差放大器的原理圖,采用一種對稱性運(yùn)算跨導(dǎo)放大器(Operational Transconductance Amplifier,OTA),其中包括一個差分對和三個電流鏡。輸入差分對的負(fù)載是兩個相同的電流鏡,并提供了一個增益為A的電流增益。顯然由于整體電路的對稱性,在版圖設(shè)計時會有很好的匹配。M3與M4工作在線性區(qū),提高了誤差放大器的線性度[2]。其低頻增益為:

AV=gm1ARout(3)

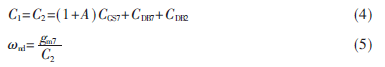

由于只有輸出節(jié)點(diǎn)是高阻,其他節(jié)點(diǎn)電阻約為1/gm左右,因此主極點(diǎn)位于輸出節(jié)點(diǎn),在節(jié)點(diǎn)1、2、3處產(chǎn)生非主極點(diǎn)。從圖中可以看出,C1與C2都是交流接地的,對于對稱的差分電路來說,它們的交流通路是相同的,因此有相同的極點(diǎn)。對于節(jié)點(diǎn)3,注意到它是位于單端輸出另一端的節(jié)點(diǎn),在這一節(jié)點(diǎn)會產(chǎn)生一個極-零點(diǎn)對,零點(diǎn)大約是極點(diǎn)的兩倍,因此對于相位裕量的影響可以忽略[3]。事實(shí)上,電路只產(chǎn)生一個非主極點(diǎn)。因此有:

可以看到次級點(diǎn)要受到A的影響,A越大,次級點(diǎn)頻率越低,這也限定了A的最大值。

對于普通采用PMOS作為導(dǎo)通管的LDO來說,通常需要一個電壓緩沖(buffer)電路來驅(qū)動導(dǎo)通管,以便將由其柵極電容產(chǎn)生的極點(diǎn)推到環(huán)路帶寬外。然而,這種方式卻不適用于低靜態(tài)電流LDO,因?yàn)閎uffer本身會消耗較大的電流。因此,可以在LDO的反饋環(huán)路中加入一個零點(diǎn)以抵消導(dǎo)通管柵極處的極點(diǎn)或者輸出電容產(chǎn)生的極點(diǎn)。如圖1所示,C1是導(dǎo)通管MPpass柵源電容與溝道電容總和,Cc是柵漏電容,gmi為誤差放大器的等效跨導(dǎo),ro為其等效輸出電阻,gmo為導(dǎo)通管MPpass的跨導(dǎo),CL與RL分別為負(fù)載電容與電阻。顯然,在導(dǎo)通管柵極與輸出端各產(chǎn)生一個極點(diǎn),其傳輸函數(shù)為:

為了補(bǔ)償次級點(diǎn),在電路中添加一個并聯(lián)在導(dǎo)通管MPpass兩端的MOS管MPpa,其寬長比相對于導(dǎo)通管的比例很小,這樣導(dǎo)通管柵極電壓通過MPpa轉(zhuǎn)化為電流注入到反饋電路中,可以得到一個零點(diǎn)ωz為:

通過適當(dāng)選取 Rf+R2/R1的值,可以對電路進(jìn)行有效的補(bǔ)償,并且不隨負(fù)載電容的變化而變化。當(dāng)該值大于1時,零點(diǎn)的頻率低于次級點(diǎn)的頻率,補(bǔ)償效果會很好,但是當(dāng)這個值過大時會影響交流信號通過導(dǎo)通管的主支路,從而導(dǎo)致輸出電壓瞬態(tài)響應(yīng)變差;當(dāng)這個值遠(yuǎn)小于1時,又會使補(bǔ)償效果變差。因此,在實(shí)際電路設(shè)計中要進(jìn)行折中。

這種補(bǔ)償方式可以解決交流補(bǔ)償,但在直流方面還存在問題。首先,MPpa會將直流電流注入到反饋電路中,并且這個電流會隨著負(fù)載的變化而變化,因此會造成輸出電壓失調(diào),并且降低了負(fù)載調(diào)整率。此外,當(dāng)負(fù)載電流很小時,gmp的值也會很小,無法為電路提供有效的環(huán)路補(bǔ)償。對于后一個問題,可以在MPpa和MPpass管的柵極間添加一個電阻,為Mpa的柵極提供一個電壓VOS,這樣即使MPpass進(jìn)入亞閾值區(qū),并聯(lián)路徑仍然會通過MPpa管提供一個有效的電流信號。為解決前一個問題,可以在MPpa源漏端加入兩個電流源,這樣通過MPpa的電流大小不會隨負(fù)載的變化而變化,同時也幾乎不會有電流流入反饋網(wǎng)絡(luò)而造成輸出電壓失調(diào)。對圖1 的電路作小信號分析可知,由于電流源的高阻特性,需要在MPpa源極接一個較大的電容Cp以保證交流信號從其柵極轉(zhuǎn)換到漏極,可以等效為一個高通濾波器,其截止頻率為gmp/Cp。若當(dāng)Cp較小時,截止頻率位于零點(diǎn)ωz的右側(cè),會造成一個增益凹陷,導(dǎo)致系統(tǒng)不穩(wěn)定。因此需要有:

如果在空載情況下,流過Mpa管的電流為1 nA,gmp=40 nA/V,gmo=200 nA/V,CL=1 F,則可得到Cp約為40 nF,這樣大的電容在片上是很難實(shí)現(xiàn)的。

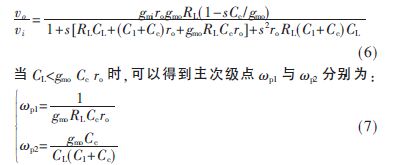

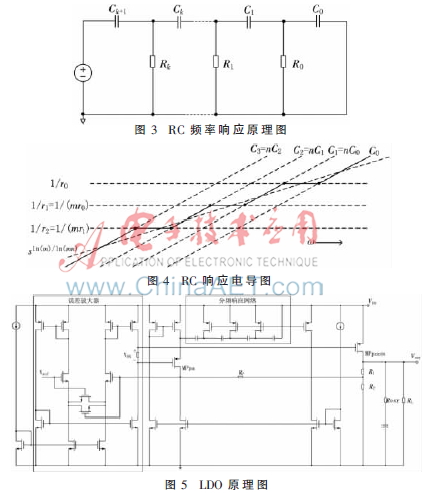

上述提到的增益凹陷來自于兩個信號,一個是MPpass漏極信號,它對于電容CL有一個1/s的頻率響應(yīng),另一個是MPpa的漏極信號,它對于電容Cp有一個s的頻率響應(yīng),這兩個信號在電路反饋端互相抵消。為了解決這個問題,本文采用了一種RC頻率響應(yīng)網(wǎng)絡(luò)的方法來代替Cp。在RC網(wǎng)絡(luò)中,Ck+1=nCk,Rk+1=mRk,其中k為該網(wǎng)絡(luò)的級數(shù),如圖3所示,電容為串聯(lián)關(guān)系,而電阻為并聯(lián)關(guān)系。圖4給出了每個元件在對數(shù)坐標(biāo)下的電導(dǎo)圖,斜線為電容的電導(dǎo)線,直線為電阻的電導(dǎo)線,它們分別為平行且等間距,電容與電阻的曲線相交。在高頻情況下,電容C0的電導(dǎo)值在串聯(lián)電容中起主導(dǎo)作用,隨著頻率降低,該值不斷降低,直到遇到電阻R0的電導(dǎo)曲線。當(dāng)頻率繼續(xù)降低時,電阻R0的電導(dǎo)值起主導(dǎo)作用并不隨頻率變化,直到遇到電容C1的電導(dǎo)曲線。以此類推可以得到該網(wǎng)絡(luò)的頻率響應(yīng)曲線,可以看出該曲線是在電容與電阻之間變換的分段線性曲線,頻率范圍為1/R0 C0到1/[n(mn)kR0 C0]。該網(wǎng)絡(luò)頻率響應(yīng)可以近似為一個sa的分頻響應(yīng)網(wǎng)絡(luò),其中a=lgm/lg(mn)[4]。隨著網(wǎng)絡(luò)級數(shù)的增加,低頻的電導(dǎo)交點(diǎn)會繼續(xù)下延。為得到更好的近似曲線,應(yīng)該使用較小的m與n和較大的k值,但這樣做會增加電路的復(fù)雜性與面積,這里采用m=n=k=2,則有a=1/2,這使得MPpa漏極的頻率響應(yīng)變?yōu)閟1/2,可以很好地避開增益凹陷。同時,按照前面的假設(shè),并設(shè)R0=1/2gmp,高通截止頻率為gmp/C0,則C0只需要大于2.5 pF即可實(shí)現(xiàn)足夠的頻率補(bǔ)償。為節(jié)省面積,采用MOS管代替網(wǎng)絡(luò)中的電阻,整體電路如圖5所示。

3 仿真結(jié)果

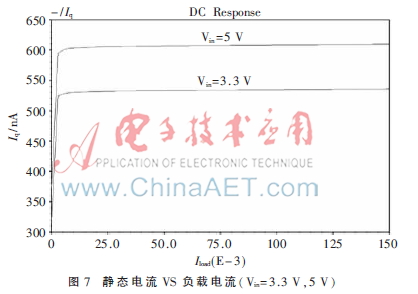

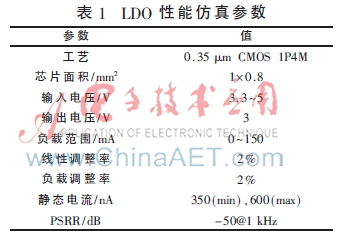

電路采用CSMC 0.35 μm工藝,使用Cadence Spectre對設(shè)計的LDO進(jìn)行仿真。圖6為電源電壓變化下LDO電路在空載與滿載下的靜態(tài)電流,圖7為負(fù)載變化下的靜態(tài)電流,表1給出了整個LDO系統(tǒng)的性能仿真參數(shù)。

4 結(jié)論

本文設(shè)計了一種超低靜態(tài)功耗的LDO電路,正常工作下最大靜態(tài)電流為600 nA,最小靜態(tài)電流為350 nA,有效地提高了電源的工作效率,顯著延長了工作時間。同時,本文采用一種新穎的分頻響應(yīng)網(wǎng)絡(luò)對電路進(jìn)行補(bǔ)償,在保證電路穩(wěn)定工作的基礎(chǔ)上盡可能降低了靜態(tài)功耗。本文設(shè)計的LDO采用0.35 μm標(biāo)準(zhǔn)CMOS工藝,輸入電壓為3.3 V~5 V,輸出電壓為3 V,最大負(fù)載電流為150 mA。

參考文獻(xiàn)

[1] RINCON-MORA G A,ALLEN P E.A low-voltage,low quiescent current,low drop-out regulator[J].IEEE J Sol StaCirc,1998,33(1):36-44.

[2] KRUMMENACHER F,JOEHL N.A 4-MHz CMOS con-tinuous-time filter with on-chip automatic tuning[J].IEEE J Sol Sta Circ,1988,23(3):750-758.

[3] KAY M.Design and analysis of an LDO voltage regulator with a PMOS power device[Z].Preliminary paper pending publication,Texas Instruments.

[4] CHAREF A,SUN H H,TSAO Y Y,et al.Fractional systemas represented by singularity function[J].IEEE J Trans.On Auto Control,1992,37(9):1465-1470.